Template Revision 2.1 - on construction Design Name always "TE Series Name" + Design name, for example "TE0720 Test Board" |

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

Important General Note: Export PDF to download, if vivado revision is changed! Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro - Use "Scroll Title" macro for pictures and table labels. Figure number must be set manually at the moment (automatically enumeration is planned by scrollPDF)

- ...

|

Table of contents

|

Overview

Zynq Design PS with Linux and simple frequency counter to measure MGT Reference CLK with Vivado HW-Manager.

Refer to http://trenz.org/te0745-info for the current online version of this manual and other available documentation.

Key Features

Notes : - Add basic key futures, which can be tested with the design

|

- PetaLinux

- SD

- ETH

- USB

- I2C

- RTC

- FMeter

- SI5338 Initialisation with FSBL

|

Revision History

Notes : - add every update file on the download

- add design changes on description

|

| Date | Vivado | Project Built | Authors | Description |

|---|

| 2018-09-2019 | 2018.2 | TE0745-test_board_noprebuilt-vivado_2018.2-build_04_20190918103545.zip

TE0745-test_board-vivado_2018.2-build_04_20190918103531.zip | John Hartfiel | - BUGFIX in TE0745-02-45-3EA board parts

| | 2018-11-26 | 2018.2 | TE0745-test_board-vivado_2018.2-build_03_20181126115131.zip

TE0745-test_board_noprebuilt-vivado_2018.2-build_03_20181126115320.zip | John Hartfiel | - Rework Board Part Files

- New assembly versions

- Rework BD Design

- add init.sh scripts

| | 2017-10-23 | 2017.2 | TE0745-test_board_noprebuilt-vivado_2017.2-build_05_20171023171903.zip

TE0745-test_board-vivado_2017.2-build_05_20171023171855.zip | John Hartfiel | |

|

Release Notes and Know Issues

Notes :- add known Design issues and general notes for the current revision

- do not delete known issue, add fixed version time stamp if issue fixed

|

| Issues | Description | Workaround | To be fixed version |

|---|

| No known issues | --- | --- | --- |

|

Requirements

Software

Notes : - list of software which was used to generate the design

|

| Software | Version | Note |

|---|

| Vivado | 2018.2 | needed | | SDK | 2018.2 | needed | | PetaLinux | 2018.2 | needed | | SI5338 Clock Builder | --- | optional |

|

Hardware

Notes : - list of software which was used to generate the design

|

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

Design supports following modules:

| Module Model | Board Part Short Name | PCB Revision Support | DDR | QSPI Flash | Others | Notes |

|---|

| TE0745-02-30-1I | 30_1i | 01,02 | 1GB | 32MB |

| *xc7z030 has lower MGT count | | TE0745-02-30-2IA | 30_2i | 01,02 | 1GB | 64MB |

| *xc7z030 has lower MGT count | | TE0745-02-35-1C | 35_1c | 01,02 | 1GB | 32MB |

|

| | TE0745-02-45-2I | 45_2i | 01,02 | 1GB | 32MB |

|

| | TE0745-02-45-2IA | 45_2i | 01,02 | 1GB | 64MB |

|

| | TE0745-02-45-1C | 45_1c | 01,02 | 1GB | 32MB |

|

| | TE0745-02-45-1CA | 45_1c | 01,02 | 1GB | 64MB |

|

| | TE0745-02-45-3EA | 45_3e | 01,02 | 1GB | 64MB |

|

|

|

Design supports following carriers:

| Carrier Model | Notes |

|---|

| TEB0745 |

|

|

Additional HW Requirements:

| Additional Hardware | Notes |

|---|

| USB Cable for JTAG/UART | Check Carrier Board and Programmer for correct typ | | XMOD Programmer | Carrier Board dependent, only if carrier has no own FTDI |

|

Content

For general structure and of the reference design, see Project Delivery - Xilinx devices

Design Sources

| Type | Location | Notes |

|---|

| Vivado | <design name>/block_design

<design name>/constraints

<design name>/ip_lib | Vivado Project will be generated by TE Scripts | | SDK/HSI | <design name>/sw_lib | Additional Software Template for SDK/HSI and apps_list.csv with settings for HSI | | PetaLinux | <design name>/os/petalinux | PetaLinux template with current configuration |

|

Additional Sources

| Type | Location | Notes |

|---|

| SI5338 | <design name>/misc/Si5338 | Si5338 Project with current PLL Configuration | | init.sh | <design name>/misc/sd | Additional Initialization Script for Linux |

|

Prebuilt

Notes : - prebuilt files

- Template Table:

File | File-Extension | Description |

|---|

| BIF-File | *.bif | File with description to generate Bin-File | | BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | | BIT-File | *.bit | FPGA (PL Part) Configuration File | | DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | Debian SD-Image | *.img | Debian Image for SD-Card | | Diverse Reports | --- | Report files in different formats | | Hardware-Platform-Specification-Files | *.hdf | Exported Vivado Hardware Specification for SDK/HSI and PetaLinux | | LabTools Project-File | *.lpr | Vivado Labtools Project File | MCS-File | *.mcs | Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only) | MMI-File | *.mmi | File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only) | | OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | | Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems | SREC-File | *.srec | Converted Software Application for MicroBlaze Processor Systems |

|

|

File | File-Extension | Description |

|---|

| BIF-File | *.bif | File with description to generate Bin-File | | BIN-File | *.bin | Flash Configuration File with Boot-Image (Zynq-FPGAs) | | BIT-File | *.bit | FPGA (PL Part) Configuration File | | DebugProbes-File | *.ltx | Definition File for Vivado/Vivado Labtools Debugging Interface | | Diverse Reports | --- | Report files in different formats | | Hardware-Platform-Specification-Files | *.hdf | Exported Vivado Hardware Specification for SDK/HSI and PetaLinux | | LabTools Project-File | *.lpr | Vivado Labtools Project File | | OS-Image | *.ub | Image with Linux Kernel (On Petalinux optional with Devicetree and RAM-Disk) | | Software-Application-File | *.elf | Software Application for Zynq or MicroBlaze Processor Systems |

|

Download

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

Reference Design is available on:

Design Flow

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

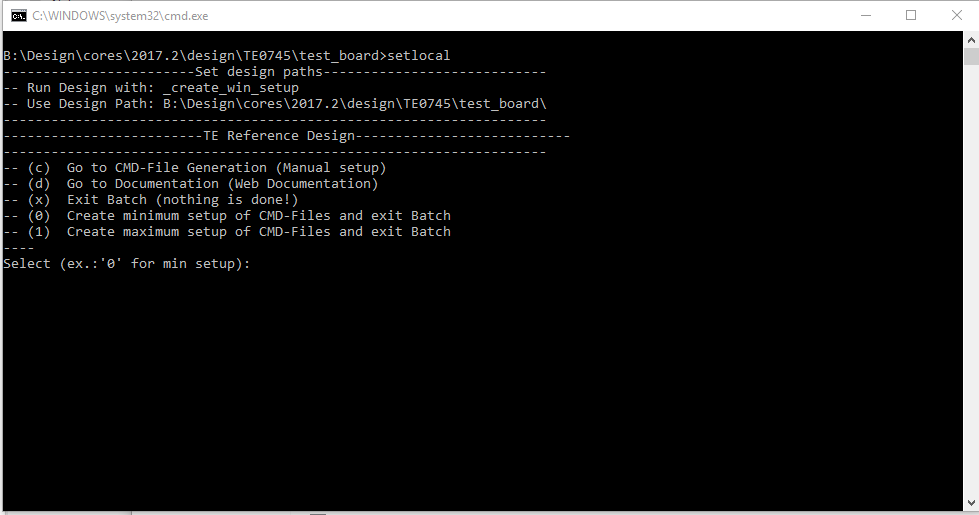

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

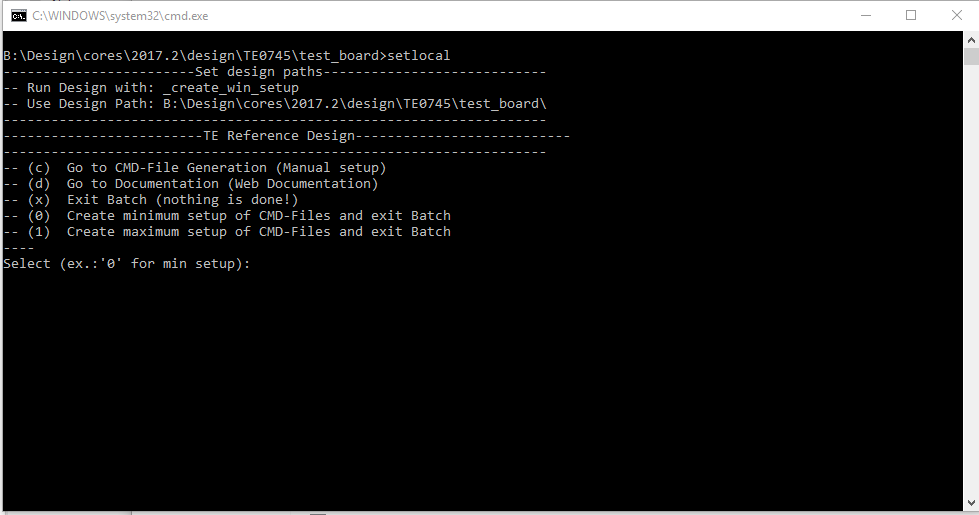

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter for minimum setup

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project

- Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Create Linux (uboot.elf and image.ub) with exported HDF

- HDF is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\default" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<short name>", if exist, otherwise "prebuilt\os\petalinux\default"

- Generate Programming Files with HSI/SDK

- Run on Vivado TCL: TE::sw_run_hsi

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_sdk

Note: See SDK Projects

Launch

Programming

Note: - Programming and Startup procedure

|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

QSPI

Optional for Boot.bin on QSPI Flash and image.ub on SD.

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0745" possible - Copy image.ub and init.sh (optional on /misc/sd) on SD-Card

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Insert SD-Card

SD

- Copy image.ub,Boot.bin and init.sh (optional on /misc/sd) on SD-Card.

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Set Boot Mode to SD-Boot.

- Depends on Carrier, see carrier TRM.

- Insert SD-Card in SD-Slot.

JTAG

Not used on this Example.

Usage

- Prepare HW like described on section Programming

- Connect UART USB (most cases same as JTAG)

- Select SD Card as Boot Mode

Note: See TRM of the Carrier and Module. - Power On PCB

Note: 1. Zynq Boot ROM loads FSBL from SD into OCM, 2. FSBL loads U-boot from SD into DDR and program PL part, 3. U-boot load Linux from SD into DDR

Linux

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:

- User Name: root

- Password: root

- You can use Linux shell now.

- I2C 0 Bus type: i2cdetect -y -r 0

- RTC check: dmesg | grep rtc

- ETH0 works with udhcpc

- USB type "lsusb" or connect USB2.0 device

- (optional) init.sh scripts: Scripts will enable SFP interface after linux booting, if file is copied on SD

Vivado HW Manager

Monitoring:

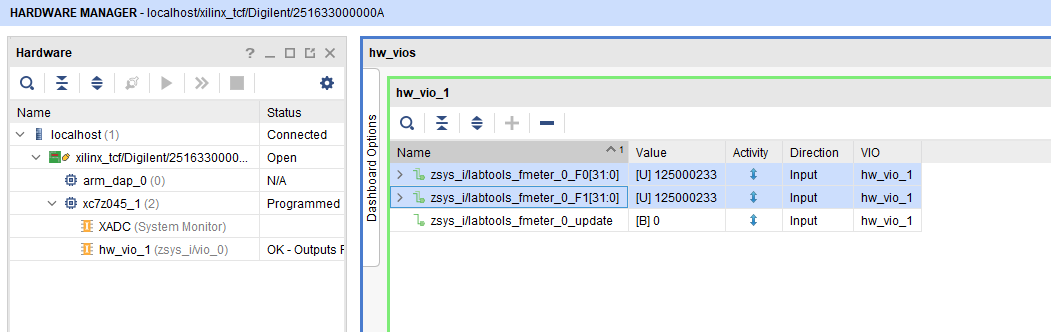

SI5338 CLKs:

- Open Vivado HW-Manager and add VIO signal to dashboard (*.ltx located on prebuilt folder).Set radix from VIO signals to unsigned integer.

Note: Frequency Counter is inaccurate and displayed unit is Hz, SI5338 CLK(0 and 3) are configured to 125MHz by default.

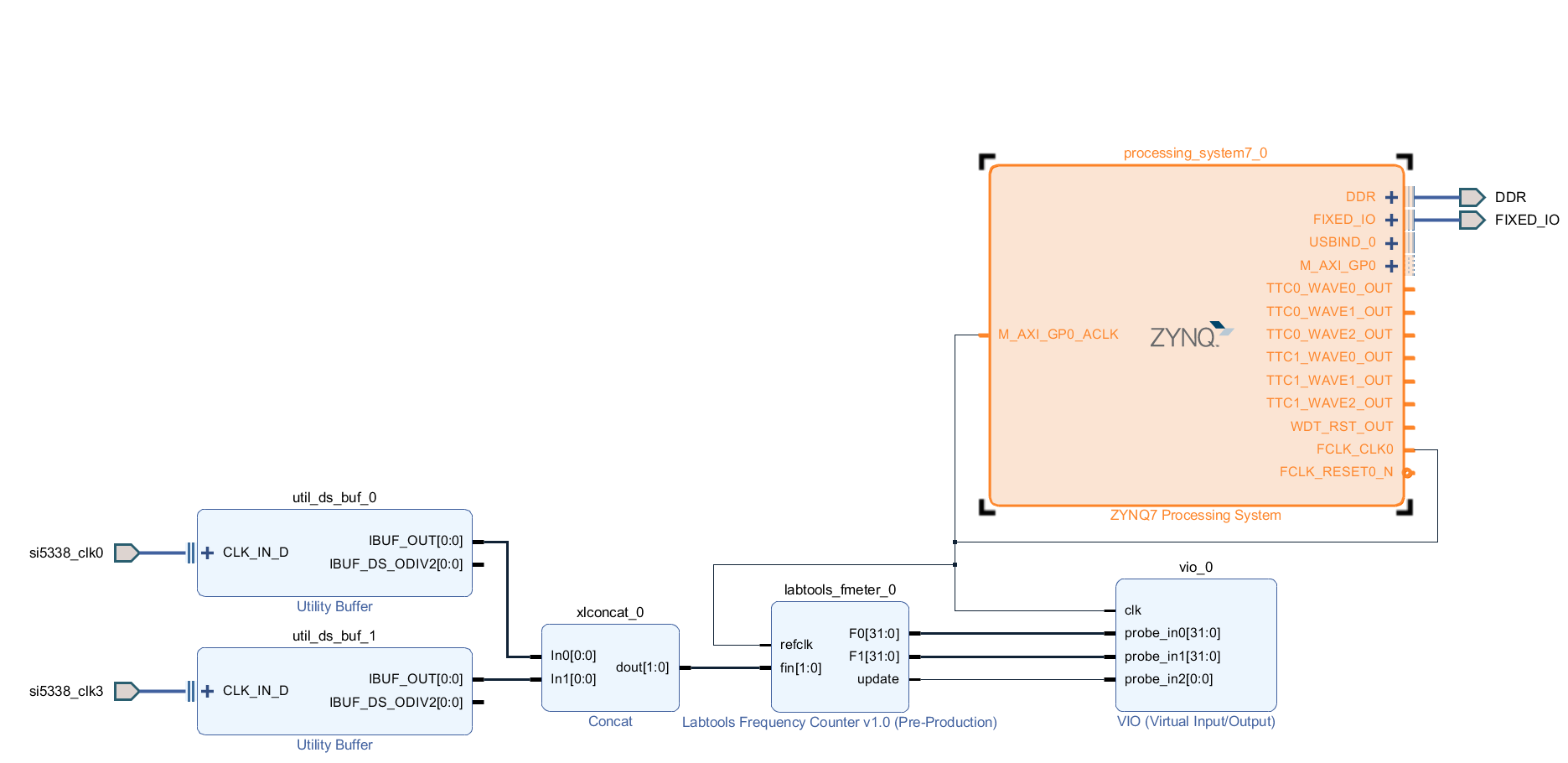

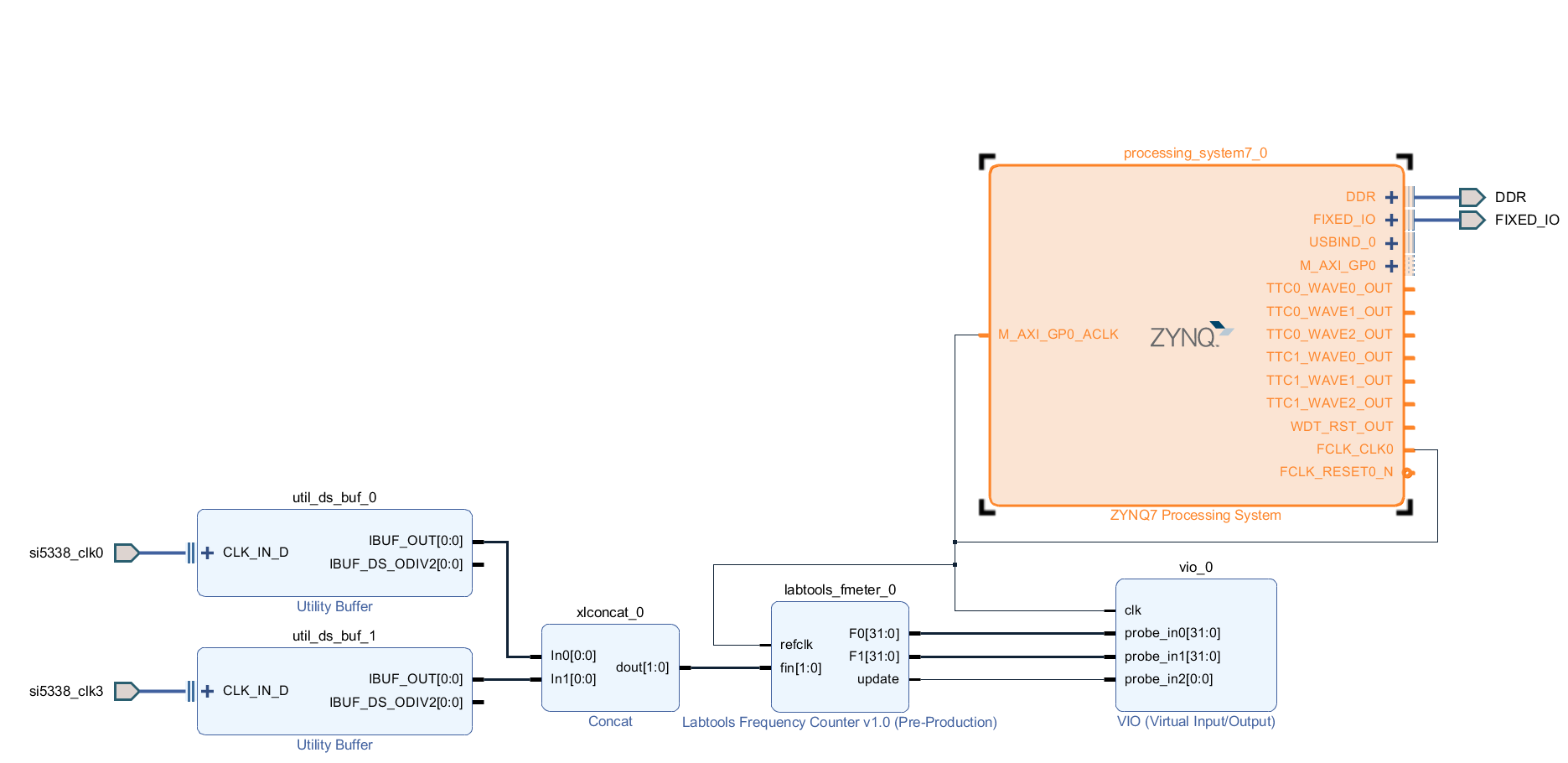

System Design - Vivado

Block Design

*clk3 is not available on the smallest SOC (xc7z030) |

PS Interfaces

Activated interfaces:

| Type | Note |

|---|

| DDR |

| | QSPI | MIO | | ETH0 | MIO | | USB0 | MIO | | SD0 | MIO | | UART0 | MIO | | I2C0 | MIO | | GPIO | MIO | | ETH0 Reset | MIO | | USB0 Reset | MIO | | I2C0 Reset | MIO | | TTC0..1 | EMIO | | SWDT0 | EMIO |

|

Constrains

Basic module constrains

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property CONFIG_VOLTAGE 1.8 [current_design]

set_property CFGBVS GND [current_design] |

Design specific constrain

No additional constrains.

Software Design - SDK/HSI

<!--

optional chapter

separate sections for different apps

--> |

For SDK project creation, follow instructions from:

SDK Projects

Application

Template location: ./sw_lib/sw_apps/

zynq_fsbl

TE modified 2018.2 FSBL

Changes:

- Si5338 Configuration see fsbl_hooks.c

- Add register_map.h, si5338.c, si5338.h

zynq_fsbl_flash

TE modified 2018.2 FSBL

Changes:

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

hello_te0745

Hello TE0745 is a Xilinx Hello World example as endless loop instead of one console output.

u-boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

Software Design - PetaLinux

For PetaLinux installation and project creation, follow instructions from:

Config

No changes.

U-Boot

No changes.

Device Tree

/include/ "system-conf.dtsi"

/ {

};

/* QSPI PHY */

&qspi {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

flash0: flash@0 {

compatible = "jedec,spi-nor";

reg = <0x0>;

#address-cells = <1>;

#size-cells = <1>;

};

};

/* ethernet */

&gem0 {

phy-handle = <&phy0>;

mdio {

#address-cells = <1>;

#size-cells = <0>;

phy0: phy@1 {

compatible = "marvell,88e1510";

device_type = "ethernet-phy";

reg = <1>;

} ;

} ;

};

/* usb */

/{

usb_phy0: usb_phy@0 {

compatible = "ulpi-phy";

#phy-cells = <0>;

reg = <0xe0002000 0x1000>;

view-port = <0x0170>;

drv-vbus;

};

};

&usb0 {

dr_mode = "host";

//dr_mode = "peripheral";

usb-phy = <&usb_phy0>;

};

/* I2C */

&i2c0 {

#address-cells = <1>;

#size-cells = <0>;

rtc0: rtc@6F {

compatible = "isl12022";

reg = <0x6F>;

};

i2cmux_SFP: i2cmux@72 {

compatible = "nxp,pca9548";

#address-cells = <1>;

#size-cells = <0>;

reg = <0x72>;

SFP@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

};

SFP@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

};

SFP@2 {

#address-cells = <1>;

#size-cells = <0>;

reg = <2>;

};

SFP@3 {

#address-cells = <1>;

#size-cells = <0>;

reg = <3>;

};

SFP@4 {

#address-cells = <1>;

#size-cells = <0>;

reg = <4>;

};

SFP@5 {

#address-cells = <1>;

#size-cells = <0>;

reg = <5>;

};

SFP@6 {

#address-cells = <1>;

#size-cells = <0>;

reg = <6>;

};

SFP@7 {

#address-cells = <1>;

#size-cells = <0>;

reg = <7>;

};

};

};

|

Kernel

Activate:

- USB_ULPI_BUS

- RTC_DRV_ISL12022

Rootfs

Activate:

Applications

startup

Script App to load init.sh from SD Card if available.

See: \os\petalinux\project-spec\meta-user\recipes-apps\startup\files

Additional Software

Note:

- Add description for other Software, for example SI CLK Builder ...

- SI5338 and SI5345 also Link to:

|

SI5338

File location <design name>/misc/Si5338/RegisterMap.txt

General documentation how you work with these project will be available on Si5338

Appx. A: Change History and Legal Notices

Document Change History

To get content of older revision got to "Change History" of this page and select older document revision number.

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

| Date | Document Revision | Authors | Description |

|---|

| | | - bugfix for TE0745-02-45-3EA

| | 2018-12-19 | v.11 | John Hartfiel | | | v.10 | John Hartfiel | - update 2018.2

- documentation style update

| | v.7 | John Hartfiel | | | 2018-02-09 | v.6 | John Hartfiel | | | 2017-09-11 | v.1 | John Hartfiel | | | -- | all | | -- |

|

Legal Notices