Page History

Template Revision 2.8 - on construction

...

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

...

| hidden | true |

|---|---|

| id | Comments |

Important General Note:

...

Export PDF to download, if vivado revision is changed!

Designate all graphics and pictures with a number and a description, Use "Scroll Title" macro

...

Figure template (note: inner scroll ignore/only only with drawIO object):

...

| anchor | Figure_xyz |

|---|---|

| title | Text |

| Scroll Ignore |

|---|

Create DrawIO object here: Attention if you copy from other page, use |

| Scroll Only |

|---|

image link to the generate DrawIO PNG file of this page. This is a workaround until scroll pdf export bug is fixed |

...

Table template:

- Layout macro can be use for landscape of large tables

- Set column width manually(can be used for small tables to fit over whole page) or leave empty (automatically)

...

| anchor | Table_xyz |

|---|---|

| title | Text |

...

| Scroll pdf ignore | ||||

|---|---|---|---|---|

Table of contents

|

Overview

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Zynq PS Design with Linux Example and Camera Demo.

Refer to http://trenz.org/te0726-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Excerpt |

|---|

|

Revision History

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

| anchor | Table_DRH |

|---|---|

| title | Design Revision History |

...

- script update

...

- update with Vivado 2019.2

...

te0726-zynqberrydemo1_noprebuilt-vivado_2018.3-build_10_20200113150027.zip

te0726-zynqberrydemo1-vivado_2018.3-build_10_20200113150016.zip

...

- update with Vivado 2018.3

...

- update petalinux with audio config

...

2018.2

...

- initial release

Release Notes and Know Issues

...

| anchor | Table_KI |

|---|---|

| title | Known Issues |

...

Requirements

Software

...

...

...

...

...

Hardware

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Basic description of TE Board Part Files is available on TE Board Part Files.

Complete List is available on <design name>/board_files/*_board_files.csv

Design supports following modules:

...

| anchor | Table_HWM |

|---|---|

| title | Hardware Modules |

...

...

Design supports following carriers:

...

| anchor | Table_HWC |

|---|---|

| title | Hardware Carrier |

...

...

...

...

...

...

...

For general structure and of the reference design, see Project Delivery - Xilinx devices

Design Sources

- the content of the zip file

...

...

...

...

...

...

...

...

...

...

Prebuilt

...

| hidden | true |

|---|---|

| id | Comments |

Notes :

...

| anchor | Table_PF |

|---|---|

| title | Prebuilt files |

...

File

...

File-Extension

...

Description

...

Debian SD-Image

...

*.img

...

Debian Image for SD-Card

...

MCS-File

...

*.mcs

...

Flash Configuration File with Boot-Image (MicroBlaze or FPGA part only)

...

MMI-File

...

*.mmi

...

File with BRAM-Location to generate MCS or BIT-File with *.elf content (MicroBlaze only)

...

SREC-File

...

*.srec

...

Converted Software Application for MicroBlaze Processor Systems

...

| anchor | Table_PF |

|---|---|

| title | Prebuilt files (only on ZIP with prebult content) |

...

File

...

File-Extension

...

Description

...

Download

Reference Design is only usable with the specified Vivado/SDK/PetaLinux/SDx version. Do never use different Versions of Xilinx Software for the same Project.

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

Reference Design is available on:

Design Flow

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Note |

|---|

Reference Design is available with and without prebuilt files. It's recommended to use TE prebuilt files for first lunch. |

Trenz Electronic provides a tcl based built environment based on Xilinx Design Flow.

See also:

The Trenz Electronic FPGA Reference Designs are TCL-script based project. Command files for execution will be generated with "_create_win_setup.cmd" on Windows OS and "_create_linux_setup.sh" on Linux OS.

TE Scripts are only needed to generate the vivado project, all other additional steps are optional and can also be executed by Xilinx Vivado/SDK GUI. For currently Scripts limitations on Win and Linux OS see: Project Delivery Currently limitations of functionality

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell:

- Press 0 and enter to start "Module Selection Guide"

- (optional Win OS) Generate Virtual Drive or use short directory for the reference design (for example x:\<design name>)

- Create Project (follow instruction of the product selection guide), settings file will be configured automatically during this process

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

Note: Select correct one, see TE Board Part Files

- (optional for manual changes) Select correct device and Xilinx install path on "design_basic_settings.cmd" and create Vivado project with "vivado_create_project_guimode.cmd"

- Create HDF and export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

Note: Script generate design and export files into \prebuilt\hardware\<short dir>. Use GUI is the same, except file export to prebuilt folder

- Run on Vivado TCL: TE::hw_build_design -export_prebuilt

- Create Linux (uboot.elf and image.ub) with exported XSA

- XSA is exported to "prebuilt\hardware\<short name>"

Note: HW Export from Vivado GUI create another path as default workspace. - Create Linux images on VM, see PetaLinux KICKstart

- Use TE Template from /os/petalinux

- For 128MB and 64MB only:Netboot Offset must be reduced manually, see 69107715

- XSA is exported to "prebuilt\hardware\<short name>"

- Add Linux files (uboot.elf and image.ub) to prebuilt folder

- "prebuilt\os\petalinux\<DDR size>" or "prebuilt\os\petalinux\<short name>"

Notes: Scripts select "prebuilt\os\petalinux\<DDR size>", if exist, otherwise "prebuilt\os\petalinux\<short name>"

- "prebuilt\os\petalinux\<DDR size>" or "prebuilt\os\petalinux\<short name>"

- Generate Programming Files with Vitis

- Run on Vivado TCL: TE::sw_run_vitis -all

Note: Scripts generate applications and bootable files, which are defined in "sw_lib\apps_list.csv" - (alternative) Start SDK with Vivado GUI or start with TE Scripts on Vivado TCL: TE::sw_run_vitis

Note: TCL scripts generate also platform project, this must be done manuelly in case GUI is used. See Vitis

- Run on Vivado TCL: TE::sw_run_vitis -all

...

...

Note:

- Programming and Startup procedure

Programming

| Note |

|---|

Check Module and Carrier TRMs for proper HW configuration before you try any design. |

Xilinx documentation for programming and debugging: Vivado/SDK/SDSoC-Xilinx Software Programming and Debugging

Get prebuilt boot binaries

- _create_win_setup.cmd/_create_linux_setup.sh and follow instructions on shell

- Press 0 and enter to start "Module Selection Guide"

- Select assembly version

- Validate selection

- Select Create and open delivery binary folder

Note: Folder (<project foler>/_binaries_<Artikel Name>) with subfolder (boot_<app name>) for different applications will be generated

QSPI

- Connect JTAG and power on the carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0726" possible - Copy image.ub on SD-Card

- use files from (<project foler>/_binaries_<Articel Name>)/boot_linux from generated binary folder,see: Get prebuilt boot binaries

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Important: Do not copy Boot.bin on SD(is not used see SD note), only other files.

- Copy init.sh on SD-Card

- location: <design_name>/misc/sd/

- Insert SD-Card

SD

Xilinx Zynq devices in CLG225 package do not support SD Card boot directly from ROM bootloader. Use QSPI for primary boot and SD for secondary boot (u-boot)

JTAG

Not used on this Example.

Usage

- Prepare HW like described in section 69107715

- Connect UART USB (most cases same as JTAG)

- Insert SD Card with image.ub

- Power On PCB

Note: 1. Zynq Boot ROM loads FSBL from QSPI into OCM, 2. FSBL loads U-boot from QSPI into DDR, 3. U-boot load Linux from SD into DDR

Linux

- Open Serial Console (e.g. putty)

- Speed: 115200

- COM Port: Win OS, see device manager, Linux OS see dmesg |grep tty (UART is *USB1)

- Linux Console:

Note: Wait until Linux boot finished For Linux Login use:- User Name: root

- Password: root

Note: Wait until Linux boot finished For Linux Login use:- User Name: root

- Password: root

- You can use a Linux shell now.

- I2C 1 Bus type: i2cdetect -y -r 5

Bus 0...5 possible - ETH0 works with udhcpc

- USB: insert USB device

- I2C 1 Bus type: i2cdetect -y -r 5

- Camera stream will be enabled via init.sh script on SD

- Take image from camera (must be enabled with init.sh scripts):

- write image to webserver: fbgrab -d /dev/fb1 /srv/www/camera.png

- Display image on host PC: http://<ZynqBerry IP>/camera.png

System Design - Vivado

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

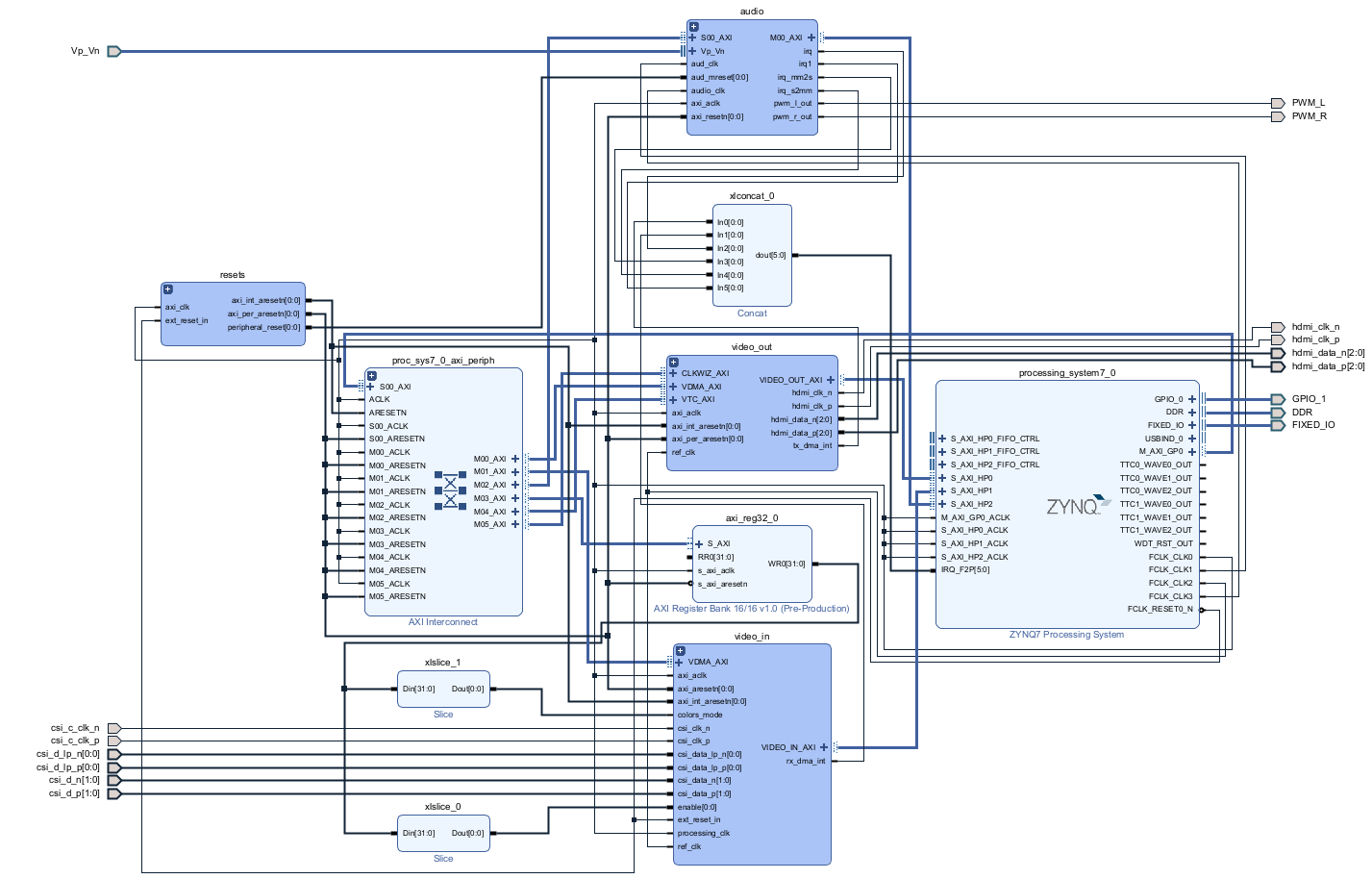

Block Design

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

...

...

Note:

optional for Zynq / ZynqMP only

- add basic PS configuration

Activated interfaces:

...

| anchor | Table_PSI |

|---|---|

| title | PS Interfaces |

...

Constraints

Basic module constraints

| Code Block | ||||

|---|---|---|---|---|

| ||||

#

# Common BITGEN related settings for TE0726

#

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design] |

Design specific constraint

| Code Block | ||||

|---|---|---|---|---|

| ||||

#

#

#

set_property BITSTREAM.CONFIG.UNUSEDPIN PULLUP [current_design] |

| Code Block | ||||

|---|---|---|---|---|

| ||||

#set_property IOSTANDARD LVCMOS33 [get_ports spdif_tx_o]

#set_property PACKAGE_PIN K15 [get_ports spdif_tx_o]

set_property IOSTANDARD LVCMOS33 [get_ports {GPIO_1_tri_io[*]}]

# GPIO Pins

# GPIO2

set_property PACKAGE_PIN K15 [get_ports {GPIO_1_tri_io[0]}]

# GPIO3

set_property PACKAGE_PIN J14 [get_ports {GPIO_1_tri_io[1]}]

# GPIO4

set_property PACKAGE_PIN H12 [get_ports {GPIO_1_tri_io[2]}]

# GPIO5

set_property PACKAGE_PIN N14 [get_ports {GPIO_1_tri_io[3]}]

# GPIO6

set_property PACKAGE_PIN R15 [get_ports {GPIO_1_tri_io[4]}]

# GPIO7

set_property PACKAGE_PIN L14 [get_ports {GPIO_1_tri_io[5]}]

# GPIO8

set_property PACKAGE_PIN L15 [get_ports {GPIO_1_tri_io[6]}]

# GPIO9

set_property PACKAGE_PIN J13 [get_ports {GPIO_1_tri_io[7]}]

# GPIO10

set_property PACKAGE_PIN H14 [get_ports {GPIO_1_tri_io[8]}]

# GPIO11

set_property PACKAGE_PIN J15 [get_ports {GPIO_1_tri_io[9]}]

# GPIO12

set_property PACKAGE_PIN M15 [get_ports {GPIO_1_tri_io[10]}]

# GPIO13

set_property PACKAGE_PIN R13 [get_ports {GPIO_1_tri_io[11]}]

# GPIO16

set_property PACKAGE_PIN L13 [get_ports {GPIO_1_tri_io[12]}]

# GPIO17

set_property PACKAGE_PIN G11 [get_ports {GPIO_1_tri_io[13]}]

# GPIO18

set_property PACKAGE_PIN H11 [get_ports {GPIO_1_tri_io[14]}]

# GPIO19

set_property PACKAGE_PIN R12 [get_ports {GPIO_1_tri_io[15]}]

# GPIO20

set_property PACKAGE_PIN M14 [get_ports {GPIO_1_tri_io[16]}]

# GPIO21

set_property PACKAGE_PIN P15 [get_ports {GPIO_1_tri_io[17]}]

# GPIO22

set_property PACKAGE_PIN H13 [get_ports {GPIO_1_tri_io[18]}]

# GPIO23

set_property PACKAGE_PIN J11 [get_ports {GPIO_1_tri_io[19]}]

# GPIO24

set_property PACKAGE_PIN K11 [get_ports {GPIO_1_tri_io[20]}]

# GPIO25

set_property PACKAGE_PIN K13 [get_ports {GPIO_1_tri_io[21]}]

# GPIO26

set_property PACKAGE_PIN L12 [get_ports {GPIO_1_tri_io[22]}]

# GPIO27

set_property PACKAGE_PIN G12 [get_ports {GPIO_1_tri_io[23]}]

## DSI_D0_N

#set_property PACKAGE_PIN F13 [get_ports {GPIO_1_tri_io[24]}]

## DSI_D0_P

#set_property PACKAGE_PIN F14 [get_ports {GPIO_1_tri_io[25]}]

## DSI_D1_N

#set_property PACKAGE_PIN F12 [get_ports {GPIO_1_tri_io[26]}]

## DSI_D1_P

#set_property PACKAGE_PIN E13 [get_ports {GPIO_1_tri_io[27]}]

## DSI_C_N

#set_property PACKAGE_PIN E11 [get_ports {GPIO_1_tri_io[28]}]

## DSI_C_P

#set_property PACKAGE_PIN E12 [get_ports {GPIO_1_tri_io[29]}]

## CSI_D0_N

#set_property PACKAGE_PIN M11 [get_ports {GPIO_1_tri_io[30]}]

## CSI_D0_P

#set_property PACKAGE_PIN M10 [get_ports {GPIO_1_tri_io[31]}]

## CSI_D1_N

#set_property PACKAGE_PIN P14 [get_ports {GPIO_1_tri_io[32]}]

## CSI_D2_P

#set_property PACKAGE_PIN P13 [get_ports {GPIO_1_tri_io[33]}]

## CSI_C_N

#set_property PACKAGE_PIN N12 [get_ports {GPIO_1_tri_io[34]}]

## CSI_C_P

#set_property PACKAGE_PIN N11 [get_ports {GPIO_1_tri_io[35]}]

## PWM_R

##set_property PACKAGE_PIN N8 [get_ports {GPIO_1_tri_io[36]}]

## PWM_L

##set_property PACKAGE_PIN N7 [get_ports {GPIO_1_tri_io[37]}]

# PWM_R

set_property PACKAGE_PIN N8 [get_ports PWM_R]

# PWM_L

set_property PACKAGE_PIN N7 [get_ports PWM_L]

set_property IOSTANDARD LVCMOS33 [get_ports PWM_*]

|

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property IOSTANDARD TMDS_33 [get_ports hdmi_clk_p]

set_property PACKAGE_PIN R7 [get_ports hdmi_clk_p]

set_property IOSTANDARD TMDS_33 [get_ports {hdmi_data_p[*]}]

set_property PACKAGE_PIN P8 [get_ports {hdmi_data_p[0]}]

set_property PACKAGE_PIN P10 [get_ports {hdmi_data_p[1]}]

set_property PACKAGE_PIN P11 [get_ports {hdmi_data_p[2]}]

|

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property PACKAGE_PIN N11 [get_ports csi_c_clk_p]

set_property IOSTANDARD LVDS_25 [get_ports csi_c_clk_p]

set_property PACKAGE_PIN M9 [get_ports {csi_d_lp_n[0]}]

set_property IOSTANDARD HSUL_12 [get_ports {csi_d_lp_n[0]}]

set_property PACKAGE_PIN N9 [get_ports {csi_d_lp_p[0]}]

set_property IOSTANDARD HSUL_12 [get_ports {csi_d_lp_p[0]}]

set_property PACKAGE_PIN M10 [get_ports {csi_d_p[0]}]

set_property IOSTANDARD LVDS_25 [get_ports {csi_d_p[0]}]

set_property PACKAGE_PIN P13 [get_ports {csi_d_p[1]}]

set_property IOSTANDARD LVDS_25 [get_ports {csi_d_p[1]}]

set_property INTERNAL_VREF 0.6 [get_iobanks 34]

set_property PULLDOWN true [get_ports {csi_d_lp_p[0]}]

set_property PULLDOWN true [get_ports {csi_d_lp_n[0]}]

# RPI Camera 1

create_clock -period 6.250 -name csi_clk -add [get_ports csi_c_clk_p]

# RPI Camera 2.1

#create_clock -period 1.875 -name csi_clk -add [get_ports csi_c_clk_p]

|

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property ASYNC_REG true [get_cells {zsys_i/audio/axi_i2s_adi_0/U0/ctrl/tx_sync/out_data_reg[4]}]

set_property ASYNC_REG true [get_cells {zsys_i/audio/axi_i2s_adi_0/U0/ctrl/SDATA_O_reg[0]}]

set_false_path -from [get_clocks clk_fpga_0] -to [get_clocks clk_fpga_3]

set_false_path -from [get_clocks clk_fpga_3] -to [get_clocks clk_fpga_0]

set_false_path -from [get_pins {zsys_i/axi_reg32_0/U0/axi_reg32_v1_0_S_AXI_inst/slv_reg16_reg[1]/C}] -to [get_pins zsys_i/video_in/axis_raw_demosaic_0/U0/colors_mode_i_reg/D]

set_false_path -from [get_pins zsys_i/video_in/csi_to_axis_0/U0/lane_align_inst/err_req_reg/C] -to [get_pins zsys_i/video_in/csi2_d_phy_rx_0/U0/clock_upd_req_reg/D]

set_false_path -from [get_pins {zsys_i/video_in/axi_vdma_0/U0/I_PRMRY_DATAMOVER/GEN_S2MM_FULL.I_S2MM_FULL_WRAPPER/GEN_INCLUDE_REALIGNER.I_S2MM_REALIGNER/GEN_INCLUDE_SCATTER.I_S2MM_SCATTER/sig_max_first_increment_reg[2]/C}] -to [get_pins zsys_i/video_in/axi_vdma_0/U0/I_PRMRY_DATAMOVER/GEN_S2MM_FULL.I_S2MM_FULL_WRAPPER/GEN_INCLUDE_REALIGNER.I_S2MM_REALIGNER/GEN_INCLUDE_SCATTER.I_S2MM_SCATTER/sig_btt_eq_0_reg/D]

set_false_path -from [get_pins {zsys_i/video_in/axi_vdma_0/U0/I_PRMRY_DATAMOVER/GEN_S2MM_FULL.I_S2MM_FULL_WRAPPER/GEN_INCLUDE_REALIGNER.I_S2MM_REALIGNER/GEN_INCLUDE_SCATTER.I_S2MM_SCATTER/sig_btt_cntr_dup_reg[1]/C}] -to [get_pins zsys_i/video_in/axi_vdma_0/U0/I_PRMRY_DATAMOVER/GEN_S2MM_FULL.I_S2MM_FULL_WRAPPER/GEN_INCLUDE_REALIGNER.I_S2MM_REALIGNER/GEN_INCLUDE_SCATTER.I_S2MM_SCATTER/sig_btt_eq_0_reg/D]

|

Software Design - Vitis

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

For SDK project creation, follow instructions from:

Application

...

| hidden | true |

|---|---|

| id | Comments |

----------------------------------------------------------

FPGA Example

scu

MCS Firmware to configure SI5338 and Reset System.

srec_spi_bootloader

TE modified 2018.3 SREC

Bootloader to load app or second bootloader from flash into DDR

Descriptions:

- Modified Files: blconfig.h, bootloader.c

- Changes:

- Add some console outputs and changed bootloader read address.

- Add bugfix for 2018.2 qspi flash

xilisf_v5_11

TE modified 2018.3 xilisf_v5_11

- Changed default Flash type to 5.

----------------------------------------------------------

Zynq Example:

zynq_fsbl

TE modified 2018.3 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

Module Specific:

- Add Files: all TE Files start with te_*

- READ MAC from EEPROM and make Address accessible by UBOOT (need copy defines on uboot platform-top.h)

- CPLD access

- Read CPLD Firmware and SoC Type

- Configure Marvell PHY

zynq_fsbl_flash

TE modified 2018.3 FSBL

General:

- Modified Files: main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

ZynqMP Example:

----------------------------------------------------------

zynqmp_fsbl

TE modified 2018.3 FSBL

General:

- Modified Files: xfsbl_main.c, xfsbl_hooks.h/.c, xfsbl_board.h/.c(search for 'TE Mod' on source code)

- Add Files: te_xfsbl_hooks.h/.c (for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device Name

Module Specific:

- Add Files: all TE Files start with te_*

- Si5338 Configuration

- ETH+OTG Reset over MIO

zynqmp_fsbl_flash

TE modified 2018.3 FSBL

General:

- Modified Files: xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

zynqmp_pmufw

Xilinx default PMU firmware.

----------------------------------------------------------

General Example:

hello_te0820

Hello TE0820 is a Xilinx Hello World example as endless loop instead of one console output.

u-boot

U-Boot.elf is generated with PetaLinux. SDK/HSI is used to generate Boot.bin.

SDK Template location: ./sw_lib/sw_apps/

zynq_fsbl

TE modified 2019.2 FSBL

General:

- Modified Files:main.c, fsbl_hooks.h/.c (search for 'TE Mod' on source code)

Add Files: te_fsbl_hooks.h/.c(for hooks and board)\n\

- General Changes:

- Display FSBL Banner and Device ID

Module Specific:

- Add Files: all TE Files start with te_*

- enable VTC and VDMA cores for camera access

zynq_fsbl_flash

TE modified 2019.2 FSBL

General:

- Modified Files: main.c

- General Changes:

- Display FSBL Banner

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

hello_te0726

Hello TE0726 is a Xilinx Hello World example as endless loop instead of one console output.

u-boot

U-Boot.elf is generated with PetaLinux. Vitis is used to generate Boot.bin.

Software Design - PetaLinux

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note:

|

For PetaLinux installation and project creation, follow instructions from:

Config

Start with petalinux-config or petalinux-config --get-hw-description

Changes:

For 64MB variant only:

- CONFIG_SUBSYSTEM_NETBOOT_OFFSET = 0x2000000

For 128MB variant only:

- CONFIG_SUBSYSTEM_NETBOOT_OFFSET = 0x4000000

U-Boot

Start with petalinux-config -c u-boot

Changes:

CONFIG_ENV_IS_NOWHERE=y

# CONFIG_ENV_IS_IN_SPI_FLASH is not set

Device Tree

...

| language | js |

|---|

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

Kernel

Start with petalinux-config -c kernel

Changes:

...

CONFIG_XILINX_GMII2RGMII=y

...

CONFIG_USB_USBNET=y

...

CONFIG_USB_NET_AX8817X=y

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

...

CONFIG_USB_BELKIN=y

...

CONFIG_USB_ARMLINUX=y

...

...

...

...

...

...

...

...

...

...

...

# CONFIG_USB_NET_KALMIA is not set

...

# CONFIG_USB_NET_QMI_WWAN is not set

...

# CONFIG_USB_NET_INT51X1 is not set

...

# CONFIG_USB_SIERRA_NET is not set

...

# CONFIG_USB_VL600 is not set

...

# CONFIG_USB_NET_CH9200 is not set

...

CONFIG_USBIP_CORE=y

...

# CONFIG_USBIP_VHCI_HCD is not set

...

# CONFIG_USBIP_HOST is not set

...

# CONFIG_USBIP_VUDC is not set

...

# CONFIG_USBIP_DEBUG is not set

...

CONFIG_FB_SIMPLE=y

...

CONFIG_SND_SIMPLE_CARD_UTILS=y

...

CONFIG_SND_SIMPLE_CARD=y

...

Rootfs

Start with petalinux-config -c rootfs

Changes:

...

...

Application used to take screenshot from camera

See: \os\petalinux\project-spec\meta-user\recipes-apps\fgrab

...

Kernel Modules

te-audio-codec

Simple module stab to use audio interface.

See: \os\petalinux\project-spec\meta-user\recipes-modules\te-audio-codec\files

...

...

...

Authors

...

| Page info | ||||||||

|---|---|---|---|---|---|---|---|---|

|

...