Page History

| Page properties | ||||

|---|---|---|---|---|

| ||||

Template Revision 2.2 TRM Name always "TE Series Name" +TRM, for example "TE0720 TRM" |

| HTML |

|---|

<!-- tables have all same width (web max 1200px and pdf full page(640px), flexible width or fix width on menu for single column can be used as before) -->

<style>

.wrapped{

width: 100% !important;

max-width: 1200px !important;

}

</style> |

| Page properties | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||

Important General Note:

|

| Page properties | ||||

|---|---|---|---|---|

| ||||

----------------------------------------------------------------------- |

| Page properties | ||||

|---|---|---|---|---|

| ||||

Note for Download Link of the Scroll ignore macro:

|

| Scroll Ignore |

|---|

Download PDF Version version of this Documentdocument. |

| Scroll pdf ignore | |

|---|---|

Table of Contents

|

Overview

...

...

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

...

The Trenz Electronic TE0714 is an industrial-grade SoM (System on Module) based on Xilinx Artix-7, 16 Mbyte MByte Flash memory and powerful switching mode power supplies for all on-board voltages. A large number of configurable I/O's is provided via rugged high-speed stacking strips. All modules in 4 x 5 cm form factor are mechanically compatible.

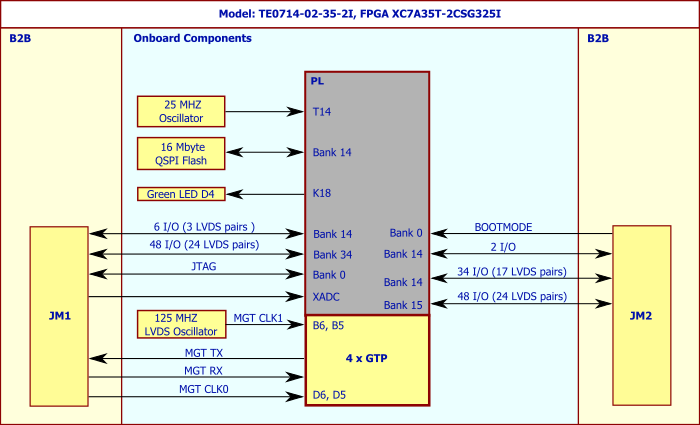

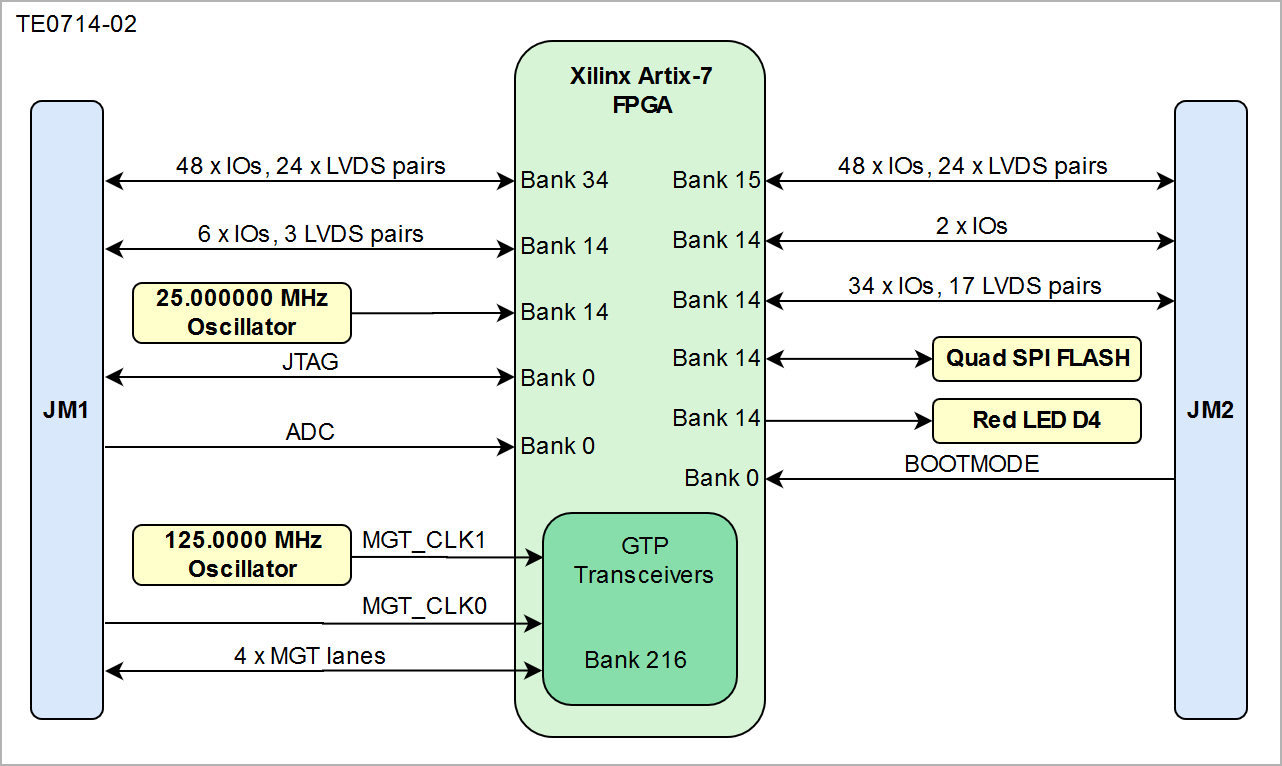

Block Diagram

Main Components

...

...

...

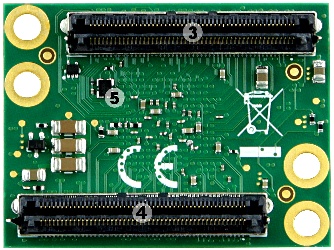

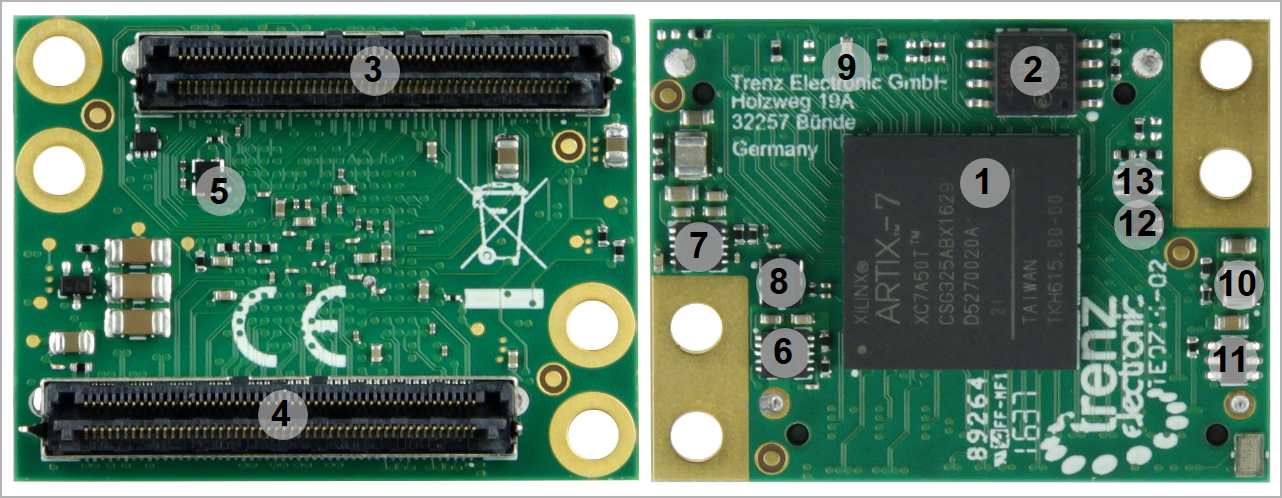

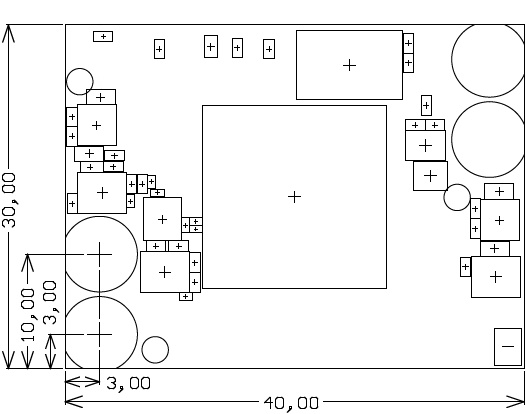

Top view

...

- Xilinx Artix-7 FPGA, U4

- SPI Flash, U7

- B2B Connector, JM2

- B2B Connector, JM1

- MEMS Oscillator (PL Clock), U8

- Single Output Low-Dropout Linear Regulator, U6 (1.2V_MGT)

- Single Output Low-Dropout Linear Regulator, U5 (1.0V_MGT)

- Low-Jitter Precision LVDS Oscillator (GT Clock), U2

- Red Indication LED,D4

- Step-Down DC-DC Converter, U1 (1.0V)

- PFET Load Switch With Configurable Slew Rate, Q1 (3.3V)

- Low Power Step-Down DC-DC Converter, U3 (1.8V)

- Voltage Detector for Circuit Initialization and Timing Supervision, U23

Key Features

TE0714 is the smallest module with transceiver (3 x 4 cm).

Refer to http://trenz.org/te0714-info for the current online version of this manual and other available documentation.

Key Features

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Xilinx Artix-7 FPGA

...

(A15T, A35T, A50T)

- Rugged for

...

- shock and

...

- high vibration

- 16 MByte QSPI Flash

...

- memory

- Differential MEMS

...

- oscillator for

...

- MGT clocking

- MEMS

...

- oscillator for PL

...

- clocks (Optional)

- Plug-

...

- on module with 2 × 100-

...

- pin high-speed hermaphroditic strips

- 138

...

- FPGA I/O's (Max 68

...

- differential)

5 IO's (QSPI or user I/O's)

- XADC

...

- analog input

- 4 GTP (

...

- high-

...

- performance transceiver)

...

- lanes

- GT

...

- reference clock inputs

- Optimized I/O and

...

- power pins for good signal integrity

- On-board

...

- high-

...

- efficiency DC-DC

...

- converters

- Power

...

- supply for

...

- all on-board components

- eFUSE

...

- bit-

...

- stream encryption (AES)

- One

...

- user configurable LED

Different configurations for cost and performance optimization available upon request. Available options are:

- FPGA Type (A15T, A35T, A50T), temperature grade

- GT

...

- clock frequency (or none if not implemented)

- PL

...

- clock frequency and precision (or none if not implemented)

- Config and B14

...

- bank Voltage: 1.8V or 3.3V

- SPI Flash type (or none if not implemented)

- LED Color (or none if not implemented)

- PUDC Pin strapping (pull high or pull down)

- GT

...

- power enable pin strapping (default power enabled or disabled)

Block Diagram

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

Main Components

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

- Xilinx Artix-7 FPGA (XC7A series), U4

- 16 MByte SPI Flash, U7

- B2B connector Samtec Razor Beam™ LSHM-150, JM2

- B2B connector Samtec Razor Beam™ LSHM-150, JM1

- 25 MHz oscillator, U8

- Single output low-dropout linear regulator (1.2V_MGT), U6

- Single output low-dropout linear regulator (1.0V_MGT), U5

- Low-jitter precision LVDS 125 MHz oscillator (GT Clock), U2

- Red indication LED, D4

- Step-down DC-DC converter (1.0V), U1

- PFET load switch with configurable slew rate (3.3V), Q1

- Low-power step-down DC-DC converter (1.8V), U3

- Voltage detector for circuit initialization and timing supervision, U23

Initial Delivery State

| Scroll Title | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||

|

|

|

|

Signals, Interfaces and Pins

JTAG Interface

JTAG access to the Xilinx Artix-7 device is provided through connector JM1.

...

...

...

Clocking

...

Clock

...

Default Frequency

...

IC

...

FPGA

...

Notes

...

25 MHz

...

U8

...

T14

...

125MHz

...

U2

...

B6/B5

...

Frequency depends on the module variant

Boot Modes

Boot mode is controlled by the MODE signal on the board to board (B2B) connector:

Control Signals

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

| Scroll Title | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||

|

...

MODE signal State

...

|

| Note |

|---|

SPI |

...

FPGA pins D02 and |

...

D03 have no pull-ups on the module, so with PUDC=High option, those pins are floating if there are no pull-ups on baseboard. As those pins have SPI RESET function when Quad mode is not enabled, it is mandatory to either add pull-ups on user baseboard or program the Quad Enable bit in Flash nonvolatile status register. |

Signals, Interfaces and Pins

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

JTAG Interface

JTAG access to the Xilinx Artix-7 FPGA device is provided through connector JM1.

| Scroll Title | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||

|

Board to Board (B2B) I/Os

FPGA bank number and number of I/O signals connected to the B2B connector:

| Scroll Title | ||||

|---|---|---|---|---|

|

...

|

Please refer to the Pin-out tables page for additional information.

On-board Peripherals

| Page properties | ||||

|---|---|---|---|---|

| ||||

Notes :

|

Quad SPI Flash

On-board SPI flash memory S25FL127S (U7) is used to store initial FPGA configuration. Besides FPGA configuration, remaining free flash memory can be used for user application storage. All four SPI data lines are connected to the FPGA allowing x1, x2 or x4 data bus widths. Maximum data rate depends on the bus width and clock frequency used.

| Note |

|---|

SPI Flash QE (Quad Enable) bit must be set to high or FPGA is unable to load its configuration from flash. By default this bit is set to high at the manufacturing plant. |

On-board LED

There is one LED on TE0714 module:.

| Scroll Title | |||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||

|

...

|

Clock

| Scroll Title | |||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||

|

...

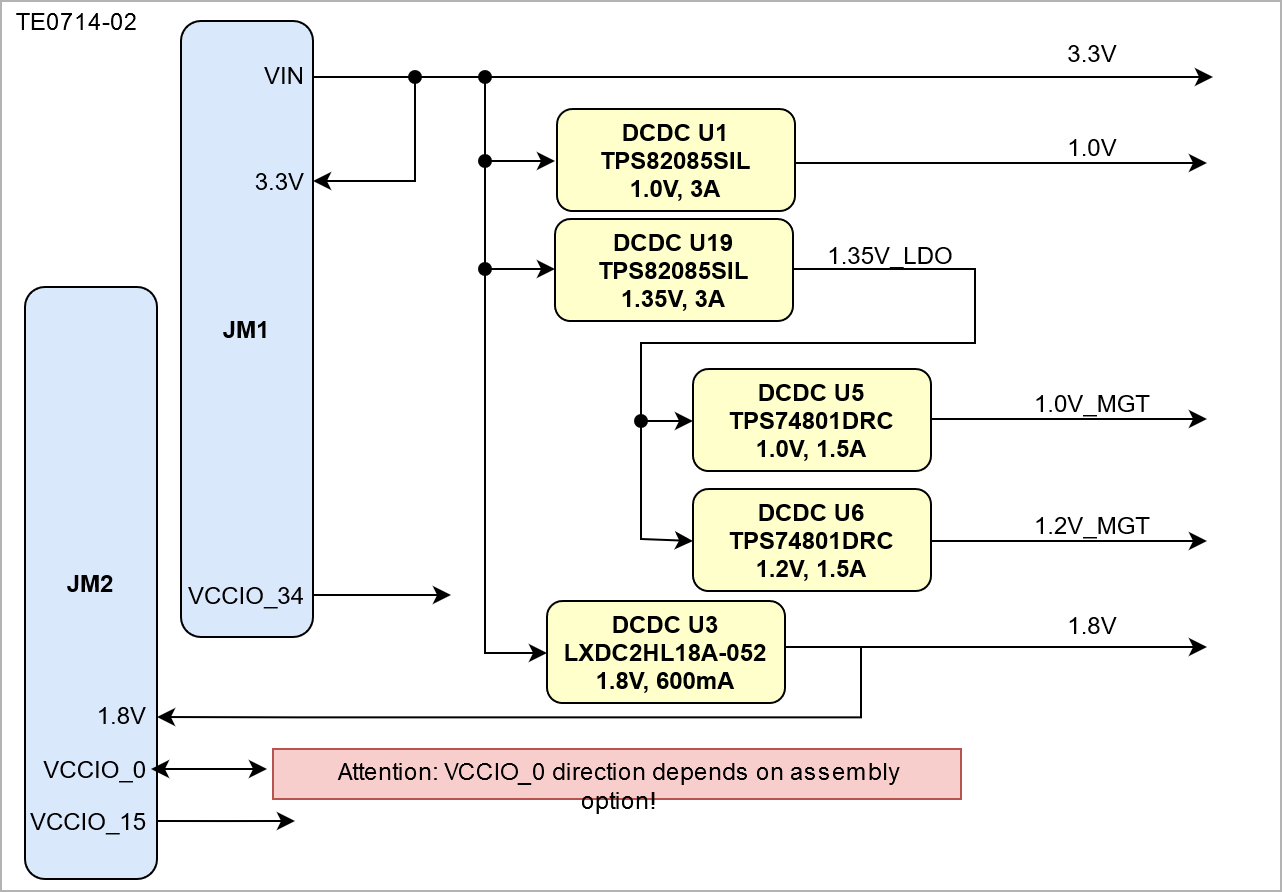

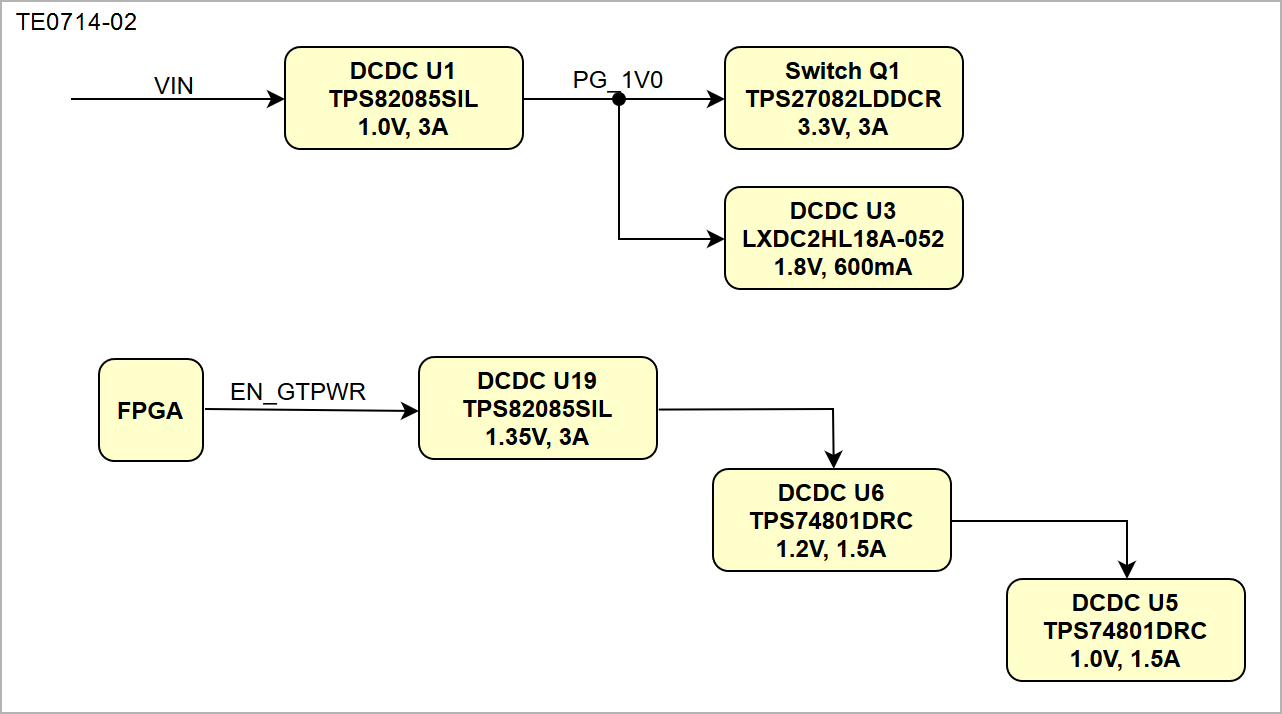

Power and Power-On Sequence

To power-up a module, power supply with minimum current capability of 1A is recommended.

Power Suppy

TE0714 needs one single power supply with nominal of 3.3V.

Power Consumption

| Scroll Title | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||

|

...

Actual power consumption depends on the FPGA design and ambient temperature.

Power Distribution Dependencies

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

Power-On Sequence

There is no specific or special power-on sequence, single power source is needed as VIN, rest of the sequence is automatic.

Bank Voltages

...

Bank

...

Voltage

...

Notes

...

0 Config and B14

...

1.8V or 3.3V

...

15

...

User

...

Supplied from baseboard via B2B connector, max 3.3V

...

34

...

User

...

Variants Currently In Production

...

FPGA Chip Model

...

B14/Config Voltage [V]

...

LED

D4

...

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

Power Rails

| Scroll Title | |||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||||||||||||||||||||||||||||

|

Bank Voltages

| Scroll Title | ||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||

|

Board to Board Connectors

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

| Include Page | ||||

|---|---|---|---|---|

|

Technical Specifications

Absolute Maximum Ratings

| Scroll Title | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||

|

| Note |

|---|

On REV 01 JM2 Pin 54 was connected to GND. When R27 is not populated, REV 02 is backwards compatible to REV 01. When R27 is set, check your baseboard to not connect this pin to GND. For all new baseboards JM2.54 should be used as VCCIO output (it will then be 1.8V or 3.3V depending the voltage settings on the module. |

Technical Specifications

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

Recommended Operating Conditions

|

Recommended Operating Conditions

| Scroll Title | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||

This TRM is generic for all variants. Variants of modules are described here: Article Number Information Modules with commercial temperature grade are equipped with components that cover at least the range of 0°C to 75°C Modules with extended temperature grade are equipped with components that cover at least the range of 0°C to 85°C Modules with industrial temperature grade are equipped with components that cover at least the range of -40°C to 85°C The actual operating temperature range will depend on the FPGA / SoC design / usage and cooling and other variables.

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

|

...

| ||||

| Note | ||||

|---|---|---|---|---|

| Please check Xilinx datasheet DS181 for complete list of absolute maximum and recommended operating ratings for the Artix-7. |

Physical Dimensions

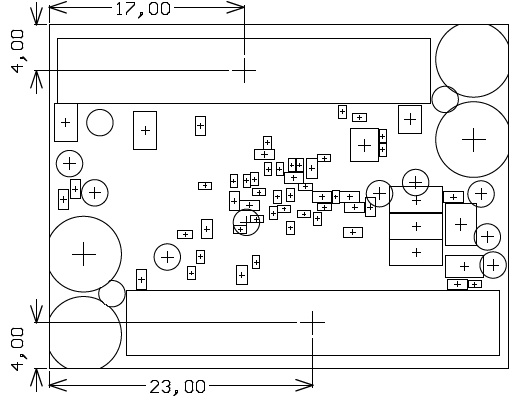

Module size: 40 mm × 30 mm. Please download the assembly diagram for exact numbers.

Mating height with standard connectors: 8 mm

PCB thickness: 1.6 mm

Highest part on PCB: approximately 2.5 mm. Please download the step model for exact numbers.

All dimensions are shown in mm. Additional sketches, drawings and schematics can be found here.

...

...

...

Operating Temperature Ranges

Commercial grade modules

All parts are at least commercial temperature range of 0 °C to +70 °C. The module operating temperature range depends on customer design and cooling solution. Please contact us for options.

Industrial grade modules

All parts are at least industrial temperature range of -40 °C to +85 °C. The module operating temperature range depends on customer design and cooling solution. Please contact us for options.

Weight

...

Revision History

Hardware Revision History

| Scroll Title | ||||

|---|---|---|---|---|

| ||||

Variants Currently In Production

| Page properties | ||||

|---|---|---|---|---|

| ||||

|

| Scroll Title | ||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||

| ||||||||||||||||||

| Note |

|---|

On REV 01 JM2 Pin 54 was connected to GND. When R27 is not populated, REV 02 is backwards compatible to REV 01. When R27 is set, check your baseboard to not connect this pin to GND. For all new baseboards JM2.54 should be used as VCCIO output (it will then be 1.8V or 3.3V depending the voltage settings on the module. |

Revision History

Hardware Revision History

| Scroll Title | |||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||||

|

...

Changes

...

01

...

Current Hardware Revision, no changes

...

|

...

|

Hardware revision number is printed on the PCB board next to the module model number separated by the dash.

Document Change History

| Scroll Title | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

...

|

...

|

...

|

...

|

...

|

...

|

Disclaimer

|

...

Disclaimer

| Include Page | ||||

|---|---|---|---|---|

|