This TRM is generic for all variants. Variants of modules are described here: Article Number Information Modules with commercial temperature grade are equipped with components that cover at least the range of 0°C to 75°C Modules with extended temperature grade are equipped with components that cover at least the range of 0°C to 85°C Modules with industrial temperature grade are equipped with components that cover at least the range of -40°C to 85°C The actual operating temperature range will depend on the FPGA / SoC design / usage and cooling and other variables. | Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders |

|---|

| | Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

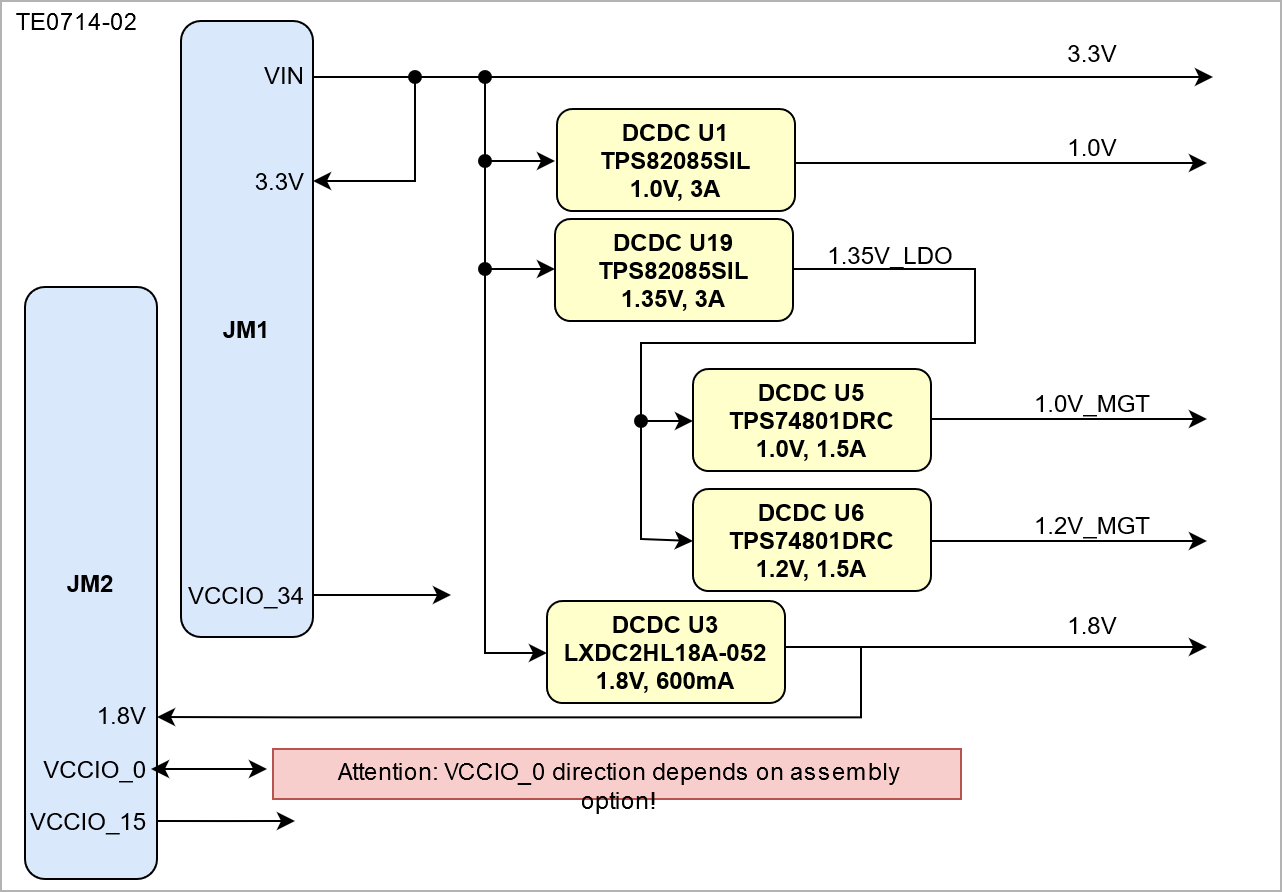

| Parameter | Min | Max | Units | Reference Document |

|---|

| VIN supply voltage | 3.135 | 3.45 | V | - | | HR I/O banks supply voltage (VCCO) | 1.14 | 3.465 | V | Xilinx datasheet DS181 | | HR I/O banks input voltage | -0.20 | VCCO + 0.2020V | V | Xilinx datasheet DS181 | | Voltage on module JTAG pins | 3.135 | 3.465 | | 0 | VCCO_0 + 5% | V | Xilinx datasheet DS181 |

|