Page History

...

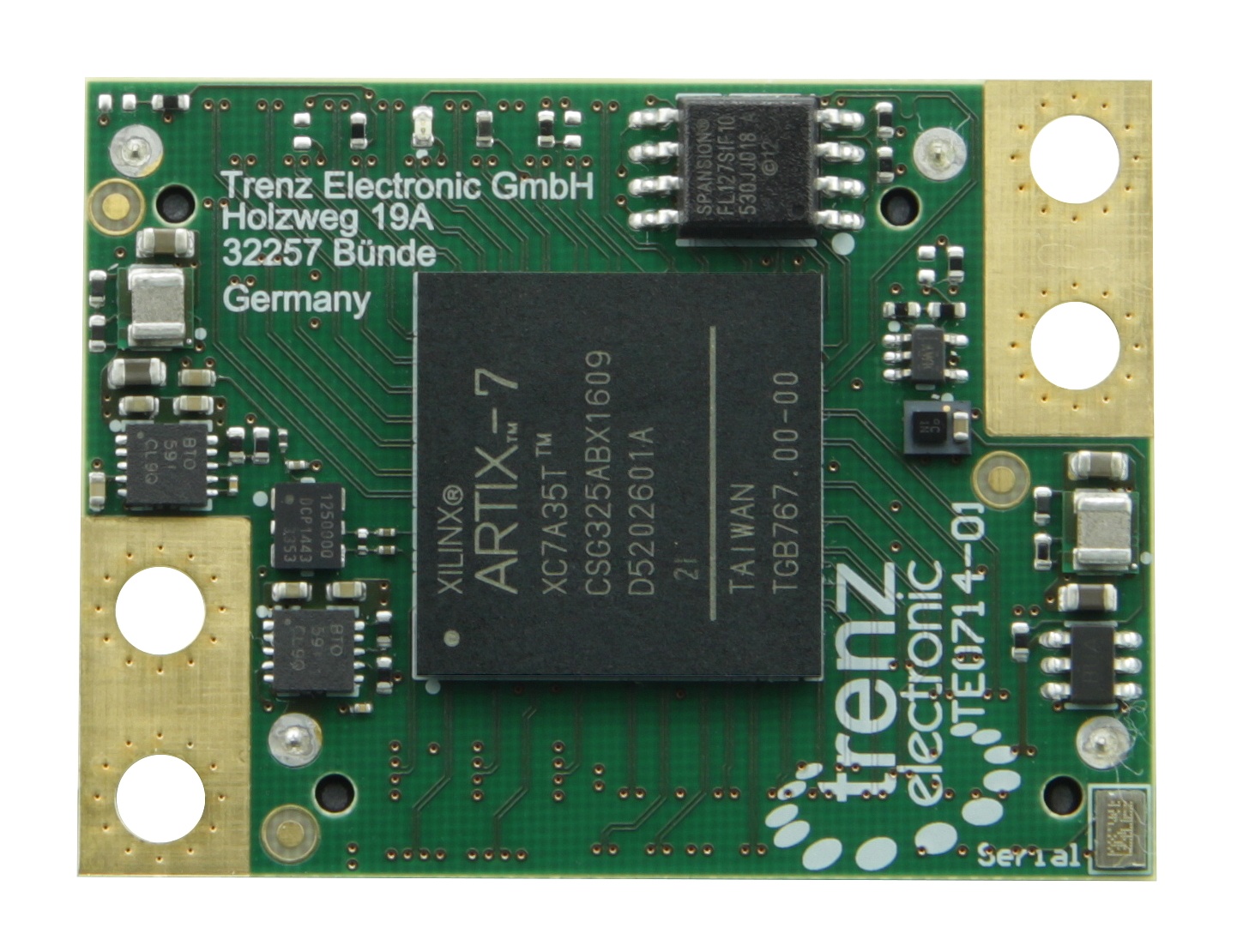

The Trenz Electronic TE0714 is an industrial-grade SoM (System om on Module) based on Xilinx Artix-7, 16 MByte Flash memory and powerful switch-switching mode power supplies for all on-board voltages. A large number of configurable I/O's is provided via rugged high-speed stacking strips. All modules in 4 x 5 cm form factor are mechanically compatible.

Block diagram

Board Components

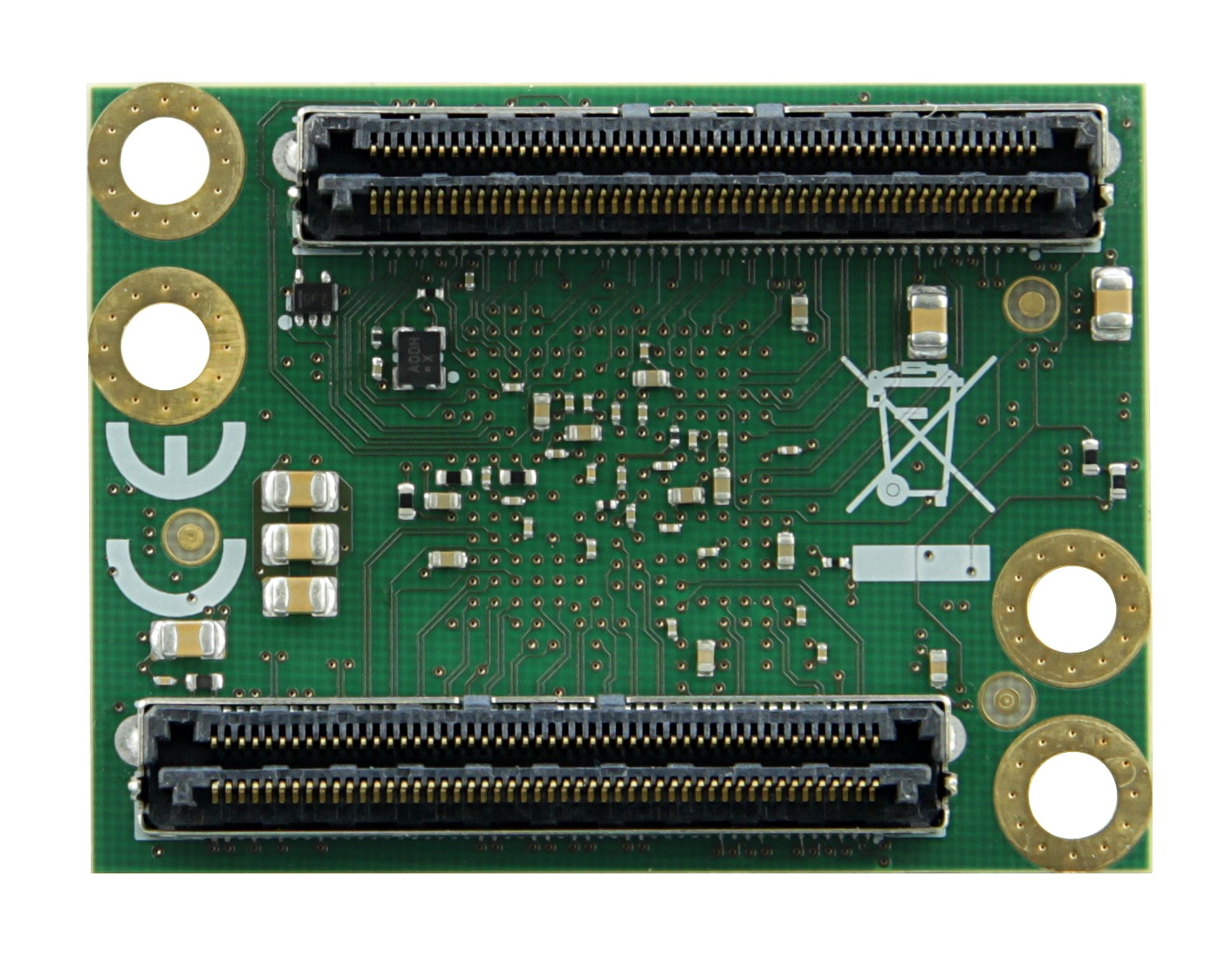

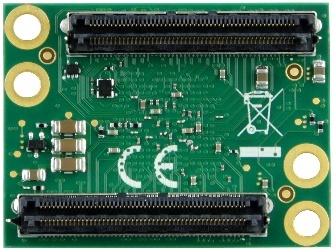

Top view | Bottom view |

Main Components:

...

Key Features

Xilinx Artix-7 (A15T, A35T, A50T)

- Rugged for shock and high vibration

- 16 MByte QSPI Flash memory

- Differential MEMS Oscillator for GT Clocking

- MEMS Oscillator for PL Clocks (option)

- Plug-on module with 2 × 100-pin high-speed hermaphroditic strips

- 144 FPGA I/O's (max 68 differential)

- XADC Analog Input

- 4 GTP (high-performance transceiver) lanes

- GT Reference Clock input

- Optimized I/O and power pins for good signal integrity

- On-board high-efficiency DC-DC converters

- eFUSE bit-stream encryption (AES)

- One user LED

Assembly options for cost or performance optimization available upon request. Possible options:

- FPGA Type (A15T, A35T, A50T), temperature grade

- GT Clock Frequency (or none if not assembled)

- PL Clock Frequency and precision or none if not assembled)

- Config and B14 Bank Voltage: 1.8V or 3.3V

- SPI Flash type (or none if not assembled)

- LED Color (or none if not assembled)

- PUDC Pin strapping (pull high or pull down)

- GT Power Enable pin strapping (default power enabled or disabled)

Current Assembly Variants

| Variant | FPGA | GT Clock [MHz] | PL Clock [MHz] | PUDC | GT PWR Enable | B14/Config Voltage [V] | R27 (VCCIO_0 on JM2 Pin 54) | SPI Flash | LED |

|---|---|---|---|---|---|---|---|---|---|

| TE0714-02-35-2I | A35T-2I | 125MHz125 | 25Mhz25 | High | Enabled | 3.3V3 | JM2 Pin 54 = VCCIO_0 (3.3V3 V) | S25FL127S | Red |

| TE0714-02-35-2IC6 | A35T-2I | 125MHz125 | 25MHz25 | High | Enabled | 1.8V8 | JM2 Pin 54 = Open | N25Q128 | Red |

| TE0714-02-35-2IC7 | A35T-2I | 125MHz125 | 25MHz25 | Low | Enabled | 3.3V3 | JM2 Pin 54 = Open | S25FL127S | Red |

| TE0714-02-50-2I | A50T-2I | 125MHz125 | 25Mhz25 | High | Enabled | 3.3V3 | JM2 Pin 54 = VCCIO_0 (3.3V3 V) | S25FL127S | Red |

| TE0714-02-50-2IC6 | A50T-2I | 125MHz125 | 25MHz25 | High | Enabled | 1.8V8 | JM2 Pin 54 = Open | N25Q128 | Red |

| Note |

|---|

On REV 01 JM2 Pin 54 was GND. When R27 is not populated, REV 02 is backard backwards compatible to REV 01. When R27 is set, check your baseboard to not connect this pin to GND. For all new baseboards JM2.54 should be used as VCCIO output (it will then be 1.8V or 3.3V depending the Votlage setting voltage settings on the module. |

Signals, Interfaces and Pins

...

| Note |

|---|

SPI D2 and D3 have no pullups pull-ups on the module so with PUDC=High option, those pins are floating if there are no pullups pull-ups on baseboard. As those pins have SPI RESET function when Quad mode is not enabled, it is mandatory to either add pullups pull-ups on user base baseboard or program the Quad Enable bit in Flash nonvolatile status register. |

...

| PCB Revision | Changes | PCN link | Documentation link |

|---|---|---|---|

01 | Current Hardware Revision, no changes | - | TE0714-01 TRM |

| 02 | VCCIO0 added to B2B | PCN-20160815 |

...

| Parameter | Min | Max | Units | Notes | Reference document |

|---|---|---|---|---|---|

| Vin supply voltage | 3.135 | 3.45 | V | ||

| IO Bank supply voltage for I/O banks | 1.14 | 3.465 | V | Xilinx document DS181 | |

| I/O input voltage for I/O banks | -0.20 | Vcco + 0.20 | V | Xilinx document DS181 | |

| Voltage on Module JTAG pins | 3.135 | 3.465 | V | For assembly variant with 3.3V CONFIG Bank Option | Xilinx document DS181 |

| Note |

|---|

| Please check Xilinx Datasheet datasheet for complete list of Absolute absolute maximum and recommended operating ratings for the Artix-7 device (DS181). |

...

Module size: 40 mm × 30 mm. Please download the assembly diagram for exact numbers.

Mating height with standard connectors: 8 mm

PCB thickness: 1.6 mm

Highest part on PCB: approx. approximately 2.5 mm. Please download the step model for exact numbers.

All dimensions are shown in mm and can be found here.

Temperature Ranges

Commercial grade modules

...

Date | Revision | Authors | Description |

|---|---|---|---|

| 2016-11-18 | Antti Lukats, Thorsten Trenz | changes for REV 02 | |

2016-06-01 | V.9 | initial version |

Disclaimer

...