Page History

| HTML |

|---|

<!-- Template Revision 1.4 beta (HTML comment will not display, it's not needed to remove them. For Template/Skeleton changes, increase Template Revision number. So we can check faster, if the TRM style is up to date) --> |

| Scroll Ignore |

|---|

Download PDF version of this document. |

| Scroll pdf ignore | |

|---|---|

Table of Contents

|

Overview

| Scroll Only (inline) |

|---|

Refer to https://shop.trenz-electronic.de/en/Download/?path=Trenz_Electronic/carrier_boards/TEBF0808/REV04 for downloadable version of this manual and additional technical documentation of the product. |

The Trenz Electronic TEBF0808 carrier board is a baseboard for the Xilinx Zynq Ultrascale+ MPSoC modules TE0808 and TE0803, which exposes the module's B2B connector pins to accessible connectors and provides a whole range of on-board components to test and evaluate the Zynq Ultrascale+ SoMs and for developing purposes. The carrier board has a Mini-ITX form factor making it capable to be fitted into a PC enclosure. On the PC enclosure's rear and front panel, essential data interfaces, sockets and connectors are accessible.

Key Features

- Mini-ITX form factor, PC enclosure compatible

- ATX-24 power supply connector

- Optional 12V standard power plug

- Headers

- Intel 10-pin HDA Audio

- Intel 9-pin Power-/Reset-Button, Power-/HD-LED

- PC-BEEPER

- On-board Power- / Reset-Switches

- 2x Configuration 4-bit DIP-switches

- 2x Optional 4-wire PWM fan connectors

- PCIe Slot - one PCIe lane (16 lane connector)

- CAN FD Transceiver (10 Pin IDC connector and 6-pin header)

- 4x On-board configuration EEPROMs (1x Microchip 24LC128-I/ST, 3x Microchip 24AA025E48T-I/OT)

- Dual SFP+ Connector (2x1 Cage)

- One Display-Port (single lane)

- One SATA Connector

- 2x USB3.0 A Connector (Superspeed Host Port (Highspeed at USB2.0))

- 1x USB3.0 on-board header with two ports

- FMC HPC Slot (FMC_VADJ max. VCCIO)

- FMC Fan

- Gigabit Ethernet RGMII PHY with RJ45 MegJack

- All Carrier Board peripherals' I²C-interfaces muxed to MPSoC's I²C-interface on PS bank 503

- Quad programmable PLL clock generator SI5338A

- 2x SMA coaxial connectors for clock signals

- MicroSD- / MMC-Card Socket (bootable)

- 32 Gbit on-board eMMC memory (8 banks a 4 Gbit)

- Two System Controller CPLDs Lattice MachXO2 1200 HC

- One Samtec FireFly (4 GT lanes bidirectional)

- One Samtec FireFly connector for reverse loopback

- 2x JTAG/UART header ('XMOD FTDI JTAG Adapter'-compatible) for programming MPSoC and SC CPLDs

- 20 Pin ARM JTAG Connector (PS JTAG0)

- 3x PMOD connector (GPIO's and I²C interface to SC CPLDs / MPSoC module

- Carrier SC CPLD managing power-up sequence of MPSoC module

- On-board DC-DC PowerSoCs

Additional assembly options are available for cost or performance optimization upon request.

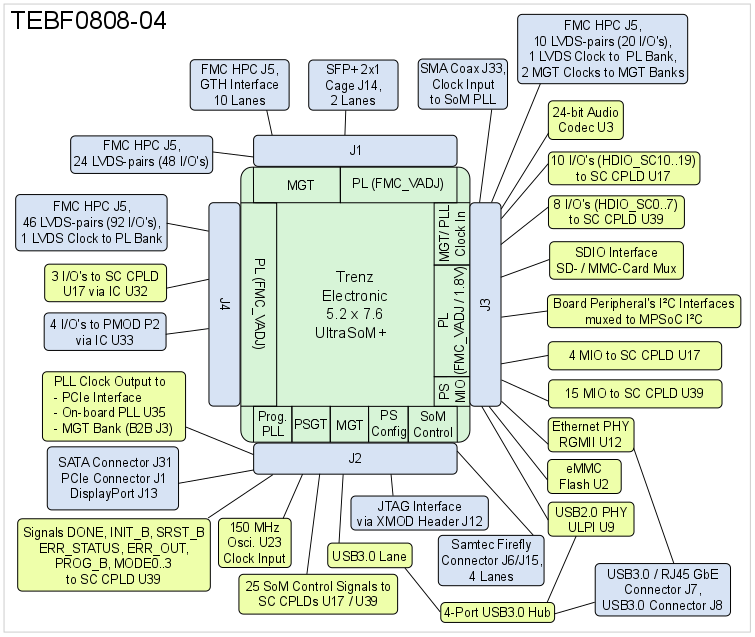

Block Diagram

Figure 1: TEBF0808-04 Block Diagram

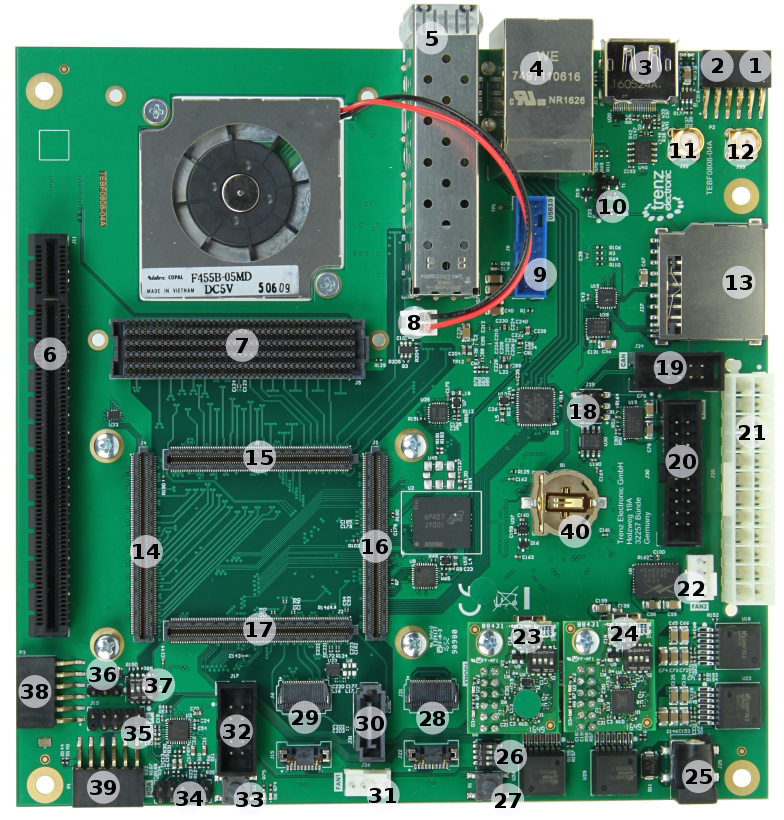

Main Components

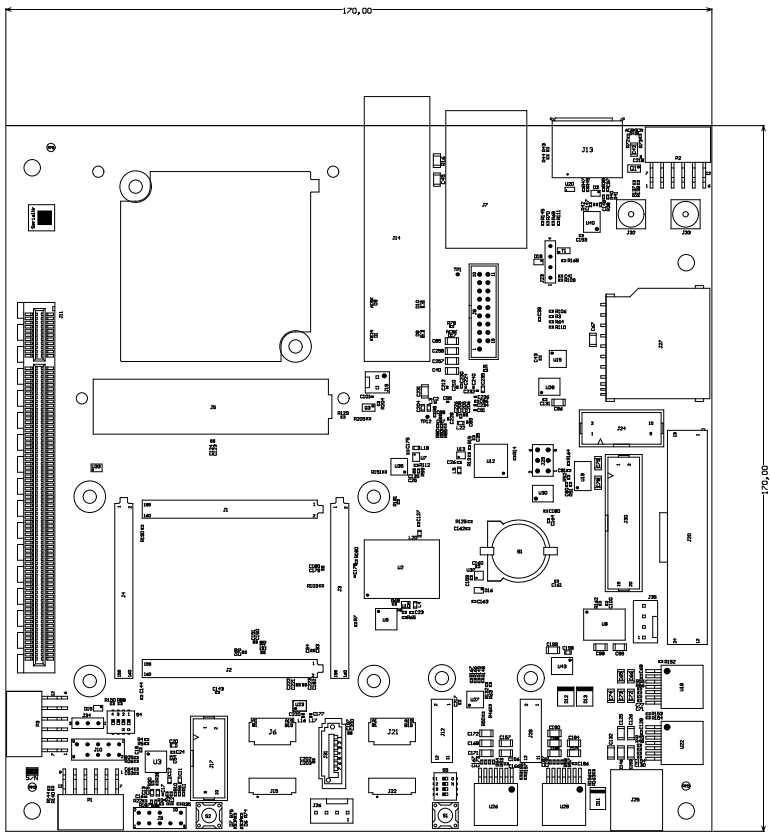

Figure 2: TEBF0808-04 Carrier Board

- PMOD connector, P2

- MicroSD Card socket (on bottom side), J16

- Display Port socket, J13

- USB3.0 A 2x , RJ45 1x (stacked), J7

- SFP+ 2x1 cage, J14

- PCIe x16 connector (one PCIe lane connected), J11

- FMC HPC, J5

- FMC-Fan connector 5V, J19

- USB3.0 connector, J8

- PC-BEEPER 4-pin header, J23

- SMA coaxial connector (SI5338A clock output), J32

- SMA coaxial connector (clock input to MPSoC module), J33

- eMMC Card socket, J27

- Ultra fine 0.50 mm pitch, Razor Beam™ LP Slim Terminal Strip with 160 contacts, J4

- Ultra fine 0.50 mm pitch, Razor Beam™ LP Slim Terminal Strip with 160 contacts, J1

- Ultra fine 0.50 mm pitch, Razor Beam™ LP Slim Terminal Strip with 160 contacts, J3

- Ultra fine 0.50 mm pitch, Razor Beam™ LP Slim Terminal Strip with 160 contacts, J2

- CAN bus 6-pin header, J29

- CAN bus 10-pin connector, J24

- ARM-JTAG 20-pin connector, J30

- ATX power supply connector, J20

- 4-Wire PWM fan connector, J35

- JTAG/UART header ('XMOD FTDI JTAG Adapter'-compatible) for access to MPSoC module, J12

- JTAG/UART header ('XMOD FTDI JTAG Adapter'-compatible) for access to System Controller CPLDs, J28

- Power Jack 2.1mm 12V, J25

- 4-bit DIP-switch, S5

- Power Button, S1

- Samtec FireFly Connector for reverse loopback, J21/J22

- Samtec FireFly Connector (4 GT lanes bidirectional), J6/J15

- SATA Header, J31

- 4-Wire PWM fan connector, J26

- Programmable on-module PLL I²C interface 10-pin header, J17

- Reset Button, S2

- INTEL HDA 9-pin header, J9

- Intel front panel (PWR-/RST-Button, HD-/PWR-LED) 9-pin header, J10

- Samtec FireFly Connector J6/J15 I²C interface 3-pin header, J34

- 4-bit DIP-switch, S4

- PMOD connector, P3

- PMOD connector, P1

- Battery Holder CR1220, B1

Initial Delivery State

Storage device name | Content | Notes |

|---|---|---|

General Purpose Configuration EEPROMs (1x Microchip 24LC128-I/ST, 3x Microchip 24AA025E48T-I/OT) | Not programmed | - |

| USB3.0 HUB Configuration EEPROM (Microchip 24LC128-I/ST) | Not programmed | - |

| Si5338A programmable PLL NVM OTP | Not programmed | - |

Table 1: Initial Delivery State of the flash memories

Signals, Interfaces and Pins

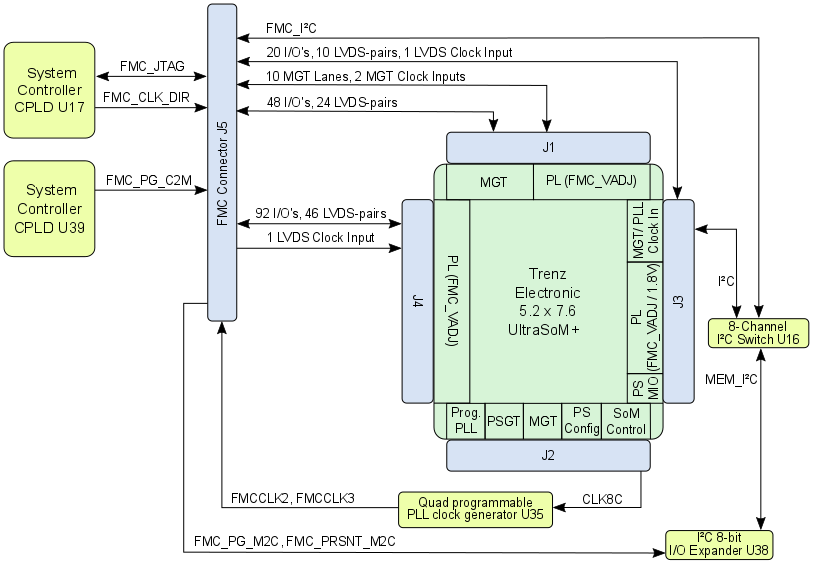

FMC HPC Connector

The FMC (FPGA Mezzanine Card) connector J5 with high pin count (HPC) provides as an ANSI/VITA 57.1 standard a modular interface to the MPSoCs FPGA and exposes numerous of its I/O pins for use by other mezzanine modules and expansion cards.

The connector supports single ended (VCCIO: FMC_VADJ) and differential signaling as the I/O's are usable as LVDS-pairs.

The I/O signals are routed from the FPGA banks as LVDS-pairs to the connector.

Figure 2: FMC HPC Connector

| FPGA Bank | I/O Signal Count | LVDS-pairs count | VCCO bank Voltage | Reference Clock Input from FMC Connector | Notes |

|---|---|---|---|---|---|

| Bank 48 | 20 | 10 | FMC_VADJ | 1 reference clock signal from FMC connector | - |

| Bank 64 | 46 | 23 | FMC_VADJ | 1 reference clock signal from FMC connector | bank's VREF-pin connected to FMC connector pin J5-H1 (VREF_A_M2C) |

| Bank 65 | 46 | 23 | FMC_VADJ | - | bank's VREF-pin connected to FMC connector pin J5-H1 (VREF_A_M2C) |

| Bank 66 | 48 | 24 | FMC_VADJ | - | bank's VREF-pin connected to FMC connector pin J5-H1 (VREF_A_M2C) |

Table 2: FMC connector pin-outs of available logic banks of the MPSoC

The MGT-banks have also clock input-pins which are exposed to the FMC connector. Following MGT-lanes are available on the FMC connectors J5:

| MGT Bank | Type | Count of MGT Lanes | Schematic Names / Connector Pins | MGT Bank's Reference Clock Inputs from FMC Connector |

|---|---|---|---|---|

| 228 | GTH | 4 GTH lanes | B228_RX3_P, B228_RX3_N, pins J5-A10, J5-A11 B228_RX2_P, B228_RX2_N, pins J5-A6, J5-A7 B228_RX1_P, B228_RX1_N, pins J5-A2, J5-A3 B228_RX0_P, B228_RX0_N, pins J5-C6, J5-C7 | 1 reference clock signal (B228_CLK0) from FMC connector |

| 229 | GTH | 4 GTH lanes | B229_RX3_P, B229_RX3_N, pins J5-B12, J5-B13 B229_RX2_P, B229_RX2_N, pins J5-B16, J5-B17 B229_RX1_P, B229_RX1_N, pins J5-A18, J5-A19 B229_RX0_P, B229_RX0_N, pins J5-A14, J5-A15 | 1 reference clock signal (B229_CLK0) from FMC connector |

| 230 | GTH | 2 GTH lanes | B230_RX1_P, B230_RX1_N, pins J5-B4, J5-B5 B230_RX0_P, B230_RX0_N, pins J5-B8, J5-B9 | - |

Table 2: FMC connector pin-outs of available MGT-lanes of the MPSoC

The FMC connector provides pins for reference clock output to the Mezzanine module and clock input to PL banks of the MPSoC:

| Clock Signal Schematic Name | FMC Connector Pins | Direction | Clock Source | Notes |

|---|---|---|---|---|

| B228_CLK0 | J5-D4 / J5-D5 | in | FMC Connector J5 | clock signal to MGT bank 228 |

| B229_CLK0 | J5-B20 / J5-B21 | in | FMC Connector J5 | clock signal to MGT bank 229 |

| FMCCLK2 | J5-K4 / J5-K5 | out | Carrier Board PLL SI5338A U35, CLK2 | - |

| FMCCLK3 | J5-J2 / J5-J3 | out | Carrier Board PLL SI5338A U35, CLK3 | - |

| B64_L14_P / B64_L14_N | J5-H4 / J5-H5 | in | FMC Connector J5 | bank 64 clock capable pin-pair |

| B48_L6_P / B48_L6_N | J5-G2 / J5-G3 | in | FMC Connector J5 | bank 48 clock capable pin-pair |

Table 3: FMC connector pin-outs for reference clock output

The FMC connector provides further interfaces like 'JTAG' and 'I²C' to the System Controller CPLD:

| Interfaces | I/O Signal Count | Pin schematic Names / FMC Pins | Connected to | Notes |

|---|---|---|---|---|

| JTAG | 5 | FMC_TCK, pin J5-D29 FMC_TMS, pin J5-D33 FMC_TDI, pin J5-D30 FMC_TDO, pin J5- D31 | SC CPLD U17, bank 1 | VCCIO: 3V3SB TRST_L, pin J5-D34 pulled-up to 3V3_PER |

| I²C | 2 | FMC_SCL, pin J5-C30 FMC_SDA, pin J5-C31 | I²C Switch U16 | I²C-lines pulled-up to 3V3_PER |

| Control Lines | 3 | FMC_PRSNT_M2C, pin J5-H2 FMC_PG_C2M, pin J5-D1 (3V3_PER pull-up) FMC_PG_M2C, pin J5-F1 (3V3_PER pull-up) FMC_CLK_DIR, pin J5-B1 (pulled-down to GND) | I²C I/O Expander U38 SC CPLD U39, bank 0 I²C I/O Expander U38 SC CPLD U17, bank 1 | 'PG' = 'Power Good'-signal 'C2M' = carrier to (mezzanine) module 'M2C' = (mezzanine) module to carrier |

Table 4: FMC connector pin-outs of available interfaces to the System Controller CPLD

Several VCCIO voltages are available on the FMC connector to operate the I/O's in order of the intended purpose:

| VCCIO Schematic Name | FMC Connector J5 Pins | Notes |

|---|---|---|

| 12V | C35/C37 | extern 12V power supply |

| 3V3_PER | D32/D36/D38/D40/C39 | 3.3V peripheral supply voltage |

| FMC_VADJ | H40/G39/F40/E39 | adjustable FMC VCCIO voltage, supplied by DC-DC converter U8 |

Table 5: Available VCCIO voltages on FMC connector

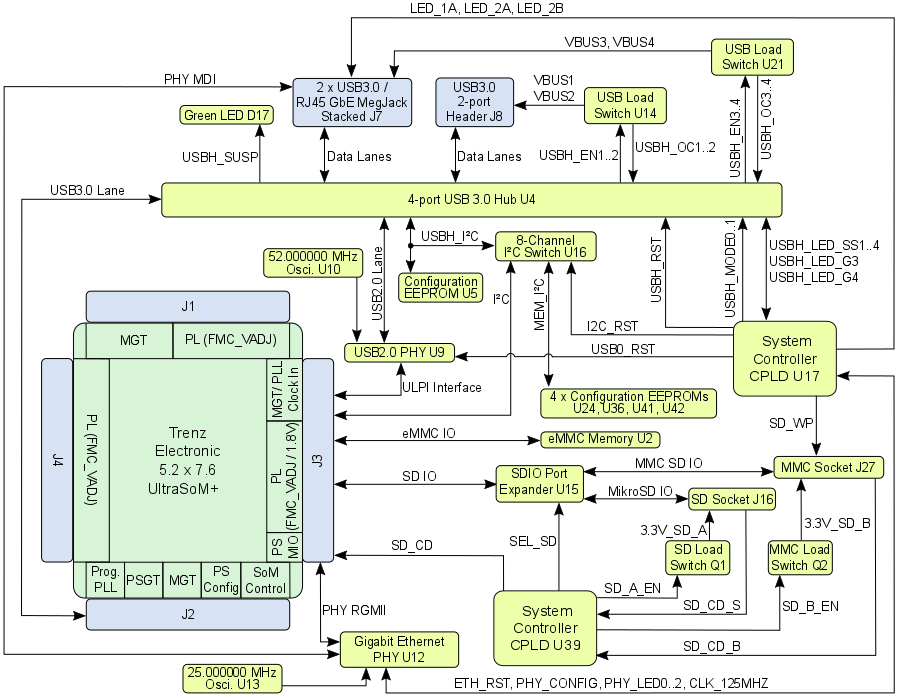

MIO Bank Interfaces

The TEBF0808 carrier board provides several interfaces, which are configured on the MIO banks 500 .. 503 of the Zynq Ultrascale+ MPSoC.

Following table contains the assignment of the MIO pins to the configured interfaces:

| MIO | Configured as | System Controller CPLD | Notes |

|---|---|---|---|

| 0..12 | Dual QSPI | - | Dual Flash Memory on TE0808 SoM; Bootable |

| 13..23 | SD0: eMMC | - | eMMC Memory U2; Bootable |

| 24, 25 | - | CPLD (U39) MUXED | - |

| 26..29 | - | CPLD (U17 MUXED | Bootable JTAG (PJTAG0) possible |

| 30 | force reboot after FSBL-PLL config for PCIe | CPLD (U39) MUXED | - |

| 31 | PCIe reset | CPLD (U39) MUXED | - |

| 32 | - | CPLD (U39) MUXED | - |

| 33 | - | CPLD (U39) MUXED | - |

| 34..37 | - | CPLD (U39) MUXED | - |

| 38, 39 | I2C0 | - | - |

| 40 | forwarded to PWRLED_P / LED_P | CPLD (U39) MUXED | - |

| 41 | - | - | - |

| 42, 43 | UART0 | CPLD (U39) MUXED | - |

| 44 | SD_WP to FPGA | CPLD (U39) MUXED | - |

| 45..51 | SD1: SD | - | Bootable MikroSD / MMC Card |

| 52..63 | USB0 | - | - |

| 64..75 | GEM3 | - | Ethernet RGMII |

| 76, 77 | MDC / MDIO | - | Ethernet RGMII |

Table 5: MIO Assignment

On the carrier board there are up to 4 USB3.0 Super Speed ports available, which are also downward compatible to USB2.0 High Speed ports. The USB3.0 ports are provided by the IC U4, Cypress Semiconductor CYUSB3324 4-port USB3.0 Hub. The pin-strap configuration option of the USB3.0 Hub U4 is disabled, so the Hub will only be configurable over the configuration EEPROM U5. The I²C interface of the EEPROM is also accessible by the MPSoC through I²C switch U16.

On the Upstream-side, this chip is connected to the MGT1 lane of MPSoC's PG GT bank 505 to establish the USB3.0 data lane. For the USB2.0 interface, the USB3.0 HUB U4 is connected to the on-board USB2.0 PHY U9. The USB2.0 PHY U9 is connected per ULPI interface (MIO pins 52..63) to MPSoC's MIO bank 501.

Further interfaces of the MIO bank:

- SDIO port with muxed MikroSD and MMC Socket

- Gigabit Ethernet connected per RGMII

- eMMC Memory

- 4 x user configuration EEPROMs with I²C interface

Following block-diagram visualizes the interfaces of the MIO bank at the Zynq Ultrascale+ MPSoC and their associated on-board peripherals.

Figure 3: TEBF0808 MIO Interfaces

MPSoC's PS GT Bank 505 Interfaces

On the PS GT Bank 505 provides beside the USB3.0 Lane also following interfaces:

- SATA (PS GT bank 505, MGT2 Lane)

- Display-Port (PS GT bank 505, MGT3 Lane, only TX-pair routed)

- PCI Express (PS GT bank 505, MGT0 Lane)

| Function | MGT Lane | Required Ref Clock | Clock Source | Comment |

|---|---|---|---|---|

| PCIe | PS 0 | 100 MHz | Si5345 (CLK0 of prog. PLL on mounted SoM) | - |

| USB3 | PS 1 | 100 MHz | Optional Oscillator U6 | - |

| SATA | PS 2 | 150 MHz | Oscillator U23 | - |

| DP.0 | PS 3 | - | - | Display Port |

Table 6: PS GT Lane Assignment

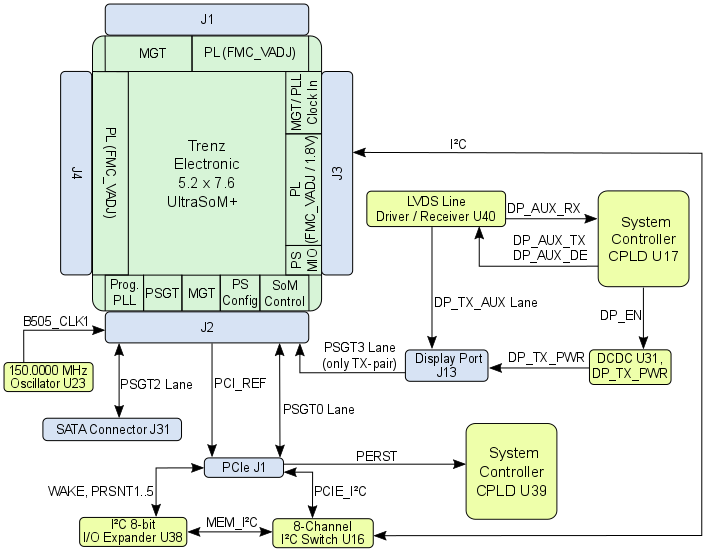

Following block diagram shows the wiring of the MGT Lanes of the PS GT bank 505 to the particular high speed data interfaces:

Figure 4: TEBF0808 PS GT Bank 505 Interface

MGT Interfaces SFP+ and FireFly

The TEBF0808 carrier board provides the high speed MGT interface connectors "SFP+" (Enhanced small form-factor pluggable) and Samtec "FireFly". Each of this connectors are capable of data transmission rates up to 10 Gbit/s.

| Function | MGT Lane | Required Ref Clock | Clock Source | Comment |

|---|---|---|---|---|

| FireFly | B128 MGT Lanes 0..3 | - | - | - |

| SFP | B230 MGT Lane 2 | 125 / 156.25 MHz | Si5345 (CLK7 of prog. PLL on mounted SoM) | - |

| SFP | B230 MGT Lane 3 | 125 / 156.25 MHz | Si5345 (CLK7 of prog. PLL on mounted SoM) | - |

Table 6: MGT Lane Assignment

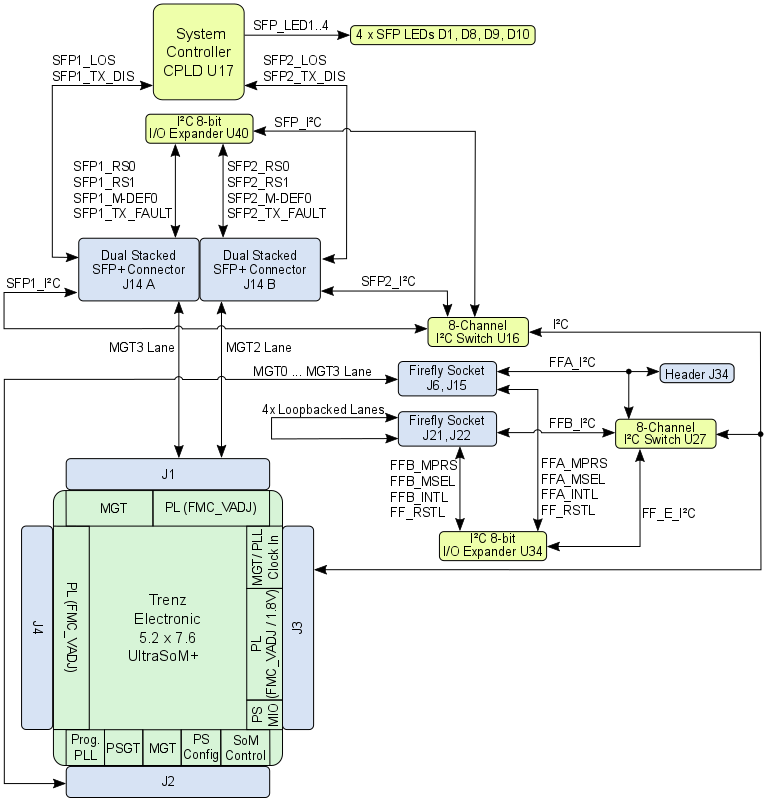

Following block diagram show the wiring of the MGT lanes to the particular interface connectors:

Figure 5: TEBF0808 MGT Interfaces

As shown on the block diagram, the FireFly connector pair J21, J22 provides four reversed looped back MGT lanes. To test any of the on-board MGT lanes or of an extern device, 4 RX/TX differential pairs are bridged on the connector, hence the transmitted data on these MGT lanes flows back to their sources in a loop-back circuit without intentional processing or modification.

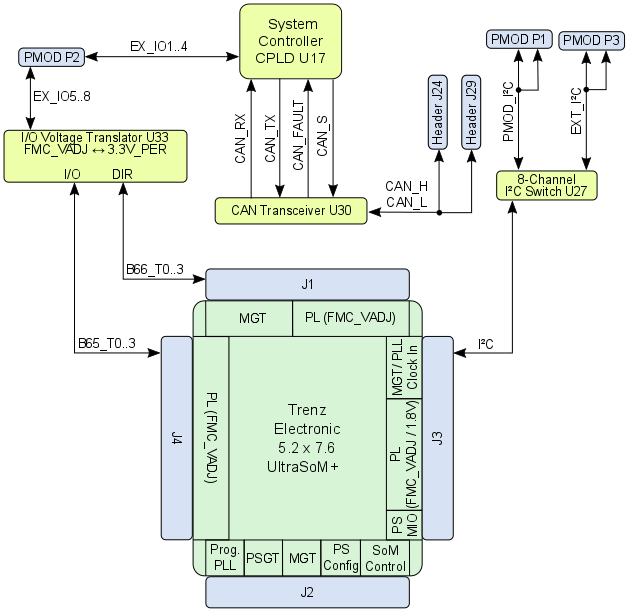

CAN FD Interface and PMOD Connectors

On the carrier board there is a CAN FD (CAN with Flexible Data-Rate) interface available which is accessible on the CAN headers J24 (10-pin IDC connector) or J29 (6-pin header), which are connected to the CAN FD transceiver U30.

Additionally the carrier board provides PMOD connectors with GPIO and I²C interface. Following table

| PMOD | Interface | Connected with | Notes |

|---|---|---|---|

| P1 | GPIO | HP Bank 65 of MPSoC (4 I/O's, B65_T0 ... B65_T3), System Controller CPLD U17 (4 I/O's, EX_IO1 ... EX_IO4) | Voltage translation via IC U33 with direction control, only singled-ended signaling possible |

| P2 | I²C | 8-channel I²C Switch U27 | Accessible on MPSoC's I²C interface through I²C switch U27 |

| P3 | I²C | 8-channel I²C Switch U27 | Accessible on MPSoC's I²C interface through I²C switch U27 |

Table 7: PMOD Pin Assignment

Figure 6: TEBF0808 CAN Interfaces, PMOD

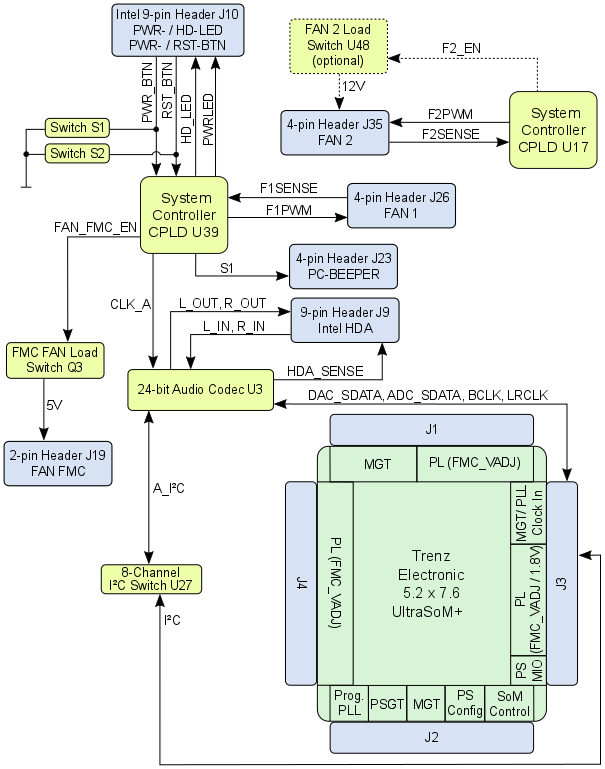

Intel PC Compatible Headers and FAN Connectors

The TEBF0808 carrier board provides with its Mini-ITX form factor the possibility to encase the board in a PC Enclosure. For this purpose, the board is equipped with several Intel PC compatible headers to connect them to the PC Enclosure.

Pins are available for following PC front panel elements

- Reset Button

- Power Button

- Power LED

- Hard Disc (HD) LED

- Intel High Definition Audio (HDA) Jacks

Following table gives an overview about the particular pins of the headers and a description about their functionalities:

| Header | Pin Name | Function | Connected to | Notes |

|---|---|---|---|---|

| J10 | Pin 1, HD LED+ | HD LED Anode | SC CPLD U39 | Reset und Power Switch-pins are also connected to switch buttons S1 and S2 |

| J9 | Pin 1, PORT1L | Microphone Jack Left Microphone Jack Right Audio Out Jack Left Audio Out Jack Right Jack Detect / Mic in Ground | 24-bit Audio Codec IC U3 | - |

| J23 | Pin 1, 3V3SB Pin 4, S1 | 3.3V DC Supply PC compatible Beeper | SC CPLD U39 | - |

| J26 | Pin 1, GND | Ground 12V DC Supply RPM PWM | SC CPLD U39 | 4-wire PWM FAN connector |

| J35 | Pin 1, GND | Ground 12V DC Supply RPM PWM | SC CPLD U39 | 4-wire PWM FAN connector |

| J19 | Pin 1, GND | Ground 5V DC Supply | Load Switch Q3 (5V DC) | 2-wire FAN connector Fan off/on switchable by signal 'FAN_FMC_EN' on SC CPLD U39 |

Table 8: PC compatible Headers

Figure 7: TEBF0808 PC Compatible Headers

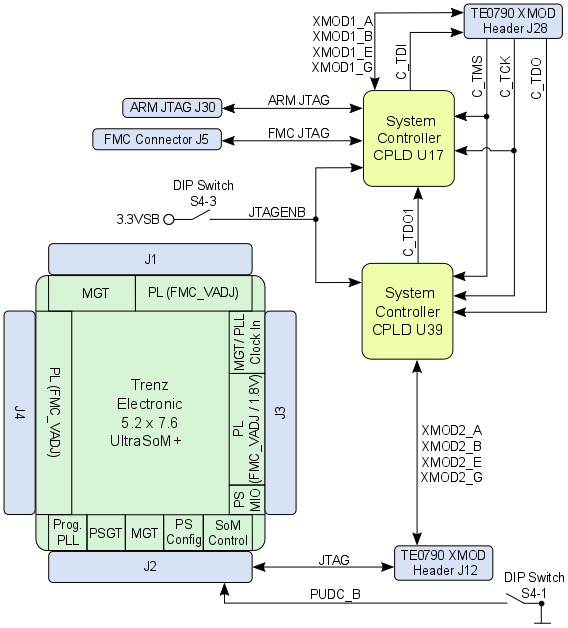

JTAG Interface

The TEBF0808 carrier board provides several JTAG interfaces to program both the System Controller CPLDs and the Zynq Ultrascale+ MPSoC.

Therefore, the board is equipped with two JTAG/UART headers, which have 'XMOD FTDI JTAG Adapter'-compatible pin-assignment. So in use with the XMOD-FT2232H adapter-board TE0790 the mounted SoM and the System Controller CPLDs can be programmed via USB interface.

The System Controller CPLDs will be programmed by the XMOD-Header J28 with cascaded JTAG chain as visualized in Figure 8. To program the System Controller CPLDs, the JTAG interface of these devices have to be activated by DIP-switch S4-3.

The 4 GPIO/UART pins (XMOD1_A/B/E/G) of the XMOD-Header J28 are routed to the System Controller CPLD U17.

XMOD-Header J12 is designated to program the Zynq Ultrascale+ MPSoC via USB interface, the 4 GPIO/UART pins (XMOD2_A/B/E/G) of this header are routed to the System Controller CPLD U39.

Figure 8: TEBF0808 JTAG interfaces

Further JTAG interfaces of the TEBF0808 carrier board are the ARM JTAG 20-pin IDC connector J30 and on the FMC Connector J5. This JTAG interfaces are connected to the System Controller CPLD U17, hence the logical processing and forwarding of the JTAG signals depend on the SC CPLD firmware. The documentation of the firmware of the SC CPLD U17 contains detailed information on this matter.

Boot Process

TE0745 module supports different boot modes which are configurable by the control line 'BOOTMODE' and 'BOOTMODE_1'. The line 'BOOTMODE' is available on B2B connector pin J2-133, the line 'BOOTMODE_1' is connected to the System Controller CPLD on bank 1, pin 21.

The current boot mode will be set by the MIO pins MIO3...MIO5. The control line 'BOOTMODE' is connected to the 'MIO4' pin, 'BOOTMODE_1' to 'MIO5'.

Following table describes how to set the control lines to configure the desired boot mode:

| Boot Mode | MIO5 (BOOTMODE_1) | MIO4 (BOOTMODE) | MIO3 | Note |

|---|---|---|---|---|

JTAG | 0 | 0 | 0 | - |

| NOR | 0 | 0 | 1 | MIO3 pin is shared with QSPI Flash Memory (QSPI-DQ1) |

| NAND | 0 | 1 | 0 | - |

| QSPI Flash Memory | 1 | 0 | 0 | standard mode in current configuration |

| SD-Card | 1 | 1 | 0 | SD-Card on base board necessary |

Table 11: Selectable boot modes

In delivery state of the SoM the boot mode depends on the configured SC-CPLD firmware. The current mode is set to boot from the QSPI Flash Memory.

On-board Peripherals

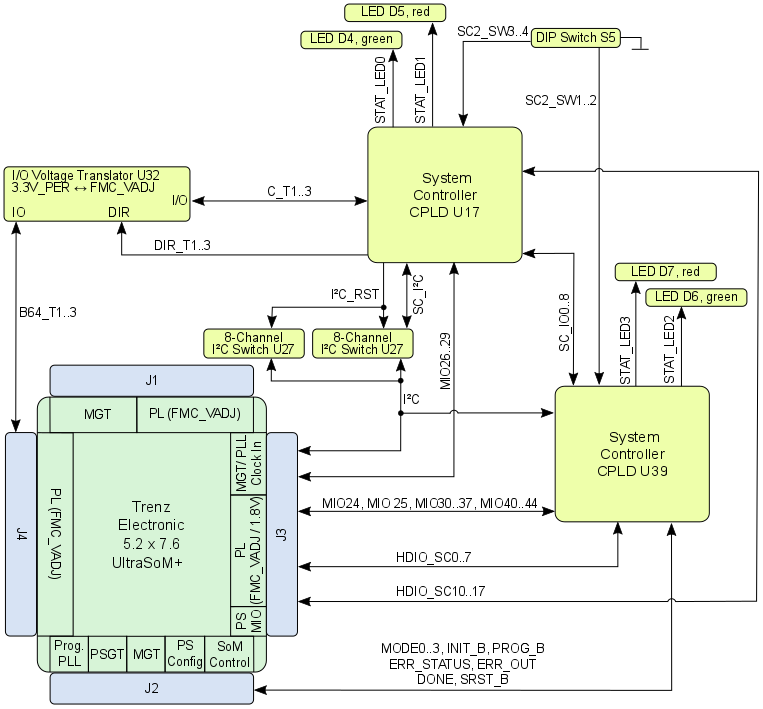

System Controller CPDLs

The TEBF0808 is equipped with two System Controller CPLDs - Lattice Semiconductor LCMXO2-1200HC (MachXO2 Product Family) - with the schematic designators U17 and U39.

The SC-CPLD is the central system management unit where essential control signals are logically linked by the implemented logic in CPLD firmware, which generates output signals to control the system, the on-board peripherals and the interfaces. Interfaces like JTAG and I2C between the on-board peripherals and to the FPGA-module are by-passed, forwarded and controlled by the System Controller CPLD.

Other tasks of the System Controller CPLD are the monitoring of the power-on sequence and to display the programming state of the FPGA module.

Both Sytem Controller CPLDs are connected to the Zynq Ultrascale+ MPSoC through MIO and also Programmable Logic pins.

The functionalities and configuration of the pins depend on the CPLDs' firmware. The documentations of the firmware of SC CPLD U17 and SC CPLD U39 contains detailed information on this matter.

Following block diagram visualizes the connection of the SC CPLDs with the Zynq Ultrascale+ MPSoC via PS (MIO) and PL bank pins.

Figure 8: TEBF0808 System Controller CPLDs

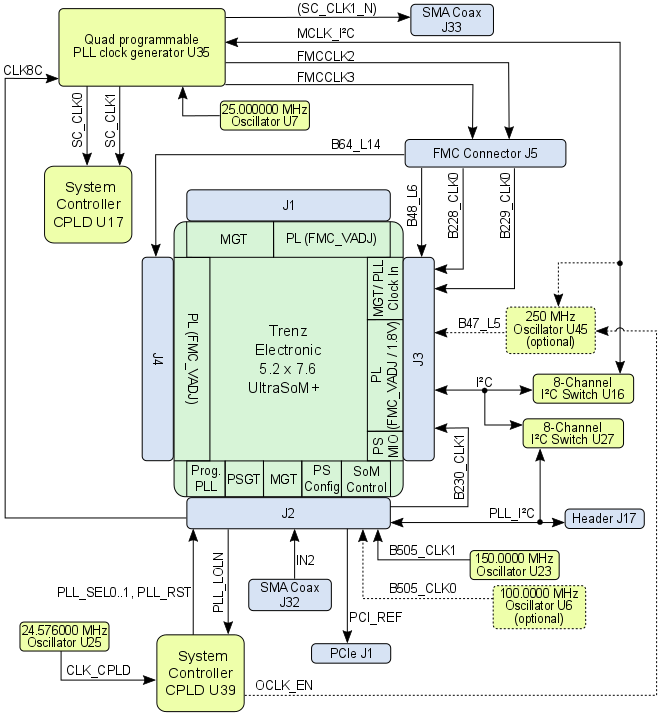

Programmable PLL Clock Generator and Reference Clock Oscillators

The TEBF0808 Carrier Board is equipped with a Silicon Labs I2C programmable quad PLL clock generator Si5338A (U35). It's output frequencies can be programmed by using the I2C bus with address 0x70.

A 25 MHz (U7) oscillator is connected to pin 3 (IN3) and is used to generate the output clocks.

Once running, the frequency and other parameters can be changed by programming the device using the I2C-bus connected through I²C switch U16 between the Zynq module (master) and reference clock signal generator (slave).

| Si5338A (U35) Input | Signal Schematic Name | Note |

|---|---|---|

IN1/IN2 | CLK8_P, CLK8_N | Reference clock signal from Si5345 (CLK8 of prog. PLL on mounted SoM) |

IN3 | reference clock signal from oscillator SiTime SiT8008BI (U7) | 25.000000 MHz fixed frequency. |

IN4/IN6 | pins put to GND | LSB (pin 'IN4') of the default I²C-adress 0x70 not activated. |

IN5 | not connected | - |

| Si5338A (U35) Output | Signal Schematic Name | Note |

CLK0 A/B | SC_CLK0 | Reference clock signal to SC CPLD U17 (single-ended signaling) |

CLK1 A/B | SC_CLK1 | Reference clock signal to SC CPLD U17 (single-ended signaling) |

CLK2 A/B | FMCCLK2_P, FMCCLK2_N | Clock signal routed to FMC connector J5, pins J5-K4 / J5-K5 |

| CLK3 A/B | FMCCLK3_P, FMCCLK3_N | Clock signal routed to FMC connector J5, pins J5-J2 / J5-J3 |

Table 9: Pin description of PLL clock generator Si5338A

Figure 9: Clocking Configuration of TE0808 SoM on TEBF0808 Carrier Board

To configure the programmable PLL clock generator on the mounted TE0808 SoM, refer to the TRM of this SoM.

| Note |

|---|

Si5338 OTP ROM is not programmed by default at delivery, so it is customers responsibility to either configure Si5338 during FSBL or then use SiLabs programmer and burn the OTP ROM with customer fixed clock setup. |

Si5338 OTP can only be programmed two times, as different user configurations may required different setup, TEBF0808 is normally shipped with blank OTP.

For more information Si5338 at SiLabs.

Oscillators

The TEBF0808 carrier board is equipped several on-board oscillators to provide the Zynq Ultrascale+ MPSoC's PS and PL banks and the on-board peripherals with reference clock-signals:

| Clock Source | Schematic Name | Frequency | Clock Input Destination |

|---|---|---|---|

| SiTime SiT8008BI oscillator, U21 | - | 25.000000 MHz | Quad PLL clock generator U16, pin 3 |

SiTime SiT8008BI oscillator, U12 | PS_CLK | 33.333333 MHz | Bank 500 (MIO0 bank), pin B24 |

| SiTime SiT8008BI oscillator, U33 | OTG-RCLK | 52.000000 MHz | USB 2.0 transceiver PHY U32, pin 26 |

| SiTime SiT8008BI oscillator, U9 | ETH_CLKIN | 25.000000 MHz | Gigabit Ethernet PHY U7, pin 34 |

Table 10: Reference clock signal oscillators

High-speed USB ULPI PHY

USB PHY (U32) is provided by USB3320 from Microchip. The ULPI interface is connected to the Zynq PS USB0. I/O voltage is fixed at 1.8V and PHY reference clock input is supplied from the on-board 52.000000 MHz oscillator (U33).

| PHY Pin | ZYNQ Pin | B2B Name | Notes |

|---|---|---|---|

| ULPI | MIO28 ... MIO39 | - | Zynq USB0 MIO pins are connected to the PHY. |

| REFCLK | - | - | 52MHz from on board oscillator (U33). |

| REFSEL[0..2] | - | - | All pins set to GND selects the external reference clock frequency (52.000000 MHz). |

| RESETB | MIO7 | - | Low active USB PHY Reset (pulled-up to PS_1.8V). |

| CLKOUT | MIO36 | - | Set to logic high to select reference clock (oscillator U33) operation mode. |

| DP, DM | - | OTG_D_P, OTG_D_N, pin J2-149 / J2-151 | USB data lines. |

| CPEN | - | VBUS_V_EN, pin J2-141 | External USB power switch active-high enable signal. |

| VBUS | - | USB_VBUS, pin J2-145 | Connect to USB VBUS via a series of resistors, see reference schematics. |

| ID | - | OTG_ID, pin J2-143 | For an A-device connect to the ground. For a B-device, leave floating. |

Table 8: USB PHY interface connections

The schematics for the USB connector and required components is different depending on the USB usage. USB standard A or B connectors can be used for Host or Device modes. A Mini USB connector can be used for USB Device mode. A USB Micro connector can be used for Device mode, OTG Mode or Host Mode.

Gigabit Ethernet PHY

On-board Gigabit Ethernet PHY (U7) is provided with Marvell Alaska 88E1512 IC. The Ethernet PHY RGMII interface is connected to the Zynq Ethernet0 PS GEM0. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from the on-board 25.000000 MHz oscillator (U9). The 125MHz PHY output clock (PHY_CLK125M) is routed to the B2B connector J2 pin 150.

| PHY Pin | ZYNQ PS | B2B | Notes |

|---|---|---|---|

| MDC/MDIO | MIO52, MIO53 | - | - |

| PHY LEDs | - | PHY_LED0: J2-144 | - |

| PHY_LED2 / INTn: | - | J2-148 | Active low interrupt line |

| PHY_CLK125M | - | J2-150 | 125 MHz Ethernet PHY clock out |

| CONFIG | - | - | Permanent logic high |

| RESETn | MIO9 | - | Active low reset line |

| RGMII | MIO16 ... MIO27 | - | Reduced Gigabit Media Independent Interface |

| SGMII | - | - | Serial Gigabit Media Independent Interface |

| MDI | - | PHY_MDI0: J2-120 / J2-122 PHY_MDI1: J2-126 / J2-128 PHY_MDI2: J2-132 / J2-134 PHY_MDI3: J2-138 / J2-140 | Media Dependent Interface |

Table 7: Ethernet PHY interface connections

8-Channel I²C Switches

The I2C interface on B2B connector J2 pins 119 (I2C_33_SCL) and 121 (I2C_33_SDA) have PS_3.3V as reference voltage.

The I2C bus works internally on module with reference voltage 1.8V, on the Zynq chip it is connected to the PS I2C interface via PS MIO bank 500, pins MIO10 and MIO11.

| MIO | Signal Schematic Name | Notes |

|---|---|---|

| 10 | I2C_SCL | 1.8V reference voltage |

| 11 | I2C_SDA | 1.8V reference voltage |

Table 9: MIO-pin assignment of the module's I2C interface

Except the RTC (U24), all I2C slave devices are operating with the reference voltage PS_1.8V via voltage level translating (3.3V ↔ 1.8V) I2C bus repeater (U17).

I2C addresses for on-board devices are listed in the table below:

| I2C Device | I2C Address | Notes |

|---|---|---|

| Zynq chip U1, bank 500 (PS MIO), pins MIO10 (SCL), MIO11 (SDA) | User programmable | Configured as I2C by default |

| Quad programmable PLL clock generator U16: pins 12 (SCL), 19 (SDA) | 0x70 | - |

| MAC Address EEPROM U23, pins 1 (SCL), 3 (SDA) | 0x53 | - |

| SC CPLD U2, bank 2, pins 16 (SDA), 17 (SCL) | User programmable | - |

| RTC, U24 | 0x6F | - |

| RTC RAM, U24 | 0x57 | - |

Table 10: Module's I2C-interfaces overview

System Controller CPLD

The System Controller CPLD (U2) is provided by Lattice Semiconductor LCMXO2-256HC (MachXO2 Product Family). The SC-CPLD is the central system management unit where essential control signals are logically linked by the implemented logic in CPLD firmware, which generates output signals to control the system, the on-board peripherals and the interfaces. Interfaces like JTAG and I2C between the on-board peripherals and to the FPGA-module are by-passed, forwarded and controlled by the System Controller CPLD.

Other tasks of the System Controller CPLD are the monitoring of the power-on sequence and to display the programming state of the FPGA module.

Quad SPI Flash Memory

On-board QSPI flash memory (U14) on the TE0745-02 is provided by Micron Serial NOR Flash Memory N25Q256A with 256 Mbit (32 MByte) storage capacity. This non volatile memory is used to store initial FPGA configuration. Besides FPGA configuration, remaining free flash memory can be used for user application and data storage. All four SPI data lines are connected to the FPGA allowing x1, x2 or x4 data bus widths. Maximum data rate depends on the selected bus width and clock frequency used.

| Note |

|---|

SPI Flash QE (Quad Enable) bit must be set to high or FPGA is unable to load its configuration from flash during power-on. By default this bit is set to high at the manufacturing plant. |

Gigabit Ethernet PHY

On-board Gigabit Ethernet PHY (U7) is provided with Marvell Alaska 88E1512 IC (U8). The Ethernet PHY RGMII interface is connected to the Zynq Ethernet0 PS GEM0. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from an on-board 25.000000 MHz oscillator (U9), the 125MHz output clock signal CLK_125MHZ is connected to the pin J2-150 of B2B connector J2.

High-speed USB ULPI PHY

Hi-speed USB ULPI PHY (U32) is provided with USB3320 from Microchip. The ULPI interface is connected to the Zynq PS USB0 via MIO28..39, bank 501 (see also section). The I/O voltage is fixed at 1.8V and PHY reference clock input is supplied from the on-board 52.000000 MHz oscillator (U33).

MAC Address EEPROM

A Microchip 24AA025E48 serial EEPROM (U23) contains a globally unique 48-bit node address, which is compatible with EUI-48(TM) specification. The device is organized as two blocks of 128 x 8-bit memory. One of the blocks stores the 48-bit node address and is write protected, the other block is available for application use. It is accessible over I2C bus with slave device address 0x53.

RTC - Real Time Clock

An temperature compensated Intersil ISL12020M is used as Real Time Clock (U24). Battery voltage must be supplied to the clock from the base board via pin 'VBAT_IN' (J1-146). Battery backed registers can be accessed over I2C bus at slave address 0x6F. General purpose RAM of the RTC can be accessed at I2C slave address 0x57. RTC IC is supported by Linux so it can be used as hwclock device. The interrupt line 'RTC_INT' of the RTC is connected to System Controller CPLD bank 3 pin 4.

On-board LEDs

LED | Color | Connected to | Description and Notes |

|---|---|---|---|

| D1 | red | DONE signal (PS Configuration Bank 503) | This LED goes ON when power has been applied to the module and stays ON until MPSoC's programmable logic is configured properly. |

Table 14: LED's description

Power and Power-On Sequence

Power Consumption

The maximum power consumption of a module mainly depends on the design which is running on the FPGA.

Xilinx provide a power estimator excel sheets to calculate power consumption. It's also possible to evaluate the power consumption of the developed design with Vivado. See also Trenz Electronic Wiki FAQ.

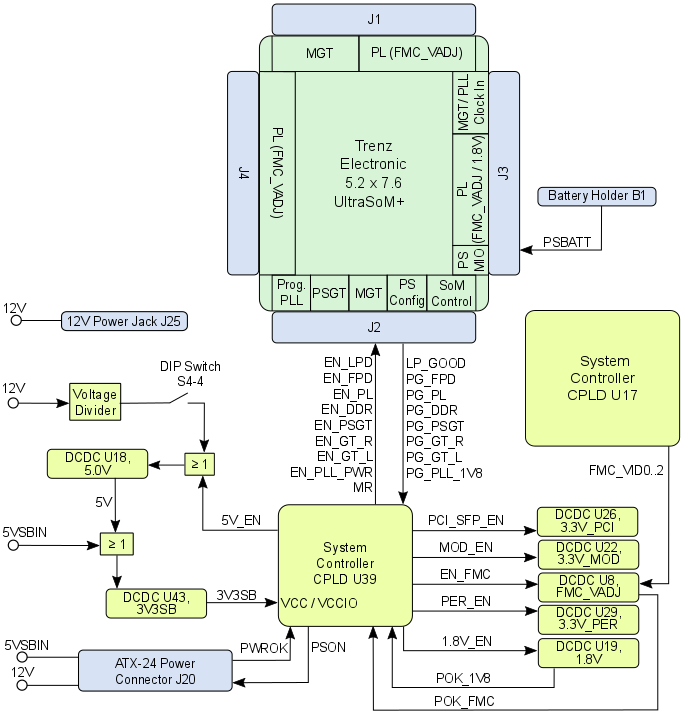

Power Management

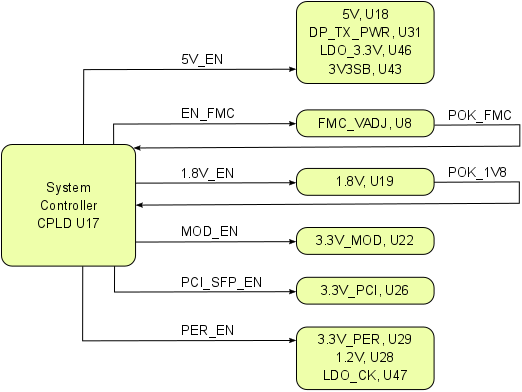

The TEBF0808 carrier board manages both the power-on sequence of the mounted TE0808 SoM and the on-board DC-DC converters via System Controller CPLD U39.

The power-on sequence of the TE0808 SoM is managed by utilizing the SoM's DC-DC converter control signals ('Enable', 'Power-Good'), so the DC-DC converters of the SoM dedicated to the particular Power Domains of the Zynq Ultrascale+ MPSoC will be powerer-up in a specific sequence to meet the recommended criteria to power up the Xilinx Zynq Ultrascale+ MPSoC properly.

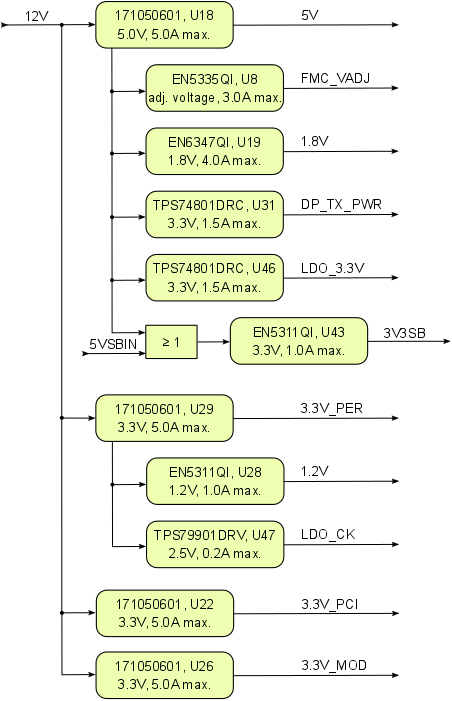

Figure 10: TEBF0808 Power-Management

Adjustable PL Bank VCCO Voltage FMC_VADJ

Power Distribution Dependencies

The power rails 'DCDCIN', 'LP_DCDC', 'PL_DCIN', 'PS_BATT' have to be powered up on the assigned pins of the B2B connectors as listed on the section "Power Rails". Except 'PS_BATT' (see section "Recommended Operation Conditions"), all power-rails can be powered up, with 3.3V power sources, also shared, if Power Domain control is not required.

There are following dependencies how the initial voltages of the power rails on the B2B connectors are distributed to the on-board DCDC converters, which power up further DCDC converters and the particular on-board voltages:

Figure 11: Power Distribution Diagram

| Note |

|---|

Current rating of Samtec Razor Beam™ LSHM B2B connectors is 2.0A per pin (2 adjacent pins powered). |

Power-On Sequence Diagram

The TE0808 SoM meets the recommended criteria to power up the Xilinx Zynq Ultrascale+ MPSoC properly by keeping a specific sequence of enabling the on-board DCDC converters dedicated to the particular Power Domains and powering up the on-board voltages.

The on-board voltages of the TE0808 SoM will be powered-up in order of a determined sequence by activating the above-mentioned power rails and the Enable-Signals of the DCDC converters. The on-board voltages will be powered up at three steps.

- Low-Power Domain (LPD) and on-board Si5345A programmable clock generator supply voltage

- Programmable Logic (PL) and Full-Power Domain (FPD)

- GTH, PS GTR transceiver and DDR memory

Hence, those three power instances will be powered up consecutively and the Power-Good-Signals of the previous instance has to be asserted.

Following diagram clarifies the sequence of enabling the three power instances utilizing the DCDC converter control signals ('Enable', 'Power-Good'), which will power-up in descending order as listed in the blocks of the diagram.

Figure 12: Power-On Sequence Utilizing DCDC Converter Control Signals

| Warning |

|---|

| To avoid any damages to the MPSoC module, check for stabilized on-board voltages in steady state before powering up the MPSoC's I/O bank voltages VCCOx. All I/O's should be tri-stated during power-on sequence. |

Core voltages and main supply voltages have to reach stable state and their "Power Good"-signals have to be asserted before other voltages like bank's I/O voltages (VCCOx) can be powered up.

It is important that all PS and PL I/Os are tri-stated at power-on until the "Power Good"-signals are high, meaning that all on-module voltages have become stable and module is properly powered up.

See Xilinx datasheet DS925 for additional information. User should also check related base board documentation when intending base board design for TE0808 SoM.

Power Rails

Voltages on B2B | B2B J1 Pin | B2B J2 Pin | B2B J3 Pin | B2B J4 Pin | Input/ | Note |

|---|---|---|---|---|---|---|

| PL_DCIN | J1-151, J1-153, J1-157, J1-159 | - | - | - | Input | - |

| DCDCIN | - | J2-154, J2-156, J2-158, J2-160, | - | - | Input | - |

| LP_DCDC | - | J2-138, J2-140, J2-142, J2-144 | - | - | Input | - |

| PS_BATT | - | J2-125 | - | - | Input | - |

| GT_DCDC | - | - | J3-157, J3-158, J3-159, J3-160 | - | Input | - |

| PLL_3V3 | - | - | J3-152 | - | Input | U5 (programmable PLL) 3.3V nominal input |

| SI_PLL_1V8 | - | - | J3-151 | - | Output | Internal voltage level 1.8V nominal output |

| PS_1V8 | - | J2-99 | J3-148 | - | Output | Internal voltage level |

| PL_1V8 | J1-91, J1-121 | - | - | - | Output | Internal voltage level |

| DDR_1V2 | - | J2-135 | - | - | Output | Internal voltage level |

Table 17: Power rails of the MPSoC module on accessible connectors

B2B connectors

| Include Page | ||||

|---|---|---|---|---|

|

Technical Specifications

Absolute Maximum Ratings

Parameter | Min | Max | Unit | Notes / Reference Document |

|---|---|---|---|---|

| PL_DCIN | -0.3 | 7 | V | TPS82085SIL / EN63A0QI data sheet |

| DCDCIN | -0.3 | 7 | V | TPS82085SIL / TPS51206 data sheet |

| LP_DCDC | -0.3 | 4 | V | TPS3106K33DBVR data sheet |

| GT_DCDC | -0.3 | 7 | V | TPS82085SIL data sheet |

| Note |

|---|

| Assembly variants for higher storage temperature range are available on request. |

Recommended Operating Conditions

| Parameter | Min | Max | Unit | Notes / Reference Document |

|---|---|---|---|---|

| PL_DCIN | 2.5 | 6 | V | EN63A0QI / TPS82085SIL data sheet |

| DCDCIN | 3.1 | 6 | V | TPS82085SIL / TPS51206PSQ data sheet |

| LP_DCDC | 2.5 | 3.6 | V | TPS82085SIL / TPS3106 data sheet |

Operating Temperature Ranges

Commercial grade: 0°C to +70°C.

Industrial grade: -40°C to +85°C.

Extended grade: 0°C to +85°C.

The module operating temperature range depends also on customer design and cooling solution. Please contact us for options.

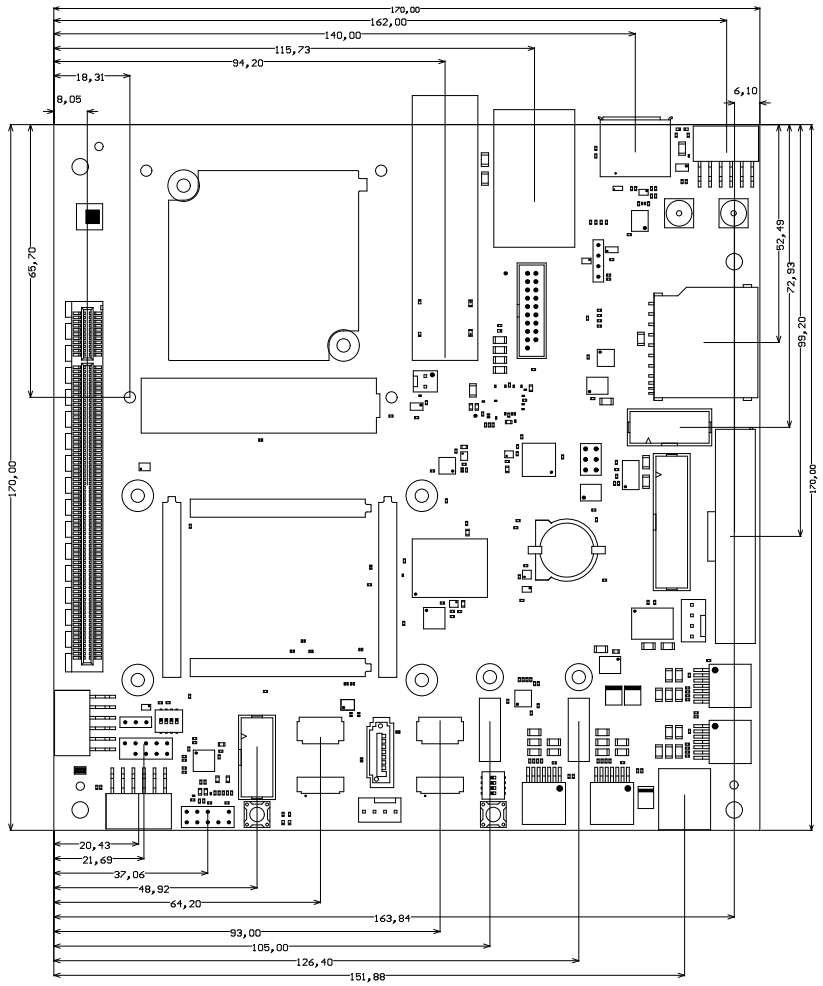

Physical Dimensions

Module size: 52 mm × 76 mm. Please download the assembly diagram for exact numbers

Mating height with standard connectors: 4mm

PCB thickness: 1.6mm

Highest part on PCB: approx. 3mm. Please download the step model for exact numbers

All dimensions are given in millimeters.

Revision History

Hardware Revision History

| Date | Revision | Notes | Link to PCN | Documentation Link |

|---|---|---|---|---|

| - | 04 | First production silicon | - | - |

| - | 03 | Second ES production release | - | TEBF0808-03 |

| - | 02 | First ES production release | - | TEBF0808-02 |

| - | 01 | Prototypes | - | - |

Hardware revision number is written on the PCB board together with the module model number separated by the dash.

Document Change History

| Date | Revision | Contributors | Description | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Ali Naseri | Initial document |

Disclaimer

| Include Page | ||||

|---|---|---|---|---|

|