Page History

...

Additional assembly options are available for cost or performance optimization upon request.

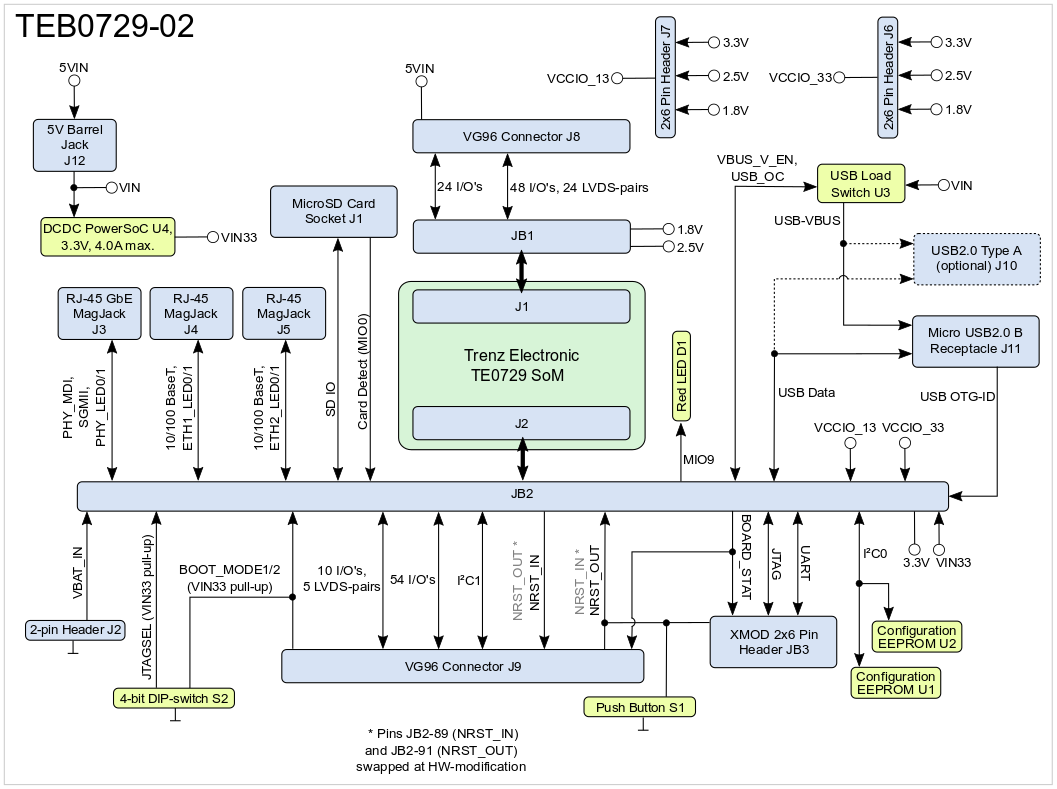

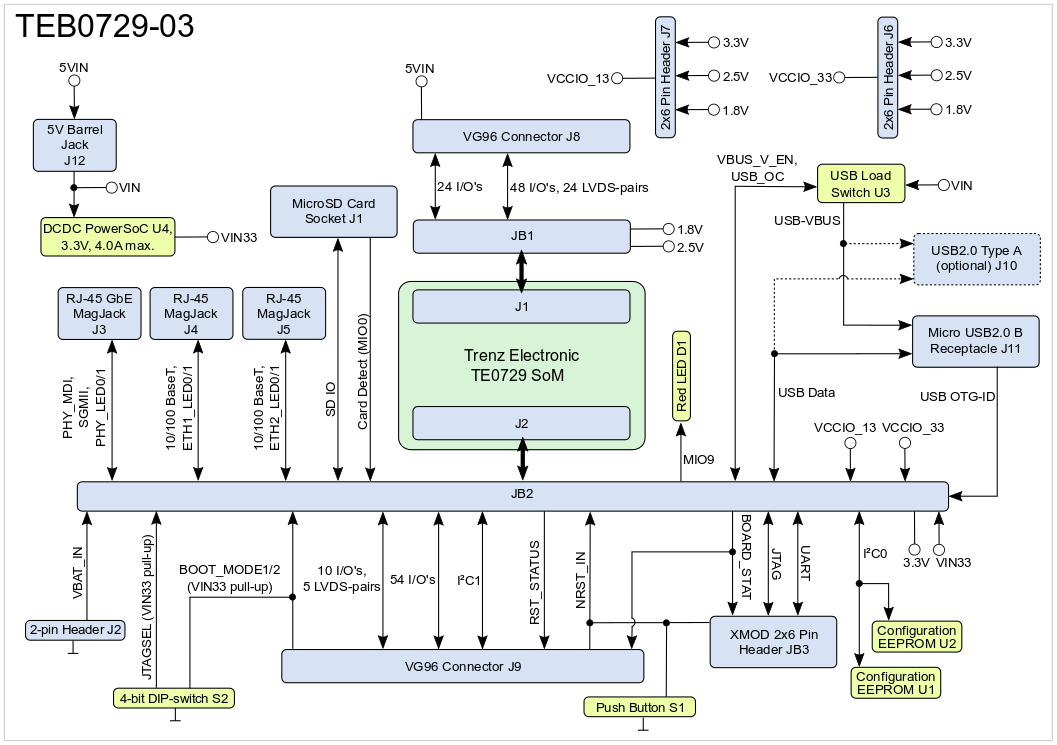

Block Diagram

Figure 1: TEB0729-02 03 block diagram.

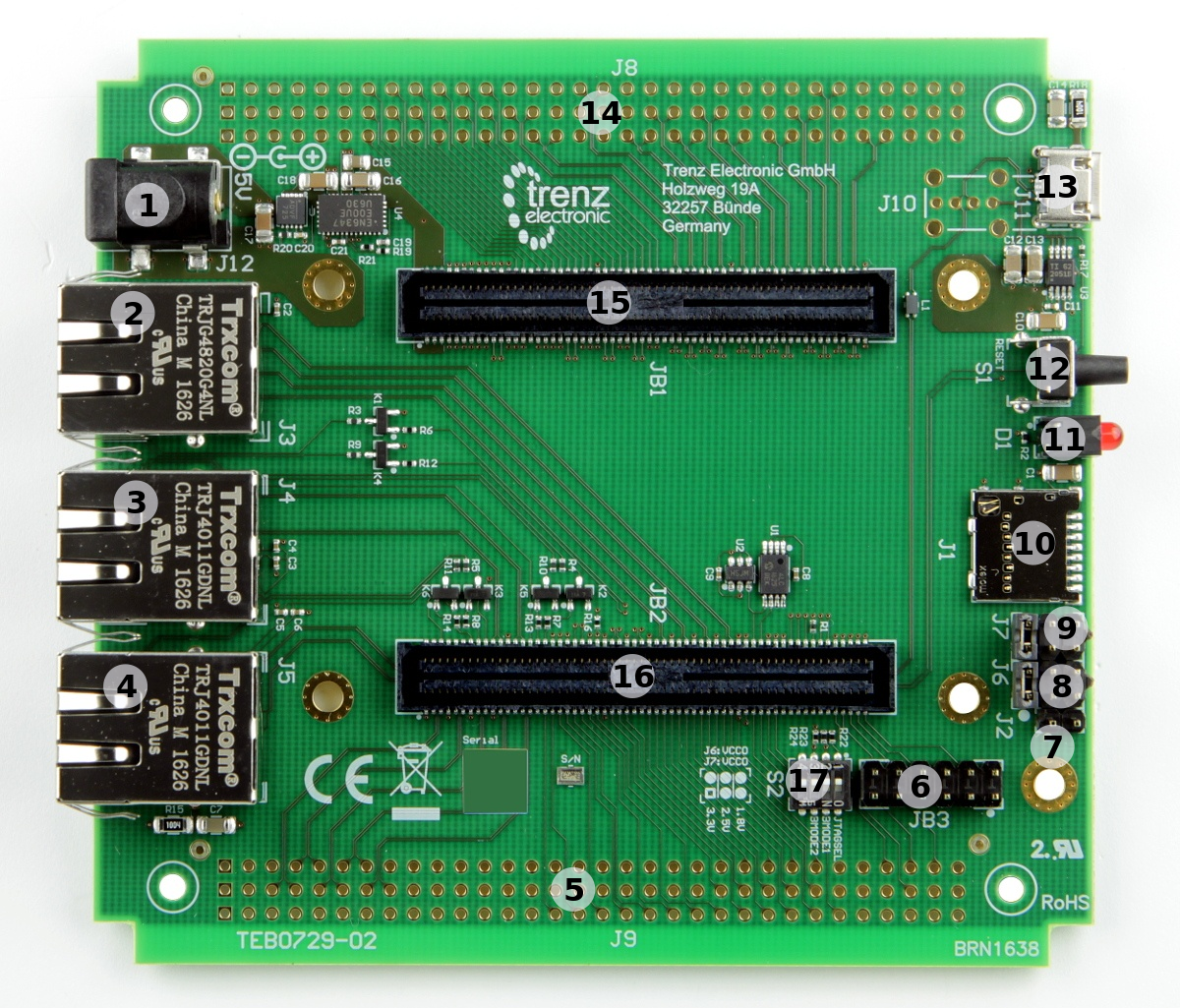

Main Components

Figure 2: TEB0729-02 03 main components (picture shows PCB REV02).

- 5V barrel jack, J12

- RJ-45 Gigabit Ethernet MegJack, J3

- RJ-45 10/100-BaseT Ethernet MegJack, J4

- RJ-45 10/100-BaseT Ethernet MegJack, J5

- VG96 connector placeholder, J9

- XMOD (TE0790) header, JB3

- 2-pin header for VBAT-IN supply-voltage, J2

- 2x6 pin header for setting VCCIO_33, J6

- 2x6 pin header for setting VCCIO_13, J7

- MicroSD Card socket, J1

- Red LED, D1

- Push Button, S1

- Micro USB2.0 B Receptacle (optional USB2.0 Type A socket)

- VG96 connector placeholder, J8

- B2B Connector, JB1

- B2B Connector, JB2

- 4-bit DIP-switch, S2

...

| B2B Connector | Interfaces | Count of IO's | Notes |

|---|---|---|---|

| JB1 | User IO | 24 single ended | - |

| 48 single ended or 24 differential | - | ||

| JB2 | User IO | 54 single ended | - |

| 10 single ended or 5 differential | - | ||

| I²C | 2 | - | |

| SD IO | 7 | - | |

| UART | 2 | - | |

| USB2.0 | 6 | - | |

| 2x 10/100-BaseT Ethernet | 1412 | - | |

| GbE MDI and SGMII | 14 | - | |

| JTAG | 4 | - |

...

On the VG96 connector J9 are signals assigned to control the SoM and the interfaces of the SoM's Zynq chip device and of its on-module peripherals:

...

| VG96 Connector | Control Signals and Interfaces | Count of IO's | Notes |

|---|---|---|---|

| J8 | User IO | 24 single ended | - |

| 48 single ended or 24 differential | - | ||

| J9 | User IO | 54 single ended | - |

| 10 single ended or 5 differential | - | ||

| 'NRST_IN' (pin J9-A29), 'NRSTRST_OUTSTATUS' , pins (pin J9-A29, J9-B30) | 2SoM reset signals 1) | These pins are dedicated to the specific Reset-functionality of the TE0729 SoM. | |

| 'BOARD_STAT' , pins (pin J9-B32) | 1 | - | |

| 'BOOT_MODE1' (pin J9-C31), 'BOOT_MODE2' , pins (pin J9-C31, J9-C32) | 2 | Binary bootmode code of SoM, also connected to DIP S2 | |

| I²CI²C, pins J9-A30, J9-A31 | 2 | I²C1 interface of module | |

| GbE SGMII | 4 | SGMII interface of on-module GbE PHY |

Table 3: General overview of PL I/O signals, SoM's interfaces and control signals connected to the VG96 connectors.

HW-modification Concerning Reset-Signals

1) The pins with the schematic net names 'NRST_IN' (JB2-89) and 'NRST_OUT' (JB2-91) are swapped as part of a HW-modification to rework the Reset-signals of the Carrier-Board in conjunction with the TE0729 SoM.

Refer to the SC CPLD documentation, section "Watchdog" to get further detailed information about the Reset-functionality of the Carrier Board and SoM before and after the HW-modification and the required SC CPLD firmware revision of the TE0729 SoM for each version of the SoM.

JTAG Interface

JTAG Interface

JTAG access to the mounted SoM is provided through B2B connector JB2 and is also routed to the XMOD header JB3. JTAG access to the mounted SoM is provided through B2B connector JB2 and is also routed to the XMOD header JB3. With the TE0790 XMOD USB2.0 to JTAG adapter, the Zynq chip device on the mounted SoM can be programed via USB2.0 interface.

...

The SD IO interface of the SoM's Zynq chip device (MIO-bank) is routed to the on-board MicroSD Card socket J1. By this interface, the Zynq chip device can be booted from an inserted MicroSD Card:

...

The TEB0729 Carrier Board is equipped with a Micro USB2.0 B (receptacle) socket J11 with board-revision TEB0729-0203B, USB2.0 Type A socket is fitted on board-revision TEB0729-0203A.

The differential data signals of the USB2.0 socket are routed to the B2B connector JB2, where they can be accessed by the USB2.0 transceiver of the mounted SoM. The USB2.0 connector can be used for Device mode, OTG Mode or Host Modes. For USB Host mode, the Carrier Board is additionally equipped with a power distribution switch U3 to provide the USB2.0 interface with the USB supply voltage USB-VBUS with nominal value of 5V. OTG mode is not available with USB2.0 Type A socket.

...

| 10/100-BaseT PHY Signal Schematic Name | B2B | Connected to | Notes | ||||

|---|---|---|---|---|---|---|---|

| ETH1_RX_P | JB2-26 | J4-3 | - | ||||

| ETH1_RX_N | JB2-28 | J4-6 | - | ||||

| ETH1_TX_P | JB2-20 | J4-1 | - | ||||

| ETH1_TX_N | JB2-22 | J4-2 | - | ||||

| ETH1_CTREF | JB2-30 | J4-4, J4-5 | Centre Tap Reference point | ETH1_LED0 | JB2-34 | Yellow MegJack J4 LED | - |

| ETH1_LED1 | JB2-32 | Green MegJack J4 LED | - | ||||

| ETH2_RX_P | JB2-8 | J5-3 | - | ||||

| ETH2_RX_N | JB2-10 | J5-6 | - | ||||

| ETH2_TX_P | JB2-2 | J5-1 | - | ||||

| ETH2_TX_N | JB2-4 | J5-2 | - | ETH2_CTREF | JB2-18 | J5-4, J5-5Centre Tap Reference point | |

| ETH2_LED0 | JB2-16 | Yellow MegJack J5 LED | - | ||||

| ETH2_LED1 | JB2-14 | Green MegJack J5 LED | - |

...

| JB3 pin | Signal Schematic Net Name | B2B | Note |

|---|---|---|---|

| C (pin 4) | TCK | JB2-119 | - |

| D (pin 8) | TDO | JB2-117 | - |

| F (pin 10) | TDI | JB2-115 | - |

| H (pin 12) | TMS | JB2-113 | - |

| A (pin 3) | USART0_TX | JB2-96 | - |

| B (pin 7) | USART0_RX | JB2-94 | - |

| E (pin 9) | BOARD_STAT | JB2-112 | also connected to VG96 connector pin J9-B32 |

| G (pin 11) 2) | NRST_IN 2) | JB2-89 | also connected to VG96 connector pin J9-A29 |

Table 12: XMOD header signals and connections. 2) Swapped at HW-Modification with signal 'NRST_OUT' in board-revision 2 Pin connected to push button S1 on XMOD FTDI JTAG Adapter

When using XMOD FTDI JTAG Adapter TE0790, the adapter-board's VCC and VCCIO will be sourced by the Carrier Board. Set the DIP-switch with the setting:

...

| Note |

|---|

Use Xilinx compatible TE0790 adapter board (designation TETE0790-0790-xx with out 'L') to program the Zynq device. The TE0790 adapter board's CPLD have to be configured with the Standard variant of the firmware. Refer to the TE0790 Resources Site for further information and firmware download. |

...

| DIP-switches S2 | Signal Schematic Net Name | Function | Note |

|---|---|---|---|

| S2-1 | JTAGSEL | Select Zynq chip device or SC CPLD programming of mounted SoM: OFF: Zynq device in JTAG chain | Refer also to the TE0729 SC CPLD documentation for detailed information about JTAG update |

| S2-2 | BOOT_MODE1 | Select first bit of boot mode code | Refer to TE0729 TRM and SC CPLD documentation for detailed information about boot modes |

| S2-3 | BOOT_MODE2 | Select second bit boot mode code | |

| S2-4 | x | x | not used |

Table 14: DIP-Switch S2 SoM configuration settings

| Boot Modes Configuration via DIP-switch S2 with default TE7029 CPLD FirmwareMode | S2-2 | S2-3 |

|---|---|---|

| JTAG | ON | ON |

| SD | OFF | OFF |

| QSPI | ON | OFF |

Table 15: Bootmode Boot Modes configuration via DIP-switch S2 with default TE0729 CPLD Firmware

VCCIO

...

Selection Jumper

The Carrier Board VCCIO for the PL IO-banks of the mounted SoM are selectable by the jumpers J6 and J7.

...

The maximum power consumption of the Carrier Board depends mainly on the mounted SoM's FPGA design running on the Zynq chipdevice.

Xilinx provide a power estimator excel sheets to calculate power consumption. It's also possible to evaluate the power consumption of the developed design with Vivado. See also Trenz Electronic Wiki FAQ.

...

Figure 3: Board power distribution diagram.

Power Rails

The voltage direction of the power rails is directed at on-board connectors' view:

| Module Connector (B2B) Designator | VCC / VCCIO | Direction | Pins | Notes |

|---|---|---|---|---|

| JB1 | VIN33 | Out | 1, 2, 3, 4, 5, 6 | 3.3V module supply voltage |

| VCCIO_13 | Out | 101, 102 | PL IO-bank VCCIO | |

| VCCIO_33 | Out | 29, 30 | PL IO-bank VCCIO | |

| 3.3V | In | 65, 66 | voltage output from module | |

| JB2 | 1.8V | In | 49 | voltage output from module |

| 2.5V | In | 13 | voltage output from module | |

| USB-VBUS | Out | 107 | USB Host supply voltage | |

| VBAT_IN | Out | 118 | RTC buffer voltage |

...

| Jumper / Header Designator | VCC / VCCIO | Direction | Pins | Notes |

|---|---|---|---|---|

| J6 | VCCIO_33 | OutIn | 2, 4, 6 | - |

| 1.8V | InOut | 5 | - | |

| 2.5V | InOut | 3 | - | |

| 3.3V | InOut | 1 | - | |

| J7 | VCCIO_13 | OutIn | 2, 4, 6 | - |

| 1.8V | InOut | 5 | - | |

| 2.5V | InOUt | 3 | - | |

| 3.3V | InOut | 1 | - |

Table 20: Power Pin description of VCCIO selection jumper pin header.

...

| Main Power Jack and Pins Designator | VCC / VCCIO | Direction | Pins | Notes |

|---|---|---|---|---|

| J12 | 5VIN | In | -1 | - |

| J9 | 5VIN | In / Out | A1, A2 | also usable as '5VIN' power supply to the Carrier Board as alternative to J12 |

| J2 | VBAT_IN | In | 1 | Attention: Pin 2 connected to ground. VBAT_IN voltage on this pin cause short-circuit. |

...

| Peripheral Socket Designator | VCC / VCCIO | Direction | Pins | Notes |

|---|---|---|---|---|

| J10 / J11 | USB-VBUS | In / Out | 1 | Direction depends on USB2.0 Type A socket / Micro USB2.0 B socketmode |

| J1 | VIN33 | Out | 4 | MikroSD Card socket VDD |

...

The TE0729 module has two 120-pin double-row REF-189019-02 connectors on the bottom side which are compatible with Samtec BSE-060-01-L-D-A connectors. Mating connectors on the baseboard are REF-189019-01, which are compatible with Samtec BTE-060-01-L-D-A connectors.

Order | REF Number | Samtec Number | Type | Mated Height | Data sheet |

|---|

| Comment | ||||||

|---|---|---|---|---|---|---|

| - | REF-189019-02 | BTE-060-01-L-D-A-K-TR | Module connector | 5 mm | http://suddendocs.samtec.com/catalog_english/bte.pdf | Standard connector used on module |

| 26663 | REF-189019- |

| 01 |

| BSE-060-01-L-D-A |

| -TR |

| Baseboard connector | 5 mm | http://suddendocs.samtec.com/catalog_english/ |

| bse.pdf | Standard connector used on |

used on board

| board |

Table 24: B2B Connectors.

| Connector Specifications | Value |

|---|---|

| Insulator material | Liquid crystal polymer |

| Stacking height | 5 mm |

| Contact material | Phosphor-bronze |

| Plating | Au or Sn over 50 μ" (1.27 μm) Ni |

| Current rating | 2 A per pin (1 pin powered per row) |

| Operating temperature range | -55 °C to +125 °C |

| Voltage rating | 225 VAC with 5 mm stack height |

| Max cycles | 100 |

| RoHS compliant | Yes |

Table 25: B2B Connector specificationsTable 24: B2B Connectors.

Variants Currently In Production

| Module Variant | Operating Temperature | USB Socket | Temperature Range |

|---|---|---|---|

| TEB0729-0203-A | -40°C to +125°C | USB2.0 Type A socket fitted | Industrial |

| TEB0729-0203-B | -40°C to +125°C | Micro USB2.0 B socket fitted | Industrial |

Table 2526: Module Board variants.

Technical Specifications

...

Parameter | Min | Max | Units | Reference Document |

|---|---|---|---|---|

5VIN supply voltage | -0.3 | 7 | V | MP5010A, EN6347QI data sheet |

Storage temperature | -65 | 150 | °C | - |

Table 2627: Module absolute maximum ratings.

...

| Parameter | Min | Max | Units | Reference Document |

|---|---|---|---|---|

| 5VIN supply voltage | 4.75 | 5.25 | V | USB2.0 specification concerning 'VBUS' voltage |

| Operating temperature | -40 | 125 | °C | - |

Table 2728: Module recommended operating conditions.

...

| Date | Revision | Notes | PCN | Documentation Link |

|---|---|---|---|---|

| - | 01 |

| - | TEB0729-01 |

| - | 02 |

| - | TEB0729-02 |

| - | 03 |

| - | TEB0729-03 |

Table 29Table 28: Module hardware revision history.

...

Date | Revision | Contributors | Description | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Ali Naseri |

| |||||||||

2017-10-27 | v.14 | Ali Naseri |

|

Table 2930: Document change history.

...