Page History

...

| HTML |

|---|

<!-- Template Revision 1.66 (HTML comments will be not displayed in the document, no need to remove them. For Template/Skeleton changes, increase Template Revision number. So we can check faster, if the TRM style is up to date). --> |

| Scroll Ignore |

|---|

Download PDF version of this document. |

| HTML |

|---|

<!-- General Notes: If some section is CPLD firmware dependent, make a note and if available link to the CPLD firmware description. It's in the TE shop download area in the corresponding module -> revision -> firmware folder. --> |

...

| Scroll pdf ignore | |

|---|---|

Table of Contents

|

Overview

| HTML |

|---|

<!--

Wiki Link: Go to Base Folder of the Module or Carrier, for example : https://wiki.trenz-electronic.de/display/PD/TE0712

--> |

| Scroll Only (inline) |

|---|

Refer to https://wiki.trenz-electronic.de/display/PD/TEB0911+TRM for the current online version of this manual and other available documentation. |

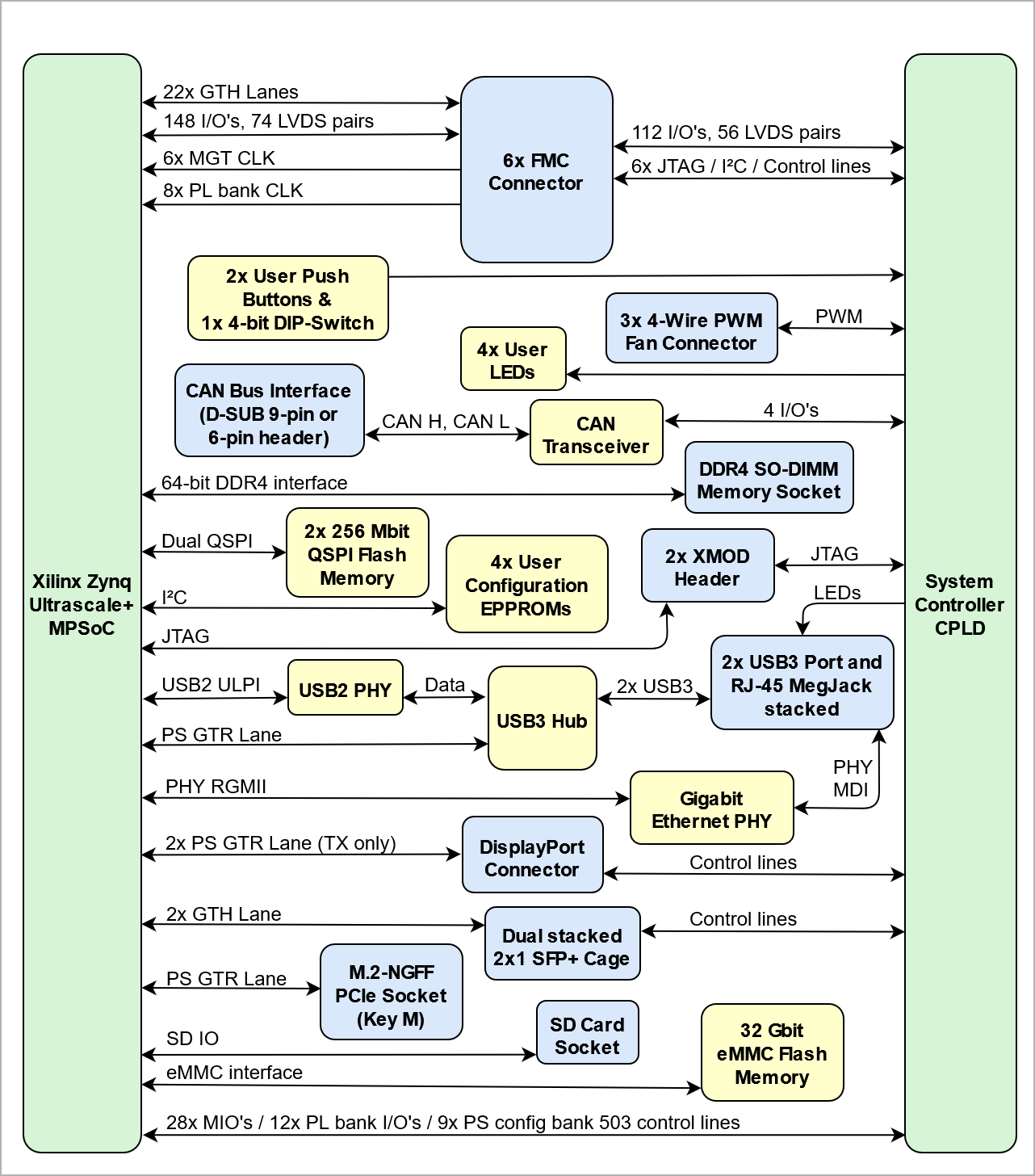

The Trenz Electronic TEB0911 UltraRack+ board is an industrial-grade motherboard integrating a Xilinx Zynq UltrascaleUltraScale+ MPSoC with 4 GByte Flash memory for configuration and operation, DDR4-SDRAM SODIMM SO-DIMM socket with 64-bit wide data bus, 24 22 MGT Lanes lanes and powerful switch-mode power supplies for all on-board voltages.. The motherboard TEB0911 board exposes the pins of the Zynq MPSoC 's pins to accessible connectors and provides a whole range of on-board components to test and evaluate the Zynq UltrascaleUltraScale+ MPSoC and for developing purposes. The motherboard board is capable to be fitted to a dedicated enclosure. On , whereby on the enclosure's rear and front panel, I/O's, LVDS-pairs and MGT interfaces lanes are accessible through 6 on-board FMC connectors and other standard high-speed interfaces for , namely USB3.0, SFP+, SSD, GbE, etc.

Key Features

| HTML |

|---|

<!--

Use short link the Wiki Ressource page: for example:

http://trenz.org/te0720-info

List of available short links: https://wiki.trenz-electronic.de/display/CON/Redirects

--> |

| Scroll Only (inline) |

|---|

Refer to http://trenz.org/teb0911-info for the current online version of this manual and other available documentation.

|

Key Features

- Zynq UltraScale+ MPSoC

- ZU6,ZU9 or ZU15 on 1156 Pin Package

- 64bit DDR4 SODIMM (PS connected)

- M2 PCIe SSD (1-Lane)

- eMMC (bootable)

- Dual QSPI Flash (bootable)

- System Controller(LCMXO2-7000HC)

- Power Sequencing

- IO Expander

- Configurable PLLs

- GTH/GTP Reference CLKs

Front Panel

- 4 x FMC

- 4 GTH per FMC

- 68 ZynqMP PL IO per FMC

- DisplayPort (2-Lanes)

- RJ34 ETH + Dual USB3 Combo

- Dual Stack SFP+

- SD (bootable)

- Status LEDs

Back Panel

- 2 x FMC

- 4/2 GTH

- 12 ZynqMP PL IO per FMC

- 56 SC IO per FMC

- USB JTAG/UART ZynqMP

- USB JTAG/GPIO FMC

- CAN FD (DB9 Connector)

- SMA (external CLK)

- 5polig 24V power connector

- Single 24V main power supply

- Motherboard fitted to dedicated enclosure from Trenz ??

- 2x USB3.0 A Connector (Superspeed Host Port (Highspeed at USB2.0))

- Gigabit Ethernet RGMII PHY with RJ45 MegJack

- Dual SFP+ Connector (2x1 Cage)

- DDR4-SDRAM SODIMM socket (64bit bus width)

- SSD (Solid State Disk) Connector

- CAN FD Transceiver (10 Pin IDC connector and 6-pin header)

- 1x DisplayPort

- 4x On-board configuration EEPROMs (1x Microchip 24LC128-I/ST, 3x Microchip 24AA025E48T-I/OT)

- All carrier board peripherals' I²C interfaces muxed to MPSoC's I²C interface

- 6x FMC HPC Connectors

- 6x FMC Fans

- 3x Optional 4-wire PWM fan connectors

- 10 output programmable PLL clock generator Si5345A

- Quad programmable PLL clock generator SI5338A

- 1x SMA coaxial connectors for reference clock signal input

- MicroSD-Socket (bootable)

- 32 Gbit (4 GByte) on-board eMMC flash (8 banks a 4 Gbit)

- System Controller CPLD Lattice MachXO2 7000 HC

- 2x JTAG/UART header ('XMOD FTDI JTAG Adapter'-compatible) for programming MPSoC and SC CPLD

- On-board DC-DC PowerSoCs and LDOs

Additional assembly options are available for cost or performance optimization upon request.

Block Diagram

...

| Scroll Title | ||||

|---|---|---|---|---|

|

...

|

...

|

...

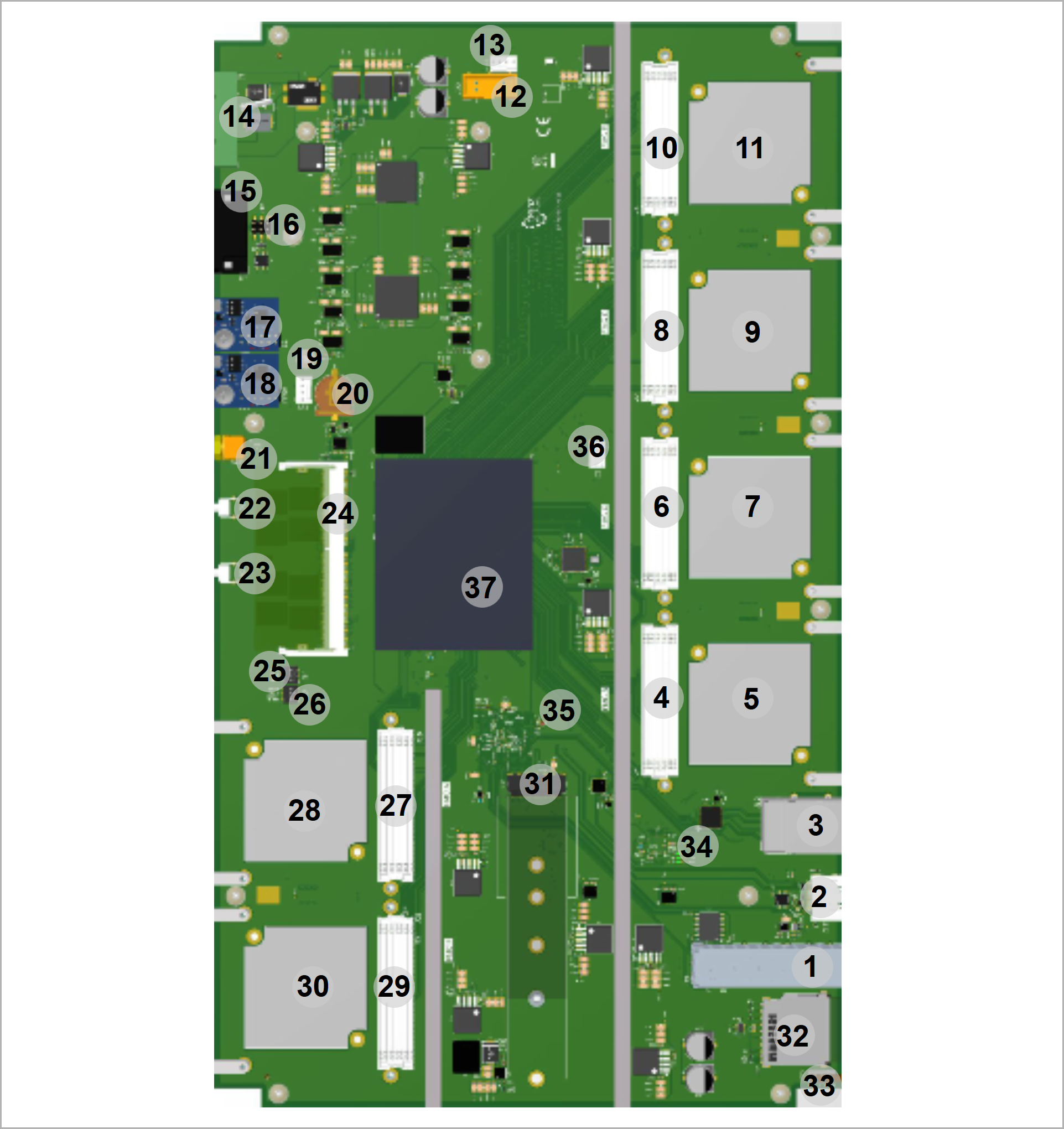

Main Components

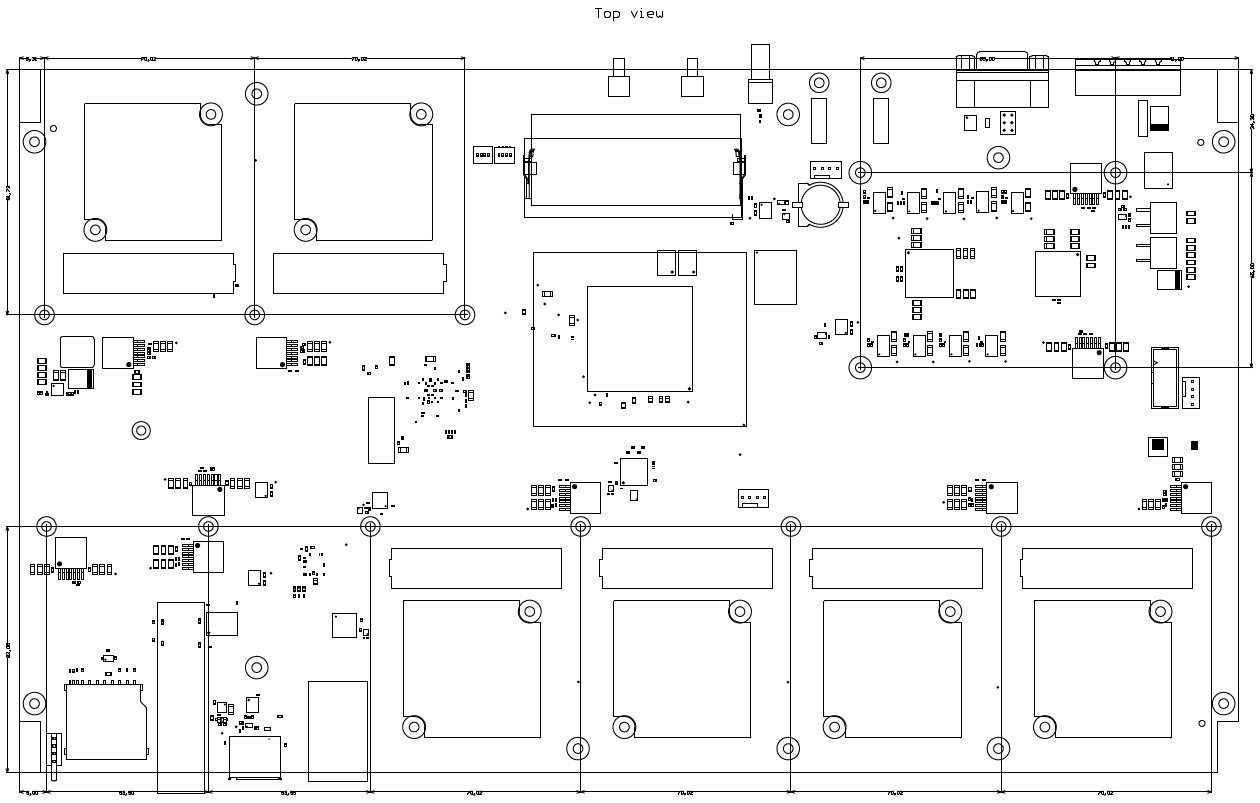

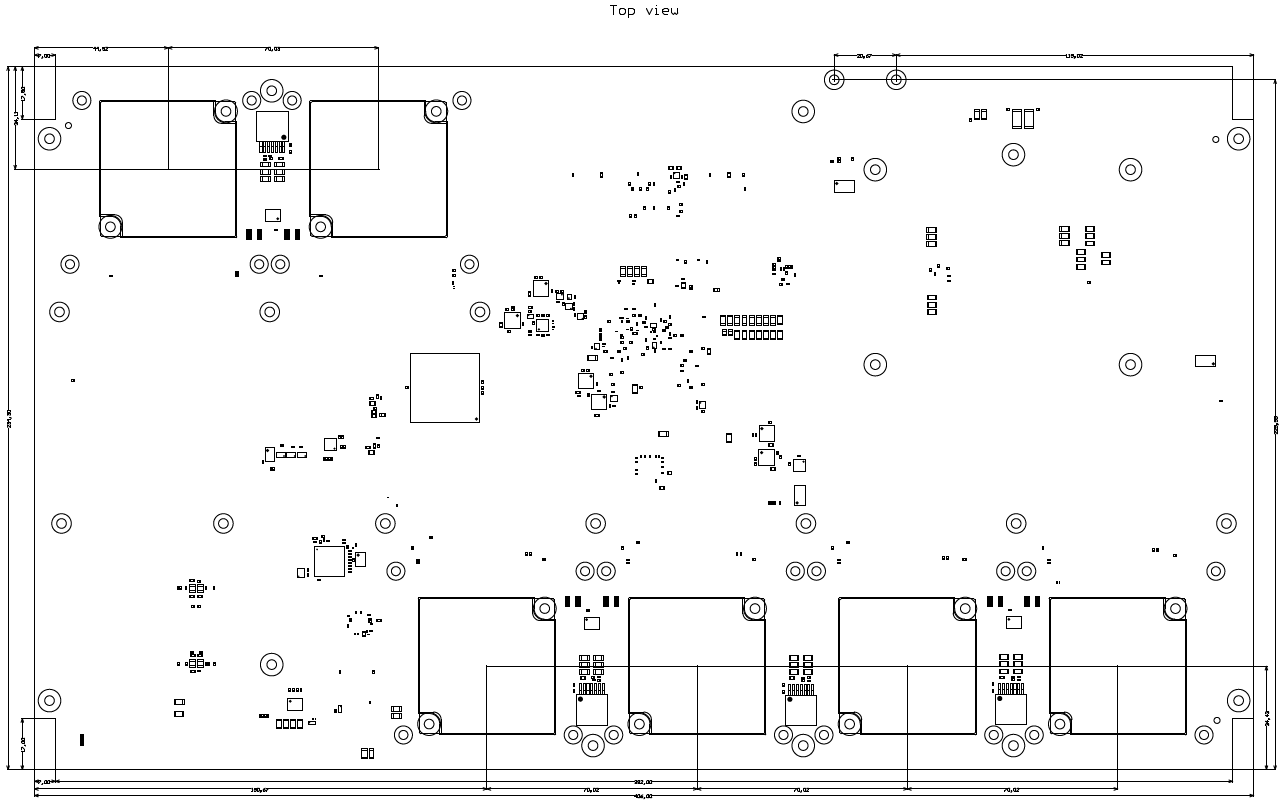

Put top and bottom pics with labels of the real PCB here...

Table 1: TE0xxx-xx main components.

Add description list of PCB labels here...

Initial Delivery State

...

Storage device name

...

Content

...

Notes

...

Table 1: Initial delivery state of programmable devices on the module.

Boot Process

For the boot process prior to powering up the board settings must be done via DIP-Switch S3-3 and S3-4. Four boot modes can be selected:

...

32-bit addressing, configured with dual on-board QSPI Flash Memory.

...

Table 2: Available boot modes of the on-board Zynq MPSoC

Refer also to the documentation of the SC CPLD firmware of the TEB0911 motherboard.

Signals, Interfaces and Pins

| HTML |

|---|

<!--

Connections and Interfaces or B2B Pin's which are accessible by User

--> |

FMC Connectors

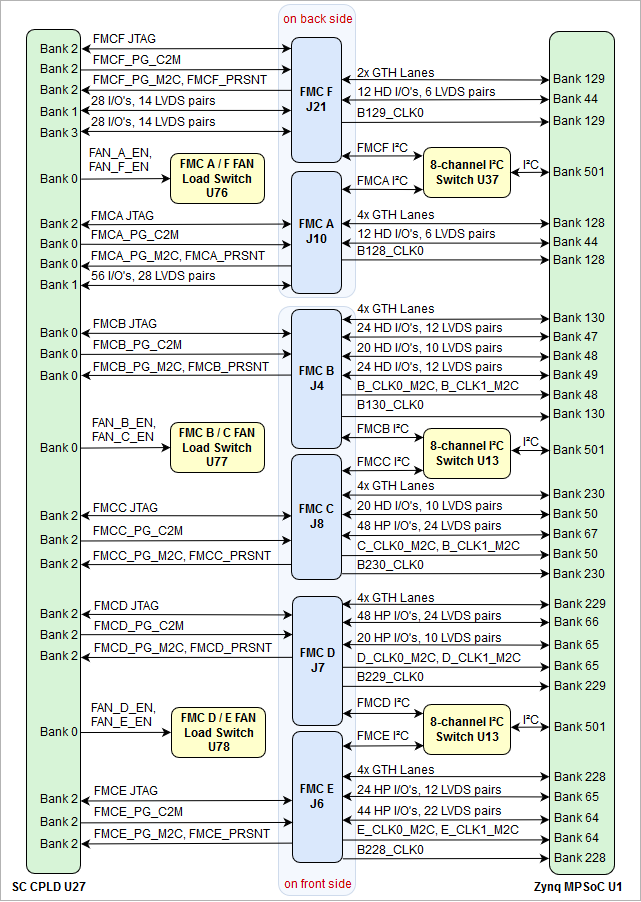

The TEB0911 Ultrarack+ offers 6 FMC (FPGA Mezzanine Card) connectors which provides as an ANSI/VITA 57.1 standard a modular interface to the MPSoCs FPGA and exposes numerous of its I/O pins and MGT Lanes for use by other mezzanine modules and expansion cards.

The connector supports single ended and differential signaling as the I/O's are routed from the FPGA banks as LVDS-pairs to the FMC connector.

Following diagram gives an overview of the FMC connectors and their connections to the Zynq Ultrascale+ MPSoC and the System Controller CPLD U27:

...

Following tables contains information about the interfaces, I/O's, clock and VCCIO sources available on the FMC connectors A - F:

FMC A Connector

...

J10

...

'FMCA_PG_C2M', 'FMCA_PG_M2C', 'FMCA_PRSNT'

Table 3: FMC A connector interfaces

...

J10

(FMC A)

...

- B128_RX0_P

- B128_RX0_N

- B128_TX0_P

- B128_TX0_N

...

- J10-C6

- J10-C7

- J10-C2

- J10-C3

...

- MGTHRXP0_128, T33

- MGTHRXN0_128, T34

- MGTHTXP0_128, T29

- MGTHTXN0_128, T30

...

- B128_RX1_P

- B128_RX1_N

- B128_TX1_P

- B128_TX1_N

...

- J10-A2

- J10-A3

- J10-A22

- J10-A23

...

- MGTHRXP1_128, P33

- MGTHRXN1_128, P34

- MGTHTXP1_128, R31

- MGTHTXN1_128, R32

...

- B128_RX2_P

- B128_RX2_N

- B128_TX2_P

- B128_TX2_N

...

- J10-A6

- J10-A7

- J10-A26

- J10-A27

...

- MGTHRXP2_128, N31

- MGTHRXN2_128, N32

- MGTHTXP2_128, P29

- MGTHTXN2_128, P30

...

- B128_RX3_P

- B128_RX3_N

- B128_TX3_P

- B128_TX3_N

...

- J10-A10

- J10-A11

- J10-A30

- J10-A31

...

- MGTHRXP3_128, M33

- MGTHRXN3_128, M34

- MGTHTXP3_128, M29

- MGTHTXN3_128, M30

|

Main Components

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

- SFP+ 2x1 cage with integrated LED light pipes, J9

- DisplayPort connector, J12

- USB3 A 2x , RJ45 1x (stacked), J13

- FMC connector (FMC B), J4

- FMC B cooling fan, M2

- FMC connector (FMC C), J8

- FMC C cooling fan, M3

- FMC connector (FMC D), J7

- FMC D cooling fan, M4

- FMC connector (FMC E), J6

- FMC E cooling fan, M5

- I²C programming header of on-board PLL clock generator U17, J22

- 4-Wire PWM fan connector, J23

- Main Power Jack 24V, J1

- CAN bus D-SUB 9-pin male connector, J3

- CAN bus 6-pin header male, J15

- XMOD JTAG header for access to System Controller CPLD, J35

- XMOD JTAG header for access to Zynq MPSoC, J24

- 4-Wire PWM fan connector, J33

- Battery Holder CR1220, B1

- SMA coaxial connector (PLL Si5345A U17 clock input), J25

- Push Button, S1

- Push Button, S2

- DDR4 SO-DIMM socket, U3

- 4-bit DIP-switch, S4

- 4-bit DIP-switch, S3

- FMC connector (FMC A), J10

- FMC A cooling fan, M1

- FMC connector (FMC F), J21

- FMC F cooling fan, M6

- NGFF M.2 PCIe socket (Key M), U2

- SD Card socket, J11

- User LEDs (3x green, 1x red) with LED light pipe, D13 ... D16

- Green LEDs dedicated to USB3 hub U4, D17 ... D19

- Red LED indicating FPGAs 'DONE' signal, D6

- 4-Wire PWM fan connector, J2

- Xilinx Zynq Ultrascale+ MPSoC, U1

Initial Delivery State

Storage device name | Content | Notes |

|---|---|---|

| User configuration EEPROMs (1x Microchip 24LC128-I/ST, 3x Microchip 24AA025E48T-I/OT) | Empty | Not programmed |

| USB3 HUB Configuration EEPROM (Microchip 24LC128-I/ST) | Empty | Not programmed |

| Si5338A programmable PLL NVM OTP | Empty | Not programmed |

| Si5345A programmable PLL NVM OTP | Empty | Not programmed |

| eMMC Flash memory | Empty | Not programmed |

| 2x QSPI Flash memory | Empty | Not programmed |

Table 1: Initial delivery state of programmable devices on the module

Boot Process

For the boot process prior to powering up the board settings must be done via DIP-Switch S3-3 and S3-4. Four boot modes can be selected:

| S3-3 (SC_SW1) | S3-4 (SC_SW2) | MIO Location | Description | Notes |

|---|---|---|---|---|

| OFF | OFF | MIO[43:38] | SD1 Boot Mode (SD-Card on J11) | Supports SD 2.0 |

| OFF | ON | MIO[29:26] | PJTAG0 | PS JTAG connection 0 option |

| ON | OFF | MIO[12:0] | QSPI32 | 32-bit addressing, configured with dual on-board QSPI Flash Memory |

| ON | ON | - | JTAG | Dedicated PS interface |

Table 2: Available boot modes of the on-board Zynq MPSoC

Refer also to the documentation of the SC CPLD firmware of the TEB0911 board, section 'boot mode'.

Signals, Interfaces and Pins

| HTML |

|---|

<!--

Connections and Interfaces or B2B Pin's which are accessible by User

--> |

FMC Connectors

The TEB0911 Ultrarack+ offers 6 FMC (FPGA Mezzanine Card) connectors which provides as an ANSI/VITA 57.1 standard a modular interface to the MPSoCs FPGA and exposes numerous of its I/O pins and MGT lanes for use by other mezzanine modules and expansion cards.

The connector supports single ended and differential signaling as the I/O's are routed from the FPGA banks as LVDS-pairs to the FMC connector.

Following diagram gives an overview of the FMC connectors and their connections to the Zynq Ultrascale+ MPSoC and the System Controller CPLD U27:

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

| HTML |

|---|

<!--

MGT lanes should be listed separately, as they are more specific than just general I/Os.

--> |

Following tables contains information about the interfaces, I/O's, clock and VCCIO sources available on the FMC connectors A - F:

Anchor FMC A FMC A

FMC A

FMC A Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage |

|---|

Table 4: FMC A connector MGT lanes

...

J10

(FMC A)

...

- B128_CLK0_P

- B128_CLK0_N

...

- J10-D4

- J10-D5

...

- MGTREFCLK0P_128, R27

- MGTREFCLK0N_128, R28

...

Table 5: FMC A connector clock signal input

| Notes | |

|---|---|

J10 (FMC A) |

- J10-D36

- J10-D38

- J10-D40

- J10-C39

DCDC U32,

max. cur.: 5A

Enable by SC CPLD U27,

Signal: 'EN_A_3V3'

- J10-D32

DCDC U50,

max. cur.: 1Aconnectors

- J10-C35

- J10-C37

DCDC U51,

max. cur.: 5A

- J10-H40

- J10-G39

- J10-F40

- J10-E39

DCDC U39,

max. cur.: 5A

Table 6: FMC A connector available VCC/VCCIO

...

J10

(FMC A)

...

Enable by SC CPLD U27,

Signal: 'FAN_A_EN'

...

| I/O | 12 | 6 | Bank 44 HD | FMCAF_1V8 | - | |

| 56 | 28 | SC CPLD U27 Bank 1 | FMCAF_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U37 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |

| MGT | - | 8 (4 x RX/TX) | Bank 128 GTH | - | 4x MGT lanes | |

| Clock Input | - | 1 | Bank 128 GTH | - | 1x Reference clock input to MGT bank | |

| Control Signals | 3 | - | SC CPLD U27 Bank 0 | 3.3VSB | 'FMCA_PG_C2M', 'FMCA_PG_M2C', 'FMCA_PRSNT' |

Table 3: FMC A connector interfaces

FMC A MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|

Table 7: FMC A connector cooling fan

FMC F Connector

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes | ||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

J10 (FMC A) | I/O0 | 12128 | 6 | Bank 44 HD | FMCAF_1V8 | - | 46 | 28 | SC CPLD U27 Bank 1 | FMCAF_1V8 | - | I²C | 2 | - | I²C-Switch U37 | - | Muxed to MIO Bank 501 I²C Inteface | JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | MGT | - | 8 (4 x RX/TX) | Bank 128 GTH | - | 4x MGT lanes | Clock Input | - | 1 | Bank 128 GTH | - | 1x Reference clock input to MGT bank | Control Signals | 3 | - | SC CPLD U27 Bank 0 | 3.3VSB | 'FMCA_PG_C2M', 'FMCA_PG_M2C', 'FMCA_PRSNT' | |

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes | I/O | 12 | 6 | Bank 44 HD | FMCAF_1V8 | - | ||||||||||||||||||||||||||||||

| 28 | 14 | SC CPLD U27 Bank 1 | FMCAF_1V8 | - | ||||||||||||||||||||||||||||||||||||||

| 68 | 34 | SC CPLD U27 Bank 3 | FMCAF_1V8 | - | ||||||||||||||||||||||||||||||||||||||

| I²C | 2 | - | I²C-Switch U37 | - | Muxed to MIO Bank 501 I²C Inteface | |||||||||||||||||||||||||||||||||||||

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |||||||||||||||||||||||||||||||||||||

| MGT | - | 8 (4 x RX/TX) | Bank 129 GTH | - | 4x MGT lanes | |||||||||||||||||||||||||||||||||||||

| Clock Input | - | 1 | Bank 129 GTH | - | 1x Reference clock input to MGT bank | |||||||||||||||||||||||||||||||||||||

| Control Signals | 3 | - | SC CPLD U27 Bank 2 | 3.3VSB | 'FMCF_PG_C2M', 'FMCF_PG_M2C', 'FMCF_PRSNT' | |||||||||||||||||||||||||||||||||||||

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes | ||||||||||||||||||||||||||||||||||||

J4 | I/O | 24 | 12 | Bank 47 HD | FMCBC_1V8 | - | ||||||||||||||||||||||||||||||||||||

| 20 | 10 | Bank 48 HD | FMCBC_1V8 | - | ||||||||||||||||||||||||||||||||||||||

| 24 | 12 | Bank 49 HD | FMCBC_1V8 | - | ||||||||||||||||||||||||||||||||||||||

| I²C | 2 | - | I²C-Switch U13 | - | Muxed to MIO Bank 501 I²C Inteface | |||||||||||||||||||||||||||||||||||||

| JTAG | 4 | - | SC CPLD U27 Bank 0 | 3.3VSB | - | |||||||||||||||||||||||||||||||||||||

| MGT | - | 8 (4 x RX/TX) | Bank 130 GTH | - | 4x MGT lanes | |||||||||||||||||||||||||||||||||||||

| Clock Input | - | 2 | Bank 48 HD | - | 2x Reference clock inputs to PL bank | |||||||||||||||||||||||||||||||||||||

| - | 1 | Bank 130 GTH | - | 1x Reference clock input to MGT bank | Control Signals | 3 | - | SC CPLD U27 Bank 0 | 3.3VSB | 'FMCB_PG_C2M', 'FMCB_PG_M2C', 'FMCB_PRSNT'|||||||||||||||||||||||||||||||||

| GTH |

| J10-C6 | MGTHRXP0_128, T33 | |||||||||||||||||||||||||||||||||||||||

| 1 | 128 | GTH |

| J10-A2 | MGTHRXP1_128, P33 | |||||||||||||||||||||||||||||||||||||

| 2 | 128 | GTH |

| J10-A6 | MGTHRXP2_128, N31 | |||||||||||||||||||||||||||||||||||||

| 3 | 128 | GTH |

| J10-A10 | MGTHRXP3_128, M33 |

Table 4: FMC A connector MGT lanes

FMC A Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J10 (FMC A) |

| 128 | J10-D4 | MGTREFCLK0P_128, R27 | Supplied by attached module |

Table 5: FMC A connector clock signal input

FMC A VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J10 (FMC A) | FMCA_3V3 | J10-D36 | DCDC U32, | Enable by SC CPLD U27, bank 2, pin Y18 |

| 3V3SB | J10-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V_FMC_AF | J10-C35 | DCDC U51, | - | |

| FMCAF_1V8 | J10-H40 | DCDC U39, | Enable by SC CPLD U27, bank 2, pin W19 |

Table 6: FMC A connector available VCC/VCCIO

FMC A Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J10 (FMC A) | M1 | Enable by SC CPLD U27, bank 2, pin Y19 | - |

Table 7: FMC A connector cooling fan

Anchor FMC F FMC F

FMC F

FMC F Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes | ||||

|---|---|---|---|---|---|---|---|---|---|---|

J8J21 (FMC CF) | I/O | 2012 | 106 | Bank 50 44 HD | FMCAF_1V8 | - | ||||

| 28 | 14 | SC CPLD U27 Bank 1 | FMCAFFMCBC_1V8 | - | ||||||

| 6828 | 3414 | SC CPLD U27 Bank 67 HP3 | FMCBCFMCAF_1V8 | - | ||||||

| I²C | 2 | - | I²C-Switch U13U37 | - | Muxed to MIO Bank 501 I²C Inteface | |||||

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |||||

| MGT | - | 8 4 (4 2 x RX/TX) | Bank 230 129 GTH | - | 4x 2x MGT lanes | |||||

| Clock Input | - | 2 | Bank 50 HD | - | 2x Reference clock inputs to PL bank | - | 1 | Bank 230 129 GTH | - | 1x Reference clock input to MGT bank |

| Control Signals | 3 | - | SC CPLD U27 Bank 2 | 3.3VSB | 'FMCCFMCF_PG_C2M', 'FMCCFMCF_PG_M2C', 'FMCCFMCF_PRSNT' |

Table 8: FMC

...

J7

(FMC D)

...

2x Reference clock inputs to PL bank

...

'FMCD_PG_C2M', 'FMCD_PG_M2C', 'FMCD_PRSNT'

...

J6

(FMC E)

...

2x Reference clock inputs to PL bank

...

'FMCE_PG_C2M', 'FMCE_PG_M2C', 'FMCE_PRSNT'

Table x: FMC connectors interfaces overview

| HTML |

|---|

<!--

MGT lanes should be listed separately, as they are more specific than just general I/Os.

--> |

MGT (Multi Gigabit Transceiver) lane consists of one transmit and one receive (TX/RX) differential pairs, two signals each or four signals total per one MGT lane. Following table lists lane number, MGT bank number, transceiver type, signal schematic name, FMC connector pin and FPGA pins:

Table x: MGT lanes

Below are listed MGT banks reference clock sources.

...

Table x: MGT reference clock sources

TODO: FMC fans table, FMC available VCC/VCCIO table

XMOD Interface

JTAG access to the ... is provided through XMOD connector ....

...

JTAG Signal

...

B2B Connector Pin

...

Table 5: JTAG interface signals.

Gigabit Ethernet Interface

USB3 Interface

SFP+ Interface

SSD Interface

DisplayPort Interface

DDR4 Memory Socket

CAN Interface

SD Card Interface

Describe SD Card interface shortly here if the module has one...

...

Table x: SD Card interface signals and connections.

PLL Clock Programing Interface

4-Wire PWM FAN Connectors

SMA Coax Clock Input

On-board Peripherals

| HTML |

|---|

<!--

Components on the Module, like Flash, PLL, PHY...

--> |

System Controller CPLD

The System Controller CPLD (U2) is provided by Lattice Semiconductor LCMXO2-256HC (MachXO2 Product Family). The SC-CPLD is the central system management unit where essential control signals are logically linked by the implemented logic in CPLD firmware, which generates output signals to control the system, the on-board peripherals and the interfaces. Interfaces like JTAG and I2C between the on-board peripherals and to the FPGA module are by-passed, forwarded and controlled by the System Controller CPLD.

Other tasks of the System Controller CPLD are the monitoring of the power-on sequence and to display the programming state of the FPGA module.

For detailed information, refer to the reference page of the SC CPLD firmware of this module.

The TEB0911 UltraRack is equipped with one System Controller CPLDs - Lattice Semiconductor LCMXO2-7000HC (MachXO2 Product Family) with the schematic designators U27.

The SC-CPLD is the central system management unit where essential control signals are logically linked by the implemented logic of the CPLD firmware, which generates output signals to control the system, the on-board peripherals and the interfaces. Interfaces like JTAG and I2C between the on-board peripherals and to the FPGA-module are by-passed, forwarded and controlled by the System Controller CPLD.

Other tasks of the System Controller CPLD are the monitoring of the power-on sequence and to display the programming state of the FPGA module.

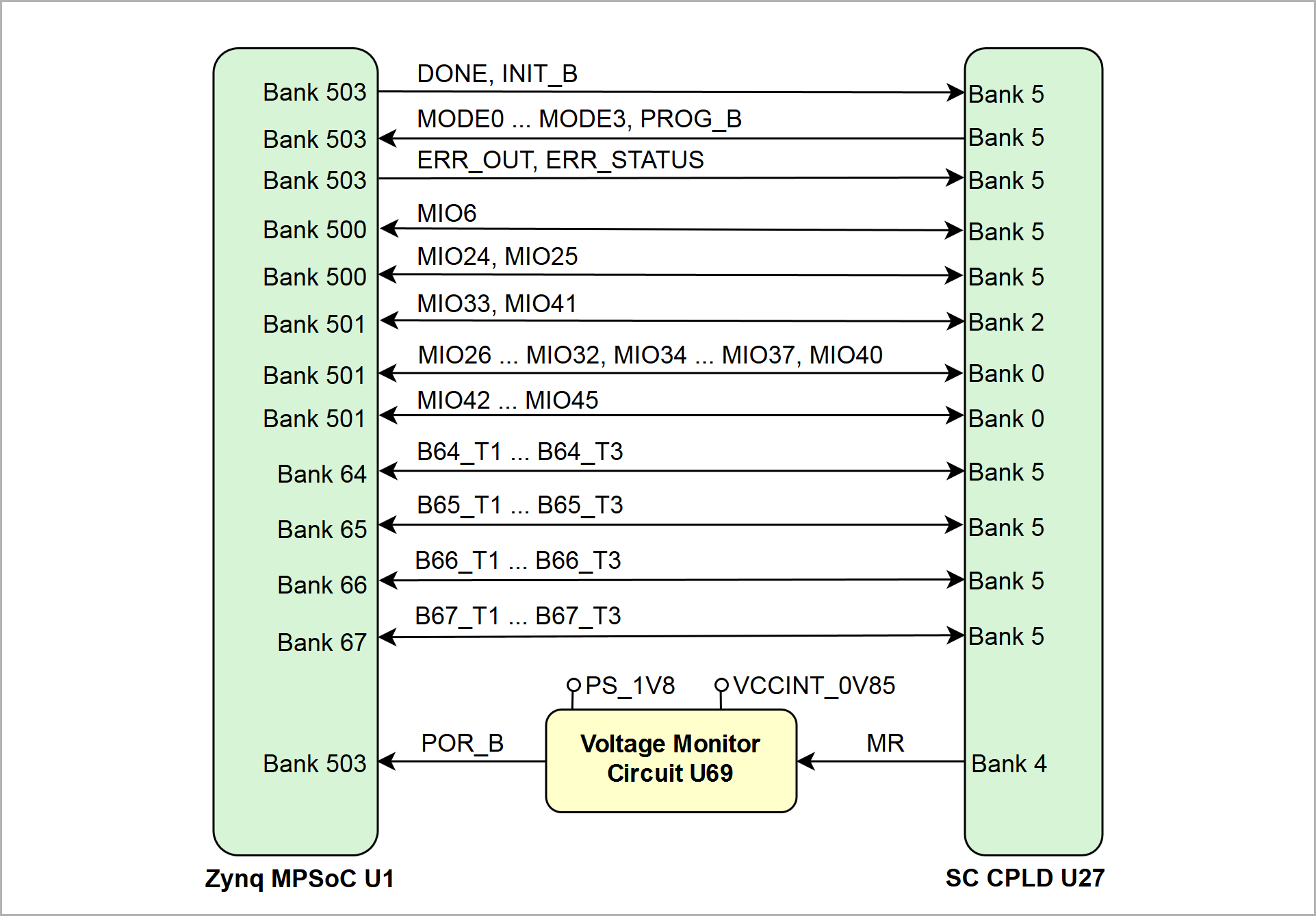

The Sytem Controller CPLDs are connected to the Zynq Ultrascale+ MPSoC through MIO, PL IO-bank differential lanes and I²C interface.

The functionalities and configuration of the pins depend on the CPLDs' firmware. The documentations of the firmware of SC CPLD U27 contains detailed information on this matter.

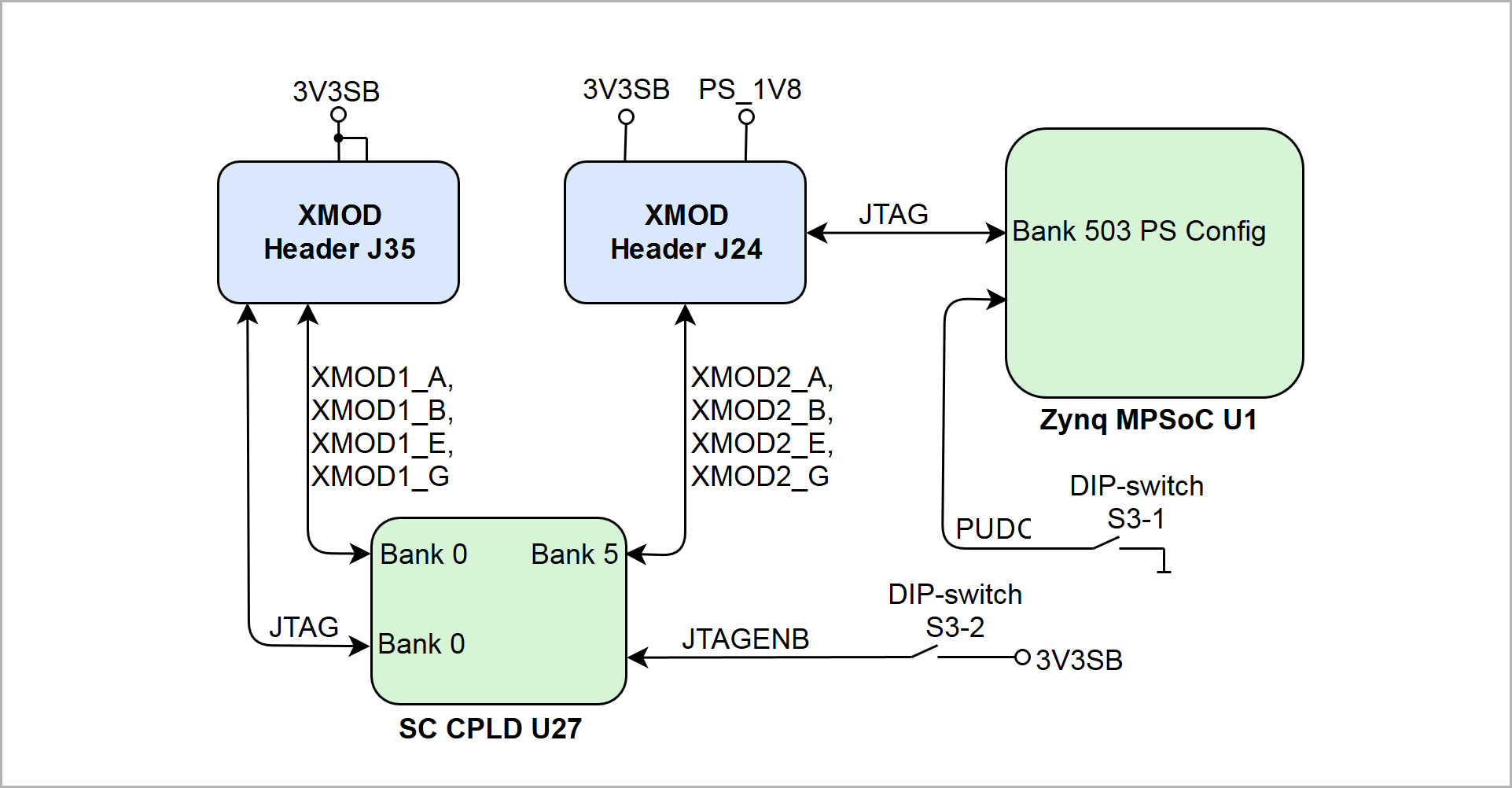

Following block diagram visualizes the connection of the SC CPLDs with the Zynq Ultrascale+ MPSoC via PS (MIO), PL bank pins and I²C interface.

| HTML |

|---|

<!--

Put in link to the Wiki reference page of the firmware of the SC CPLD.

--> |

Special purpose pins are connected to smaller System Controller CPLD and have following default configuration:

...

Table x: System Controller CPLD I/O pins.

| HTML |

|---|

<!--

For the detailed function of the pins and signals, the internal signal assignment and implemented logic, look to the Wiki reference page SC CPLD of this module or into the bitstream file of the SC CPLD.

Add link to the Wiki reference page of the SC CPLD, if available.

--> |

High-speed USB ULPI PHY

USB PHY (U9) is provided by USB3320 from Microchip. The ULPI interface is connected to the Zynq Ultrascale+ PS USB0. I/O voltage is fixed at 1.8V and PHY reference clock input is supplied from the on-board 52.000000 MHz oscillator (U10).

...

Table 17: USB PHY interface connections

Hi-speed USB ULPI PHY (U32) is provided with USB3320 from Microchip. The ULPI interface is connected to the Zynq PS USB0 via MIO28..39, bank 501 (see also section). The I/O voltage is fixed at 1.8V and PHY reference clock input is supplied from the on-board 52.000000 MHz oscillator (U33).

4-port USB3.0 Hub

On the carrier board there are up to 4 USB3.0 Super Speed ports available, which are also downward compatible to USB2.0 High Speed ports. The USB3.0 ports are provided by Cypress Semiconductor CYUSB3324 4-port USB3.0 Hub controller U4. The pin-strap configuration option of the USB3.0 Hub is disabled, so this controller gets the configuration data and parameter from the configuration EEPROM U5. The I²C interface of the EEPROM and the controller is also accessible by the Zynq Ultrascale+ MPSoC through I²C switch U16.

On the Upstream-side, this controller is connected to the MGT1 lane of MPSoC's PS GT bank to establish the USB3.0 data lane. For the USB2.0 interface, the controller is connected to the on-board USB2.0 PHY U9. The USB2.0 PHY is connected per ULPI interface (MIO pins 52..63) to MPSoC's MIO bank.

The USB3.0 Hub controller has also an ARM Cortex-M0 controller integrated, refer to the data sheet for further features and programmable options.

Gigabit Ethernet PHY

On-board Gigabit Ethernet PHY (U12) is provided with Marvell Alaska 88E1512 IC. The Ethernet PHY RGMII interface is connected to the Zynq Ultrascale+ Ethernet0 PS GEM3. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from the on-board 25.000000 MHz oscillator (U13). The 125MHz PHY output clock (PHY_CLK125M) is routed to System Controller CPLD U17, pin 70.

...

Table 18: Ethernet PHY interface connections

On-board Gigabit Ethernet PHY (U7) is provided with Marvell Alaska 88E1512 IC (U8). The Ethernet PHY RGMII interface is connected to the Zynq Ethernet0 PS GEM0. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from an on-board 25.000000 MHz oscillator (U9), the 125MHz output clock signal CLK_125MHZ is connected to the pin J2-150 of B2B connector J2.

8-Channel I²C Switches

All on-board and on-module peripherals with accessible I²C interface are muxed to the I²C interface of the Zynq Ultrascale+ MPSoC as master.

For this purpose, the TEB0911 carrier board is equipped with two 8-channel I²C switches provided by TCA9548A from Texas Instruments, together creating up to 16 switched I²C channels.

Refer to the data sheet of the TCA9548A chip how to address and and transmit data to the I²C slave devices through this switches.

The I2C bus works internally on-module with reference voltage 1.8V, it is connected to the MPSoC I2C interface via PS MIO bank (pins MIO38, MIO39) configured as master.

...

I2C addresses for on-board slave devices are listed in the table below:

...

F connector interface

FMC F MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J21 (FMC F) | 0 | 129 | GTH |

| J21-C6 | MGTHRXP0_129, L31 |

| 1 | 129 | GTH |

| J21-A2 | MGTHRXP1_129, K33 |

Table 9: FMC F connector MGT lanes

FMC F Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J21 (FMC F) |

| 129 | J21-D4 | MGTREFCLK0P_129, L27 | Supplied by attached module |

Table 10: FMC F connector clock signal input

FMC F VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J21 (FMC F) | FMCF_3V3 | J21-D36 | DCDC U42, | Enable by SC CPLD U27, bank 2, pin Y10 |

| 3V3SB | J21-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V_FMC_AF | J21-C35 | DCDC U51, | - | |

| FMCAF_1V8 | J21-H40 | DCDC U39, | Enable by SC CPLD U27, bank 2, pin W19 |

Table 11: FMC F connector available VCC/VCCIO

FMC F Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J21 (FMC F) | M6 | Enable by SC CPLD U27, bank 2, pin W18 | - |

Table 12: FMC F connector cooling fan

Anchor FMC B FMC B

FMC B

FMC B Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|---|---|---|---|---|---|

J4 (FMC B) | I/O | 24 | 12 | Bank 47 HD | FMCBC_1V8 | - |

| 20 | 10 | Bank 48 HD | FMCBC_1V8 | - | ||

| 24 | 12 | Bank 49 HD | FMCBC_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U13 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 0 | 3.3VSB | - | |

| MGT | - | 8 (4 x RX/TX) | Bank 130 GTH | - | 4x MGT lanes | |

| Clock Input | - | 2 | Bank 48 HD | - | 2x Reference clock inputs to PL bank | |

| - | 1 | Bank 130 GTH | - | 1x Reference clock input to MGT bank | ||

| Control Signals | 3 | - | SC CPLD U27 Bank 0 | 3.3VSB | 'FMCB_PG_C2M', 'FMCB_PG_M2C', 'FMCB_PRSNT' |

Table 13: FMC B connector interfaces

FMC B MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J4 (FMC B) | 3 | 130 | GTH |

| J4-C6 | MGTHRXP3_130, B33 |

| 2 | 130 | GTH |

| J4-A2 | MGTHRXP2_130, C31 | |

| 1 | 130 | GTH |

| J4-A6 | MGTHRXP1_130, D33 | |

| 0 | 130 | GTH |

| J4-A10 | MGTHRXP0_130, E31 |

Table 14: FMC B connector MGT lanes

FMC B Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J4 (FMC B) |

| 130 | J4-D4 | MGTREFCLK0P_130, G27 | Supplied by attached module |

| 48 HD | J4-H4 | IO_L6P_HDGC_48, F17 | Supplied by attached module | |

| 48 HD | J4-G2 | IO_L5P_HDGC_48, G18 | Supplied by attached module |

Table 15: FMC B connector clock signal input

FMC B VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J4 (FMC B) | FMCB_3V3 | J4-D36 | DCDC U33, | Enable by SC CPLD U27, bank 0, pin G11 |

| 3V3SB | J4-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V | J4-C35 | DCDC U82, | not dedicated for FMC connectors | |

| FMCBC_1V8 | J4-H40 | DCDC U40, | Enable by SC CPLD U27, bank 0, pin A3 |

Table 16: FMC B connector available VCC/VCCIO

FMC B Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J4 (FMC B) | M2 | Enable by SC CPLD U27, bank 0, pin A2 | - |

Table 17: FMC B connector cooling fan

Anchor FMC C FMC C

FMC C

FMC C Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|---|---|---|---|---|---|

J8 (FMC C) | I/O | 20 | 10 | Bank 50 HD | FMCBC_1V8 | - |

| 48 | 24 | Bank 67 HP | FMCBC_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U13 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |

| MGT | - | 8 (4 x RX/TX) | Bank 230 GTH | - | 4x MGT lanes | |

| Clock Input | - | 2 | Bank 50 HD | - | 2x Reference clock inputs to PL bank | |

| - | 1 | Bank 230 GTH | - | 1x Reference clock input to MGT bank | ||

| Control Signals | 3 | - | SC CPLD U27 Bank 2 | 3.3VSB | 'FMCC_PG_C2M', 'FMCC_PG_M2C', 'FMCC_PRSNT' |

Table 18: FMC C connector interfaces

FMC C MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J8 (FMC C) | 3 | 230 | GTH |

| J8-C6 | MGTHRXP3_230, A4 |

| 2 | 230 | GTH |

| J8-A2 | MGTHRXP2_230, B2 | |

| 1 | 230 | GTH |

| J8-A6 | MGTHRXP1_230, C4 | |

| 0 | 230 | GTH |

| J8-A10 | MGTHRXP0_230, D2 |

Table 19: FMC C connector MGT lanes

FMC C Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J8 (FMC C) |

| 230 | J8-D4 | MGTREFCLK0P_230, C8 | Supplied by attached module |

| 50 HD | J8-H4 | IO_L7P_HDGC_50, J12 | Supplied by attached module | |

| 50 HD | J8-G2 | IO_L8P_HDGC_50, H13 | Supplied by attached module |

Table 20: FMC C connector clock signal input

FMC C VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J8 (FMC C) | FMCC_3V3 | J8-D36 | DCDC U34, | Enable by SC CPLD U27, bank 0, pin E11 |

| 3V3SB | J8-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V | J8-C35 | DCDC U82, | not dedicated for FMC connectors | |

| FMCBC_1V8 | J8-H40 | DCDC U40, | Enable by SC CPLD U27, bank 0, pin A3 |

Table 21: FMC C connector available VCC/VCCIO

FMC C Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J8 (FMC C) | M3 | Enable by SC CPLD U27, bank 0, pin B3 | - |

Table 22: FMC C connector cooling fan

Anchor FMC D FMC D

FMC D

FMC D Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|---|---|---|---|---|---|

J7 (FMC D) | I/O | 20 | 10 | Bank 65 HP | FMCDE_1V8 | - |

| 48 | 24 | Bank 66 HP | FMCDE_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U13 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |

| MGT | - | 8 (4 x RX/TX) | Bank 229 GTH | - | 4x MGT lanes | |

| Clock Input | - | 2 | Bank 65 HP | - | 2x Reference clock inputs to PL bank | |

| - | 1 | Bank 229 GTH | - | 1x Reference clock input to MGT bank | ||

| Control Signals | 3 | - | SC CPLD U27 Bank 2 | 3.3VSB | 'FMCD_PG_C2M', 'FMCD_PG_M2C', 'FMCD_PRSNT' |

Table 23: FMC D connector interfaces

FMC D MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J7 (FMC D) | 3 | 229 | GTH |

| J7-C6 | MGTHRXP3_229, F2 |

| 2 | 229 | GTH |

| J7-A2 | MGTHRXP2_229, H2 | |

| 1 | 229 | GTH |

| J7-A6 | MGTHRXP1_229, J4 | |

| 0 | 229 | GTH |

| J7-A10 | MGTHRXP0_229, K2 |

Table 24: FMC D connector MGT lanes

FMC D Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J7 (FMC D) |

| 229 | J7-D4 | MGTREFCLK0P_229, G8 | Supplied by attached module |

| 65 HP | J7-H4 | IO_L14P_T2L_N2_GC_65, AG5 | Supplied by attached module | |

| 65 HP | J7-G2 | IO_L13P_T2L_N0_GC_QBC_65, AE5 | Supplied by attached module |

Table 25: FMC D connector clock signal input

FMC D VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J7 (FMC D) | FMCD_3V3 | J7-D36 | DCDC U35, | Enable by SC CPLD U27, bank 0, pin F8 |

| 3V3SB | J7-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V | J7-C35 | DCDC U82, | not dedicated for FMC connectors | |

| FMCDE_1V8 | J7-H40 | DCDC U41, | Enable by SC CPLD U27, bank 0, pin C5 |

Table 26: FMC D connector available VCC/VCCIO

FMC D Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J7 (FMC D) | M4 | Enable by SC CPLD U27, bank 0, pin D7 | - |

Table 27: FMC D connector cooling fan

Anchor FMC E FMC E

FMC E

FMC E Interfaces:

| FMC | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|---|---|---|---|---|---|

J6 (FMC E) | I/O | 24 | 12 | Bank 65 HP | FMCDE_1V8 | - |

| 44 | 22 | Bank 64 HP | FMCDE_1V8 | - | ||

| I²C | 2 | - | I²C-Switch U13 | - | Muxed to MIO Bank 501 I²C Inteface | |

| JTAG | 4 | - | SC CPLD U27 Bank 2 | 3.3VSB | - | |

| MGT | - | 8 (4 x RX/TX) | Bank 228 GTH | - | 4x MGT lanes | |

| Clock Input | - | 2 | Bank 64 HP | - | 2x Reference clock inputs to PL bank | |

| - | 1 | Bank 228 GTH | - | 1x Reference clock input to MGT bank | ||

| Control Signals | 3 | - | SC CPLD U27 Bank 2 | 3.3VSB | 'FMCE_PG_C2M', 'FMCE_PG_M2C', 'FMCE_PRSNT' |

Table 28: FMC E connector interfaces

FMC E MGT Lanes:

| FMC | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector Pin | FPGA Pin |

|---|---|---|---|---|---|---|

J6 (FMC E) | 3 | 228 | GTH |

| J6-C6 | MGTHRXP3_228, L4 |

| 2 | 228 | GTH |

| J6-A2 | MGTHRXP2_228, M2 | |

| 1 | 228 | GTH |

| J6-A6 | MGTHRXP1_228, P2 | |

| 0 | 228 | GTH |

| J6-A10 | MGTHRXP0_228, T2 |

Table 29: FMC E connector MGT lanes

FMC E Clock Signals:

| FMC | Signal Schematic Name | Bank | FMC Connector Pin | FPGA Pin | Notes |

|---|---|---|---|---|---|

J6 (FMC E) |

| 228 | J6-D4 | MGTREFCLK0P_228, L8 | Supplied by attached module |

| 64 HP | J6-H4 | IO_L12P_T1U_N10_GC_64, AL8 | Supplied by attached module | |

| 64 HP | J6-G2 | IO_L11P_T1U_N8_GC_64, AK8 | Supplied by attached module |

Table 30: FMC E connector clock signal input

FMC E VCC/VCCIO:

| FMC | Available VCC/VCCIO | FMC Connector Pin | Source | Notes |

|---|---|---|---|---|

J6 (FMC E) | FMCE_3V3 | J6-D36 | DCDC U36, | Enable by SC CPLD U27, bank 0, pin E8 |

| 3V3SB | J6-D32 | DCDC U50, max. cur.: 1A | not dedicated for FMC connectors | |

| 12V | J6-C35 | DCDC U82, | not dedicated for FMC connectors | |

| FMCDE_1V8 | J6-H40 | DCDC U41, | Enable by SC CPLD U27, bank 0, pin C5 |

Table 31: FMC E connector available VCC/VCCIO

FMC E Cooling Fan:

| FMC | Fan Designator | Enable Signal | Notes |

|---|---|---|---|

J6 (FMC E) | M5 | Enable by SC CPLD U27, bank 0, pin D6 | - |

Table 32: FMC E connector cooling fan

XMOD JTAG Interface

JTAG access to the Zynq MPSoC and SC CPLD is provided through XMOD header J24 and J35:

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Signal Assignment of XMOD header J24 and J35

| Connector | Interface | Signal Schematic Name | XMOD Header Pin | Connected to | VCCIO | VCC |

|---|---|---|---|---|---|---|

XMOD Header J24 | JTAG |

| J24-4 | Bank 503 PS Config, Pin R25 | PS_1V8 | 3V3SB |

| J24-10 | Bank 503 PS Config, Pin U25 | ||||

| J24-8 | Bank 503 PS Config, Pin T25 | ||||

| J24-12 | Bank 503 PS Config, Pin R24 | ||||

GPIO/ |

| J24-3 | SC CPLD U27, bank 5, Pin K7 | |||

| J24-7 | SC CPLD U27, bank 5, Pin K6 | ||||

| J24-9 | SC CPLD U27, bank 5, Pin H7 | ||||

| J24-11 | SC CPLD U27, bank 5, Pin H6 | ||||

XMOD Header J35 | JTAG |

| J35-4 | SC CPLD U27, bank 0, Pin A8 | 3V3SB | |

| J35-10 | SC CPLD U27, bank 0, Pin C7 | ||||

| J35-8 | SC CPLD U27, bank 0, Pin A6 | ||||

| J35-12 | SC CPLD U27, bank 0, Pin C9 | ||||

GPIO/ |

| J35-3 | SC CPLD U27, bank 0, Pin B19 | |||

| J35-9 | SC CPLD U27, bank 0, Pin A17 | ||||

| J35-7 | SC CPLD U27, bank 0, Pin C17 | ||||

| J35-11 | SC CPLD U27, bank 0, Pin A18 |

Table 33: XMOD interface signals

The JTAG interfaces of the TEB0911 UltraRack board can accessed with the XMOD-FT2232H adapter-board TE0790. The on-board devices Zynq MPSoC U1 and SC CPLD U27 can be programmed via USB2.0 interface of the TE0790 programmer.

XMOD-Header J24 is designated to program the Zynq Ultrascale+ MPSoC via USB interface, the 4 GPIO/UART pins (XMOD2_A/B/E/G) of this header are routed to the System Controller CPLD U27.

XMOD-Header J35 is designated to program the System Controller CPLD U27 via USB interface, the 4 GPIO/UART pins (XMOD1_A/B/E/G) of this header are also routed to the System Controller CPLD U27.

To program the System Controller CPLD, the JTAG interface of this devices have to be activated by DIP-switch S3-2. J35 JTAG is used for FMC JTAG, is JTAGENB is low (see CPLD Firmware).

When using XMOD FTDI JTAG Adapter TE0790, the adapter-board's VCC and VCCIO on both headers J24 and J35 will be sourced by the on-board supply voltages. Set the XMOD DIP-switch with the setting:

| XMOD DIP-switches | Position |

|---|---|

| Switch 1 | ON |

| Switch 2 | OFF |

| Switch 3 | OFF |

| Switch 4 | OFF |

Table 34: XMOD adapter board DIP-switch positions for voltage configuration

| Note |

|---|

Use Xilinx compatible TE0790 adapter board (designation TE-0790-xx without 'L') to program the Xilinx Zynq devices. The TE0790 adapter board's CPLD have to be configured with the Standard variant of the firmware. Refer to the TE0790 Resources Site for further information and firmware download. |

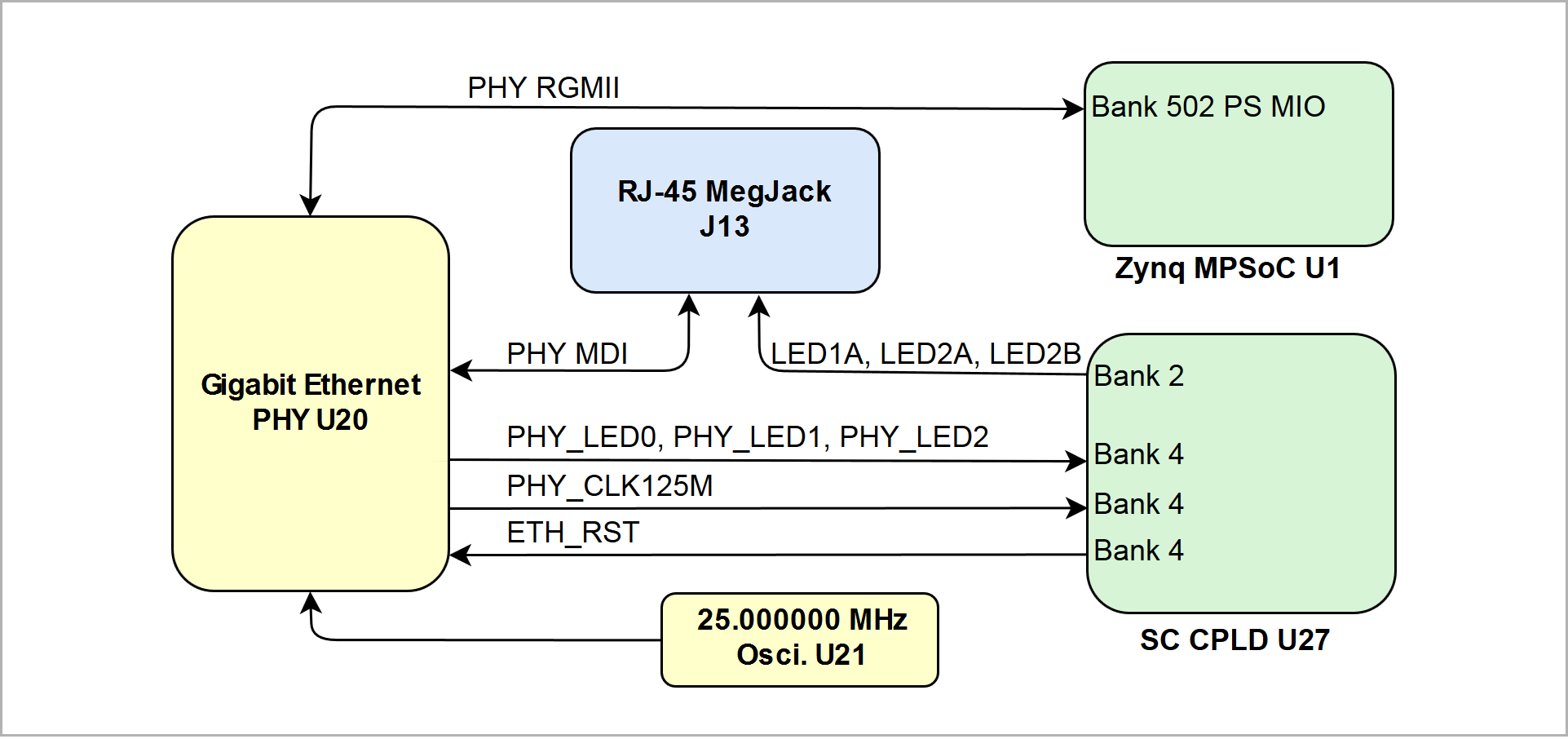

Gigabit Ethernet Interface

On-board Gigabit Ethernet PHY is provided with Marvell Alaska 88E1512 IC U20. The Ethernet PHY RGMII interface is connected to the Zynq MPSoC Ethernet interface of the PS MIO bank 502. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from the on-board 25.000000 MHz oscillator U21. The LEDs of the RJ-45 MegJack J13 are connected to the System Controller CPLD bank 2, pins Y12, Y13 and Y14.

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Following table describes the signals and control lines of the Gigabit Ethernet interface of the board:

| PHY Pin | Connected to | Notes |

|---|---|---|

| MDC/MDIO | PS bank 502 MIO76, MIO77 | - |

| PHY LED0..2 | SC CPLD U27, bank 4, pin L5, L1, K1 | see schematic for details, forwarded to RJ45 GbE MagJack J7 |

| PHY_CLK125M | SC CPLD U27, bank 4, pin K2 | 125 MHz Ethernet PHY clock out |

| CONFIG | pulled up to PS_1V8 | Configuration of PHY address LSB and VDDO level |

| RESETn | SC CPLD U27, bank 4, pin L6 | Active low reset line |

| RGMII | PS bank 502 MIO64 ... MIO75 | Reduced Gigabit Media Independent Interface |

| SGMII | - | Serial Gigabit Media Independent Interface |

| MDI | RJ45 GbE MagJack J13 | Media Dependent Interface |

Table 35: Ethernet PHY interface connections

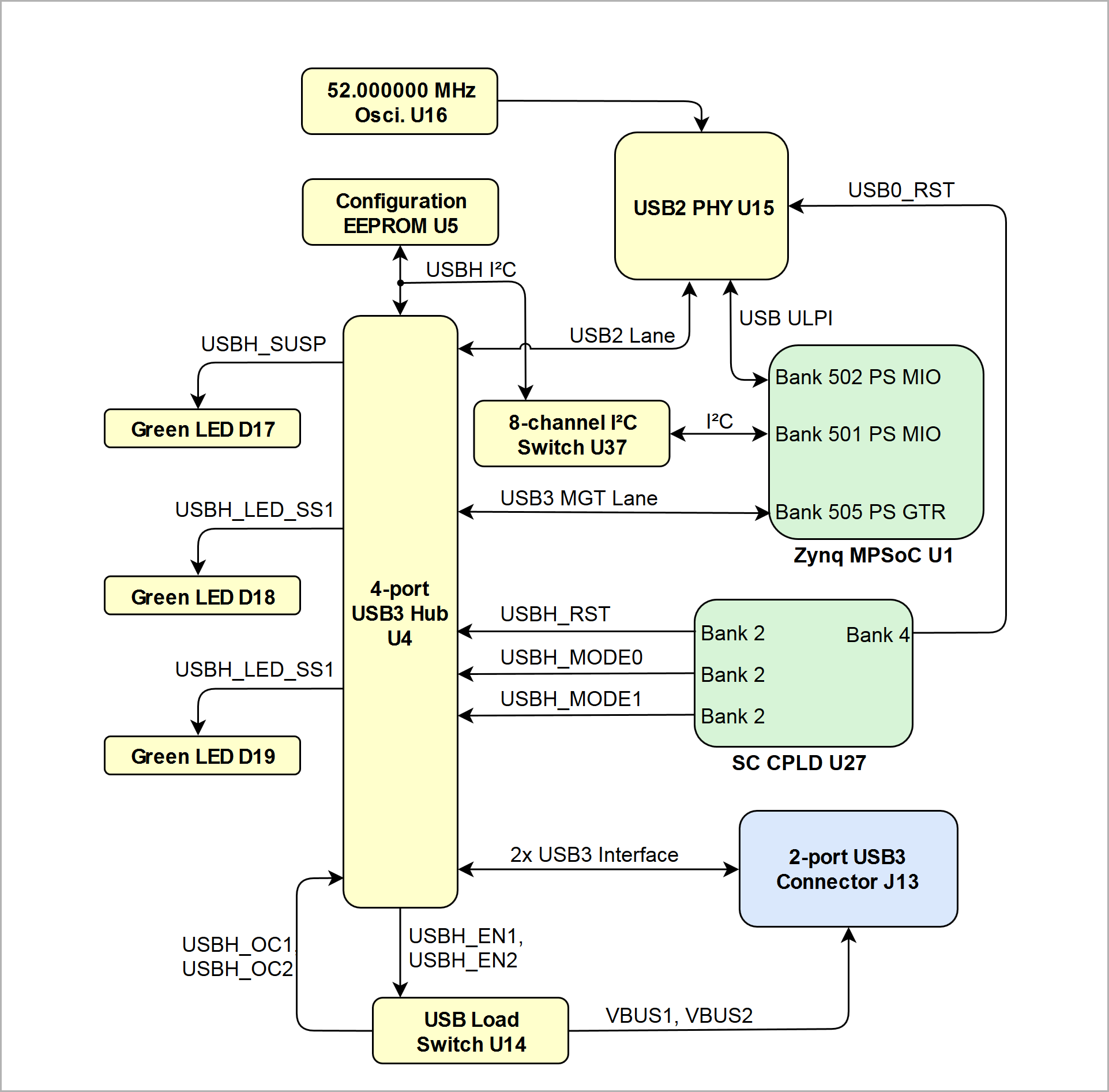

USB3 Interface

On the TEB0911 board two USB3 Superspeed ports are available to the user, which are downward compatible to USB2 Highspeed.

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

The 4-port USB3 hub is connected to the Zynq MPSoC's PS GTR bank, the USB2 PHY is connected to the PS MIO bank 502:

| IC | Interface | Signal Schematic Names | Connected to | Notes |

|---|---|---|---|---|

| USB3 Hub U4 | USB3 Upstream MGT lane |

| PS_MGTRTXP1_505, Y29 | - |

| USB2 Uptream data LVDS pair |

| USB2 PHY U15 Pins: 18,19 | - | |

| USB3 Downstream lane |

| 2-port USB3 A / RJ-45 connector | - | |

| USB2 Downstream LVDS pair |

| 2-port USB3 A / RJ-45 connector | - | |

| I²C |

| USB3 hub U4 Configuration EEPROM U5, 8-channel I²C-switch U37 | - | |

| Control Lines |

| SC CPLD U27, bank 2 Pins: Y17, Y16, Y15 | - | |

| USB2 PHY U15 | USB2 ULPI |

| PS bank 502 Pins: MIO52 ... MIO63 | - |

| USB2 data LVDS pair |

| USB3 Hub U4 Pins: 71,72 | - | |

| Control Lines |

| SC CPLD U27, bank 4 Pin: M2 | - |

Table 36: USB3 signals and interfaces

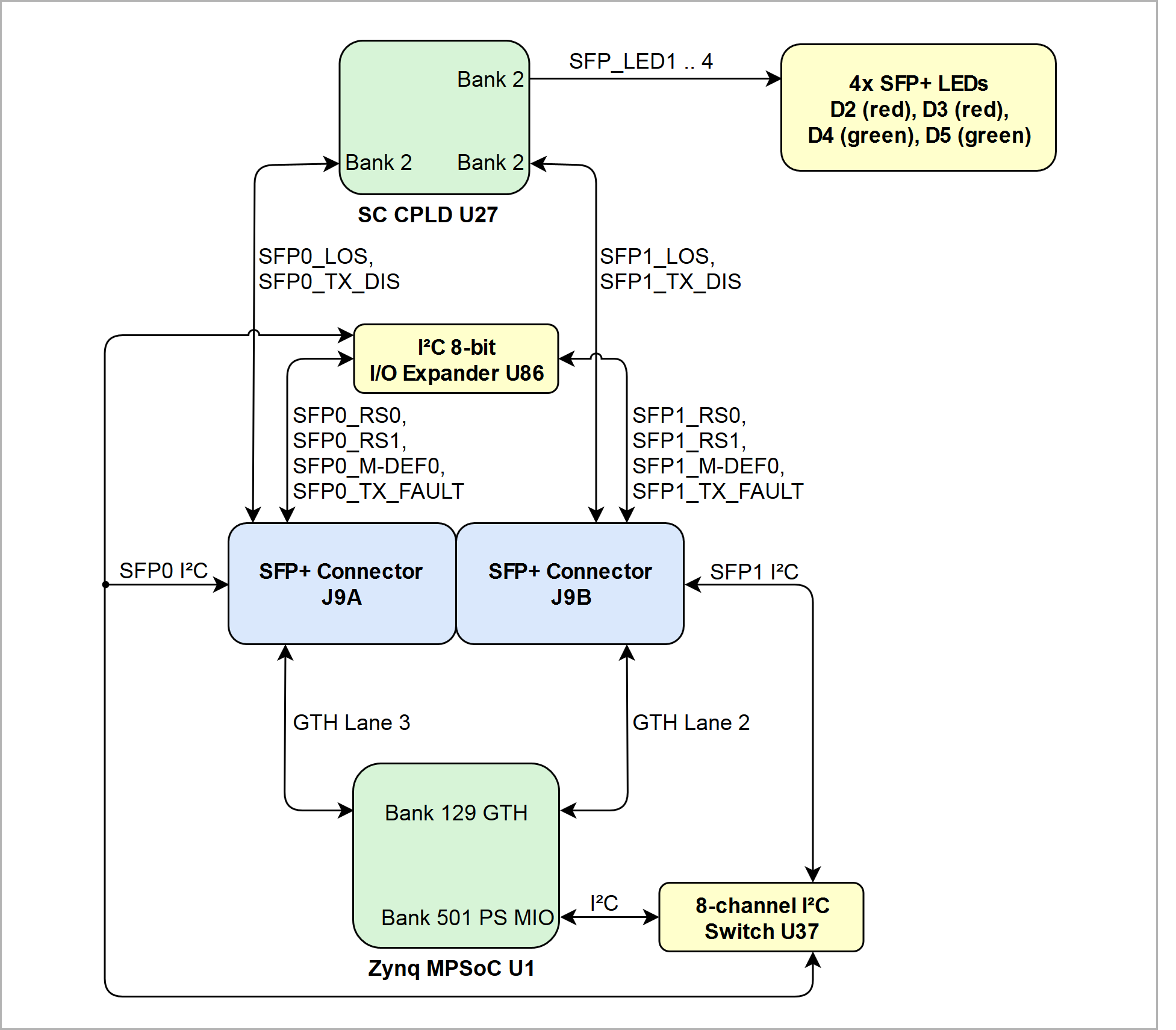

SFP+ Interface

The TEB0911 board provides the high speed MGT interface connectors "SFP+" (Enhanced small form-factor pluggable) with data transmission rates up to 10 Gbit/s.

Block diagram below shows the dependencies between the implied devices which establish the SFP+ interface:

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

| Connector | Interface | Signal Schematic Name | Connected to | Logic | Notes |

|---|---|---|---|---|---|

SFP+ J9A | MGT Lane |

| MGTHTXP3_129, G31 | TX: Output RX: Input | Multi gigabit highspeed data lane |

| I²C |

| 8-channel I²C-switch U37 | BiDir | 2-wire Serial Interface | |

| Control Lines |

| I²C 8-bit I/O Port-Expander U86 | Output, low active | Full RX bandwidth | |

| Output, low active | Reduced RX bandwidth | |||

| Input, low active | Module present / not present | |||

| Input, high active | Fault / Normal Operation | |||

| SC CPLD U27, bank 2, pin V8 | Input, high active | Loss of receiver signal | ||

| SC CPLD U27, bank 2, pin Y7 | Output, low active | SFP Enabled / Disabled | ||

SFP+ J9B | MGT Lane |

| MGTHTXP2_129, H29 | TX: Output RX: Input | Multi gigabit highspeed |

| I²C |

| 8-channel I²C-switch U37 | Bidir | 2-wire Serial Interface | |

| Control Lines |

| I²C 8-bit I/O Port-Expander U86 | Output, low active | Full RX bandwidth | |

| Output, low active | Reduced RX bandwidth | |||

| Input, low active | Module present / not present | |||

| Input, high active | Fault / Normal Operation | |||

| SC CPLD U27, bank 2, pin W7 | Input, high active | Loss of receiver signal | ||

| SC CPLD U27, bank 2, pin V7 | Output. low active | SFP Enabled / Disabled |

Table 37: SFP+ signals and interfaces

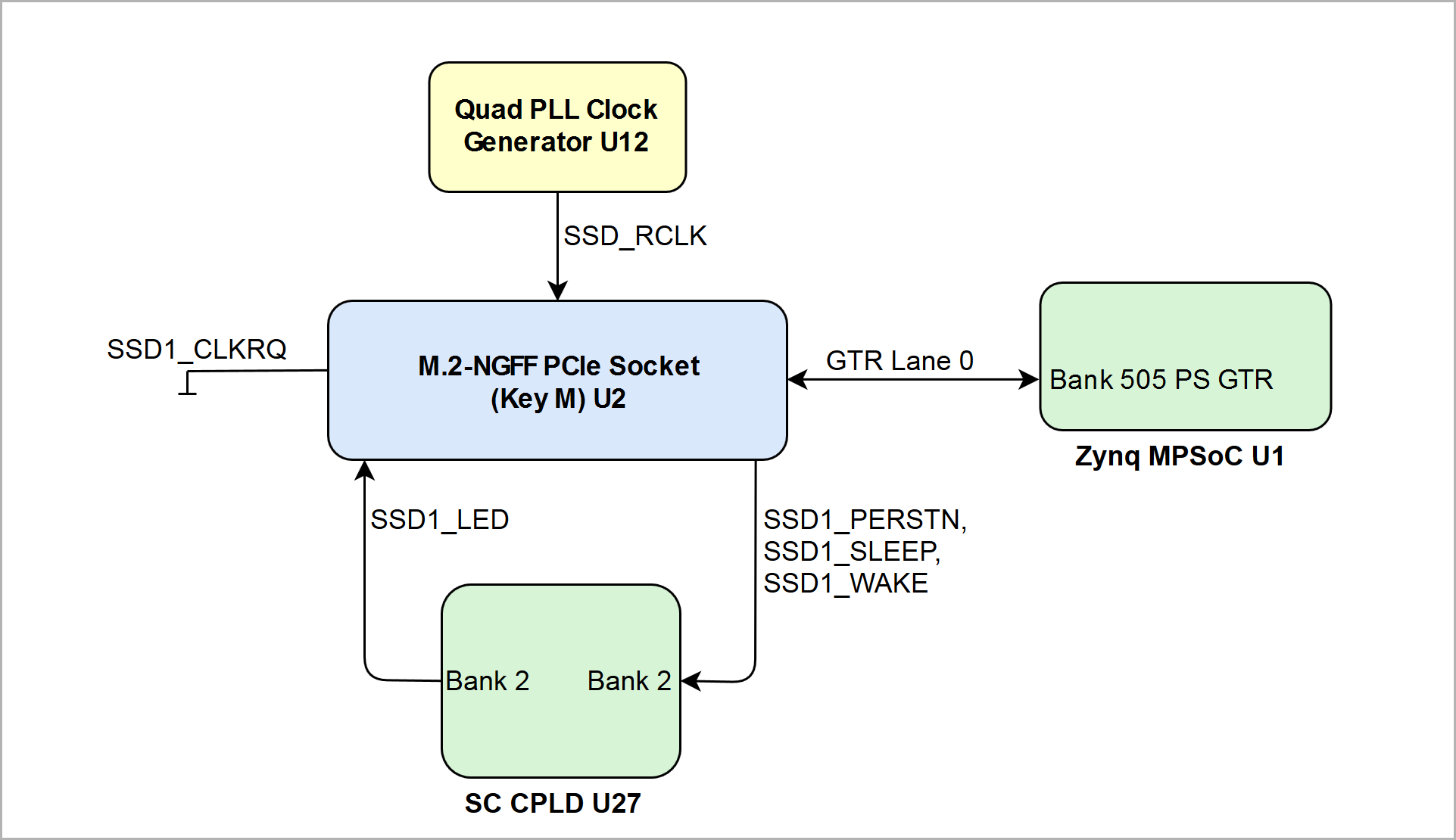

SSD Interface

On the TEB0911 UltraRack board one SSD interface is available provided by a NGFF (Next Generation Form Faktor) M.2 socket (Key M) which supports data transmission rates for PCIe3, SATA3 and USB3 interfaces.

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

| Connector | Interface | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|---|

M.2-NGFF PCIe Socket U2 | MGT Lane |

| PS_MGTRTXP0_505, AB29 | Multi gigabit highspeed TX: Output RX: Input |

| Clock Input |

| Quad programmable PLL clock generator U12, CLK0 | Reference clock signal | |

| Control Lines |

| SC CPLD U27, bank 2, pin AA13 | LED, Output, High active | |

| SC CPLD U27, bank 2, pin AA12 | PCIe sleep state, Input, Low active | ||

| SC CPLD U27, bank 2, pin AA11 | PCIe reset, Input, Low active | ||

| SC CPLD U27, bank 2, pin AB11 | PCIe Link reactivation, Input, Low active | ||

| connect to GND | PCIe Clock Request, Low active |

Table 38: SSD signals and interfaces

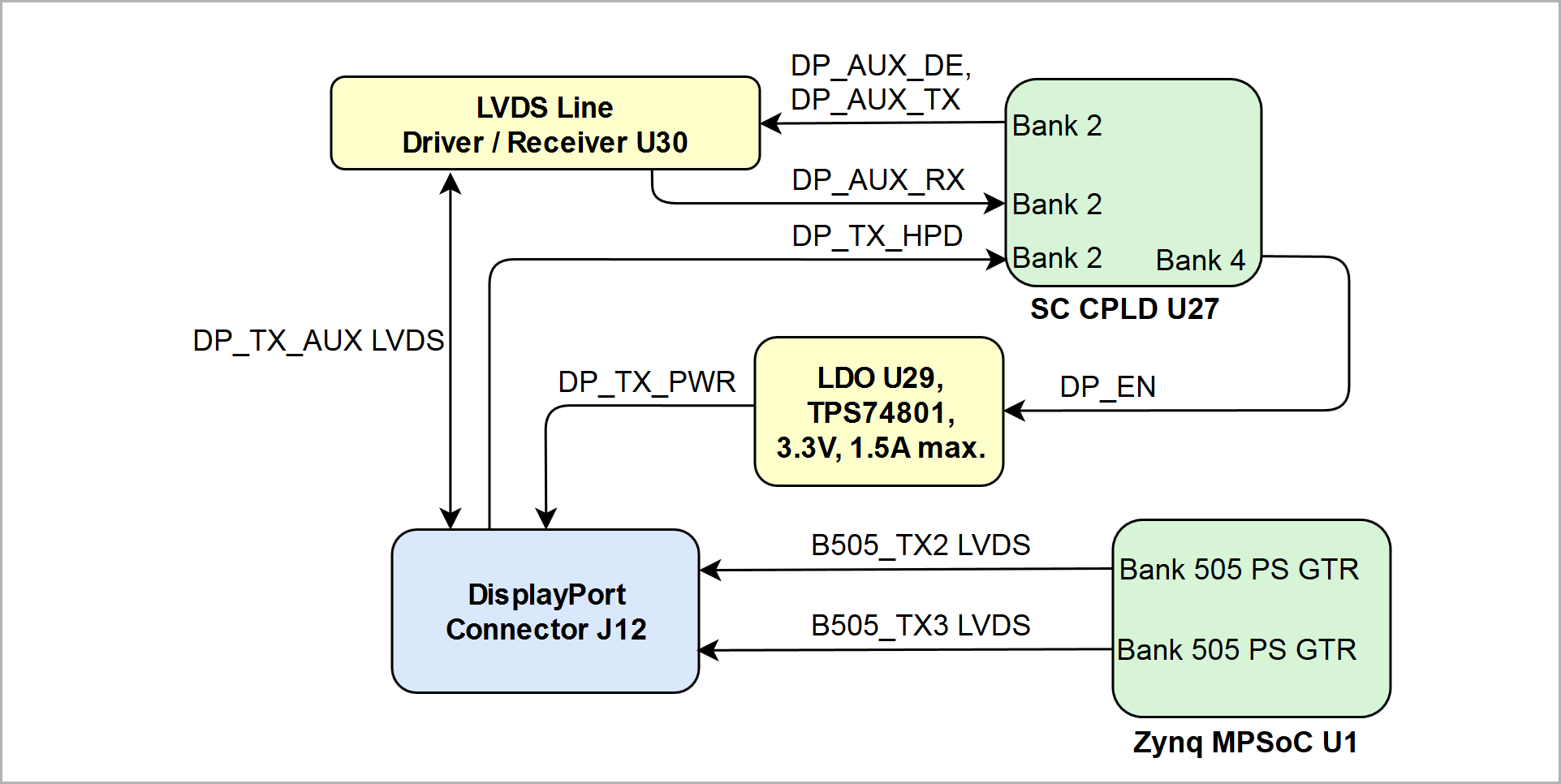

DisplayPort Interface

The TEB0911 board provides the high speed DisplayPort interface for visual output. The DisplayPort is connected with two transmit LVDS-pairs of bank 505 PS GTR lanes. Additionally the auxiliary transmit line is established by the SC CPLD in conjunction with a LVDS Line Driver/Receiver.

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Follwowing table contains a brief description of the MGT lanes and control and status signals of the DisplayPort interface:

| Connector | Interface | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|---|

DisplayPort Connector J12 | MGT Lane |

| PS_MGTRTXP2_505, W31 | Multi gigabit highspeed TX: Output RX: Input |

| Auxiliary Line |

| LVDS Line Driver/Receiver, U30 | Convert signal from single ended to LVDS Single ended signals: 'DP_AUX_TX', 'DP_AUX_RX', | |

| Control Lines |

| SC CPLD U27, bank 2, pin AA15 | DisplayPort Hot Plug Detect | |

| LDO U29 | 3.3V Supply Voltage for DisplayPort |

Table 39: DisplayPort signals and interfaces

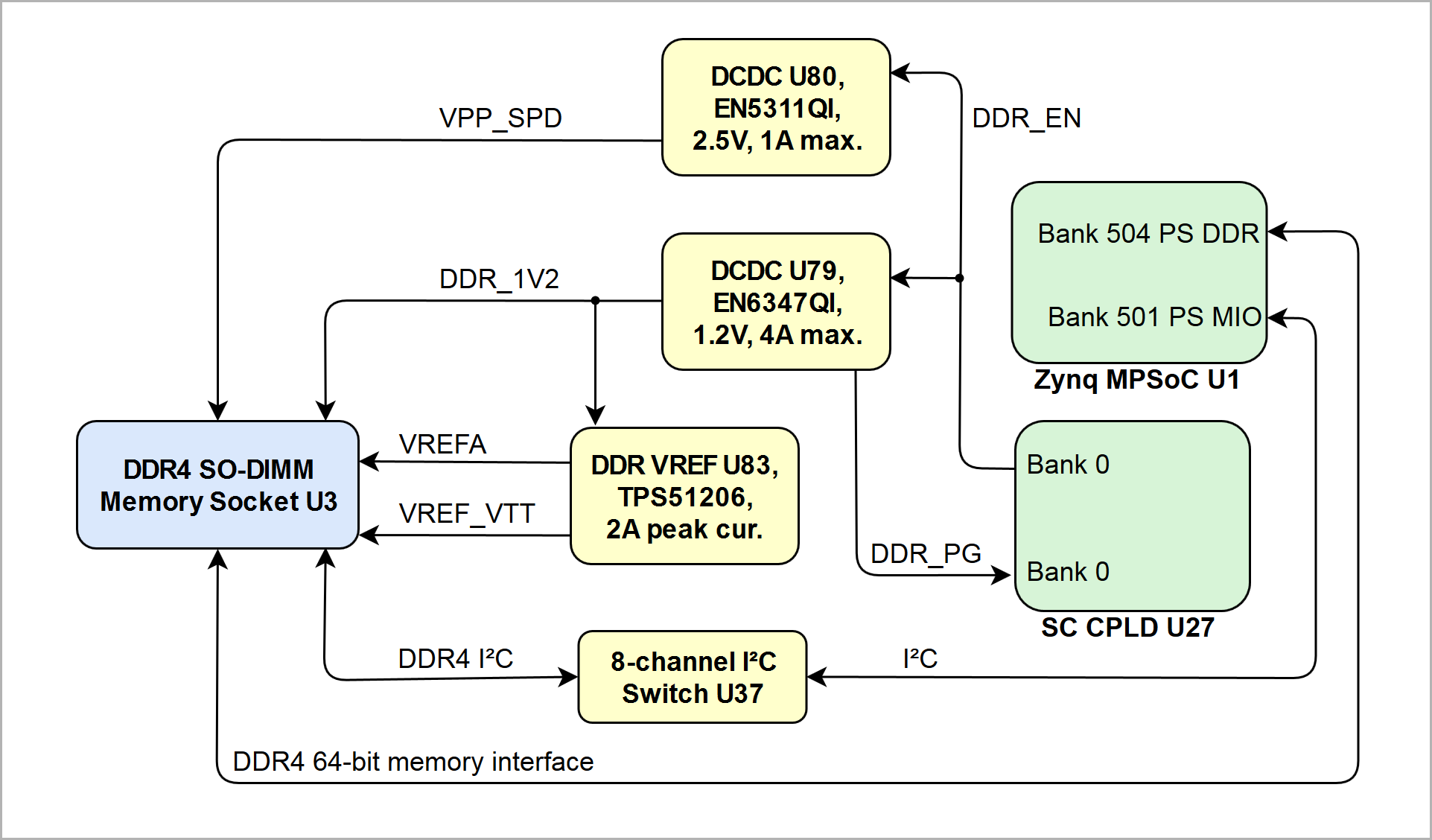

DDR4 Memory Socket

On the TEB0911 board there is a DDR4 memory interface with a 64-bit databus width available for SO-DIMM modules.

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Following table gives an overview about the I/O signals of the DDR4 SDRAM memory interface:

| Connector | DDR4 SDRAM I/O Signal | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|---|

DDR4 SO-DIMM Socket U13 | Address inputs |

| PS DDR Bank 504 | - |

| Bank address inputs |

| - | ||

| Bank group inputs |

| - | ||

| Differential clocks |

| 2 x DDR4 clock | ||

| Data input/output |

| - | ||

| Check bit input/output |

| - | ||

| Data strobe (differential) |

| - | ||

| Data mask and data bus inversion |

| - | ||

| Serial address inputs |

| address range configuration on I²C bus | ||

| Control Signals |

| chip selest signal | ||

| On-die termination enable | |||

| nRESET | |||

| Command and address parity input | |||

| Clock enable | |||

| CRC error flag | |||

| Activation command input | |||

| Temperature event | |||

| I²C |

| 8-channel I²C switch U37 | - |

Table 40: DDR4 64-bit memory interface signals and pins

Refer to the Xilinx Zynq UltraScale+ datasheet DS925 for more information on whether the specific package of the Zynq UltraScale+ MPSoC supports the maximum data transmission rate of 2400 MByte/s, which also depends on the used SO-DIMM module.

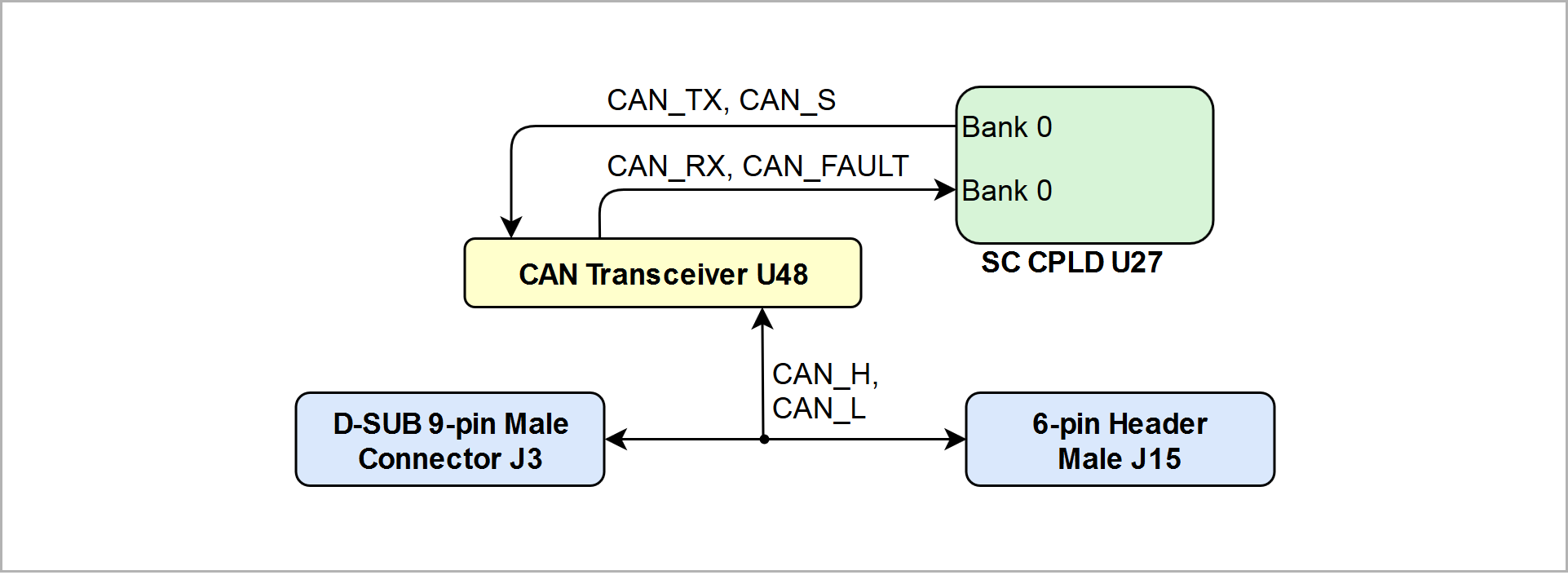

CAN Interface

The TEB0911 board provides a CAN interface, the CAN transceiver is connected and operated by the SC CPLD:

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

The CAN interface of external devices can be connected via D-SUB 9-pin male connector J3 or to the 6-pin male header J15:

| Connector | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|

D-SUB 9-pin J3 |

| CAN Transceiver U48, pin 7 | - |

| CAN Transceiver U48, pin 6 | - | |

6-pin male header J15 |

| CAN Transceiver U48, pin 7 | - |

| CAN Transceiver U48, pin 6 | - | |

| CAN Transceiver | Signal Schematic Name | Connected to | Notes |

| TCAN337 U48 |

| SC CPLD U27, bank 0, pin C16 | 3.3V VCCIO |

| SC CPLD U27, bank 0, pin B15 | 3.3V VCCIO | |

| SC CPLD U27, bank 0, pin C15 | 3.3V VCCIO | |

| SC CPLD U27, bank 0, pin D15 | 3.3V VCCIO |

Table 41: CAN interface signals and pins

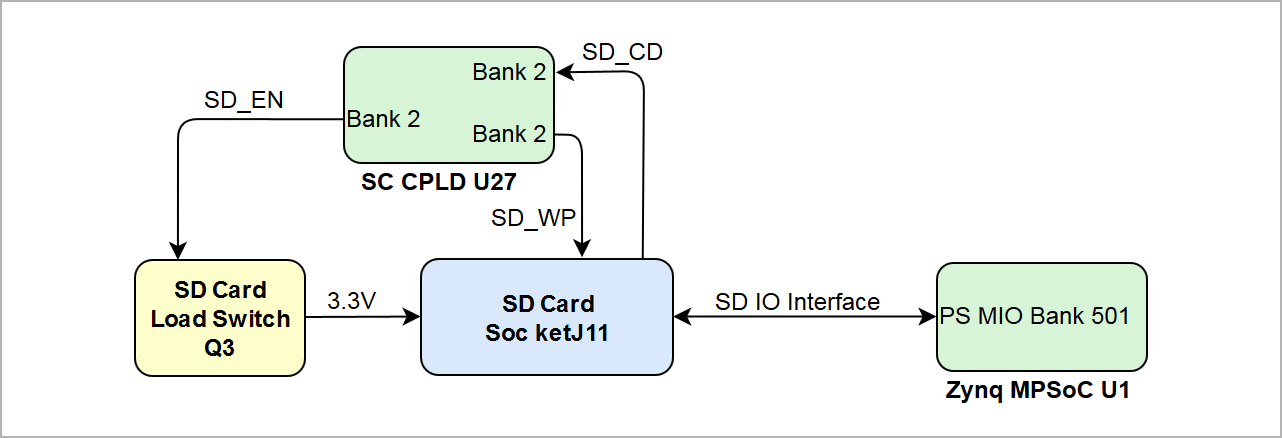

SD Card Interface

The SD Card interface of the TEB0911 board is routed via SD IO interface to the PS MIO bank 501 of the Zynq Ultrascale+ MPSoC (3.3V VCCO). The SC CPLD U27 controls the load switch Q3 to enable the card sockets J11 with signal 'SD_EN', bank 2, pin U11. The "Card Detect" and "Write Protect" signal are also routed to the SC CPLD:

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

The SD Card socket have following signal and pin assignment:

| Connector | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|

SD Card Socket J11 |

| PS bank 501 Pins: MIO46 ... MIO51 | - |

| - | ||

| - | ||

| - | ||

| - | ||

| - | ||

| SC CPLD U27, bank 2, pin T11 | Card Detect | |

| SC CPLD U27, bank 2, pin T10 | Write Protect |

Table 42: SD Card interface signals and connections

4-Wire PWM FAN Connectors

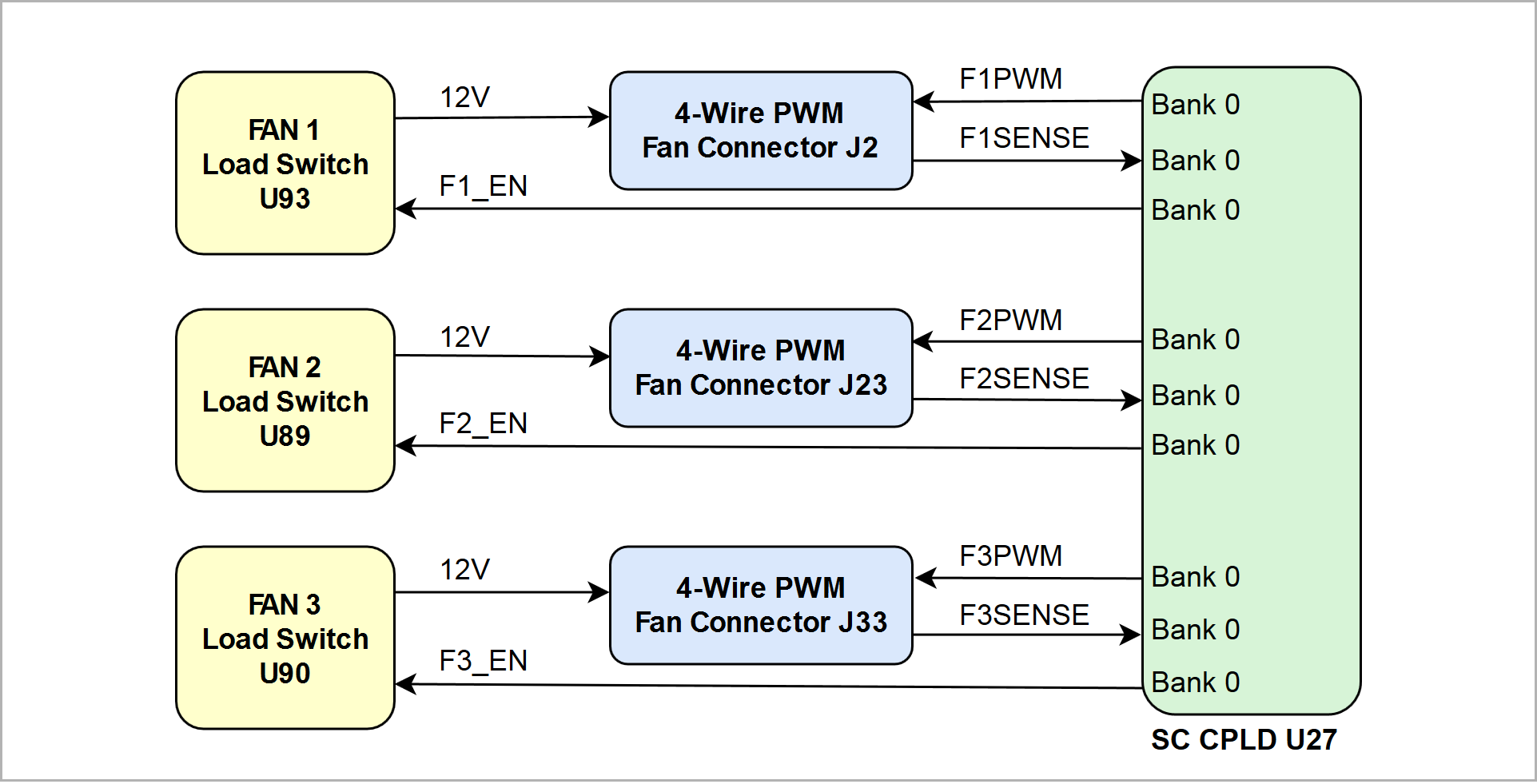

The TEB0911 offers 3x 4-wire PWM FAN connectors for optional cooling fans controlled by SC CPLD U27:

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Following table contains a brief description of the control signals of the fan connectors:

| Connector | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|

Fan Connector J2 |

| SC CPLD U27, bank 0, pin E10 | PWM signal to fan |

| SC CPLD U27, bank 0, pin D11 | sense RPM signal of fan | |

| SC CPLD U27, bank 0, pin C8 | enable 12V fan supply voltage | |

Fan Connector J23 |

| SC CPLD U27, bank 0, pin D9 | PWM signal to fan |

| SC CPLD U27, bank 0, pin G12 | sense RPM signal of fan | |

| SC CPLD U27, bank 0, pin B4 | enable 12V fan supply voltage | |

Fan Connector J33 |

| SC CPLD U27, bank 0, pin B13 | PWM signal to fan |

| SC CPLD U27, bank 0, pin A13 | sense RPM signal of fan | |

| SC CPLD U27, bank 0, pin A12 | enable 12V fan supply voltage |

Table 43: 4-wire PWM fan connectors signals and pins

PLL Clock Interfaces

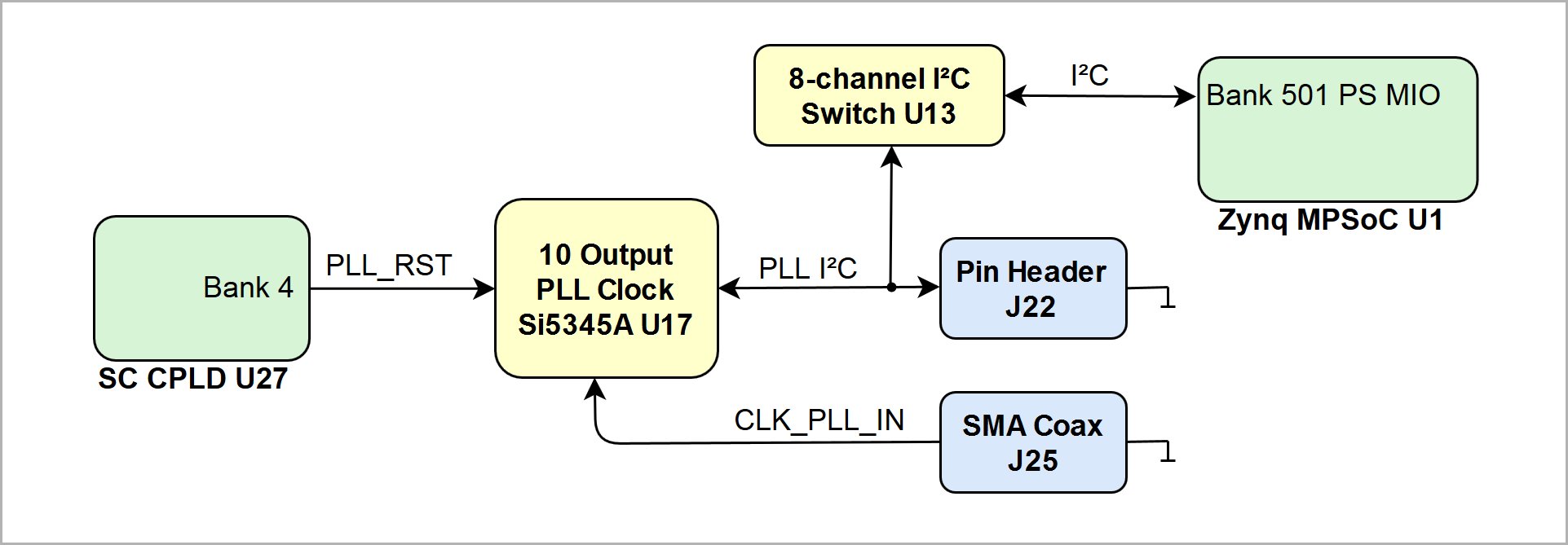

The programmable 10-output reference clock generator U17 can be accessed through its I²C interface to be programed. The I²C interface is connected to the Zynq MPSoc via I²C switch U13 and to pin header J22.

With the SMA Coaxial connector J25 the clock generator can be supplied with an external clock signal.

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

| Connector | Signal Schematic Name | Connected to | Notes |

|---|---|---|---|

Pin Header J22 |

| clock generator U17, pin 16 | PS_1V8 VCCIO |

| clock generator U17, pin 18 | ||

SMA Coax J25 |

| clock generator U17, pin 1 | - |

Table 44: Clock generator Si5345A external interfaces

On-board Peripherals

| HTML |

|---|

<!--

Components on the Module, like Flash, PLL, PHY...

--> |

System Controller CPLD

The TEB0911 UltraRack is equipped with one System Controller CPLDs - Lattice Semiconductor LCMXO2-7000HC (MachXO2 Product Family) with the schematic designators U27. The SC-CPLD is the central system management unit where essential control signals are logically linked by the implemented logic in CPLD firmware, which generates output signals to control the system, the on-board peripherals and the interfaces. Interfaces like JTAG and I2C between the on-board peripherals and to the FPGA module are by-passed, forwarded and controlled by the System Controller CPLD.

Other tasks of the System Controller CPLD are the monitoring of the power-on sequence and to display the programming state of the FPGA module. The functionalities and configuration of the pins depend on the CPLDs' firmware. The documentations of the firmware of SC CPLD U27 contains detailed information on this matter.

The Sytem Controller CPLDs are connected to the Zynq Ultrascale+ MPSoC through MIO and PL pins. The signals of these pins are forwarded by the SC CPLD to control some of the on board peripherals.

Following block diagram visualizes the connection of the SC CPLDs with the Zynq Ultrascale+ MPSoC via PS MIO pins and singled ended PL pins:

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

For detailed information about the current function of the MIO-pin in conjunction with the SC CPLD, the internal signal assignment and implemented logic, refer to the Wiki reference page of the SC CPLD firmware of this board or into the bitstream file of the SC CPLD.

The PS_1V8 and VCCINT_0V85 voltage levels are monitored by the voltage monitor circuit U89, which generates the POR_B signal to reset the board if voltage failure occurs. A manual resetis also possible by driving the pin 'MR' on SC CPLD, bank 4, pin L7 to GND. Refer to documentation of the SC CPLD firmware for detailed information to reset the board manually.

| HTML |

|---|

<!--

Put in link to the Wiki reference page of the firmware of the SC CPLD.

--> |

| HTML |

|---|

<!--

For the detailed function of the pins and signals, the internal signal assignment and implemented logic, look to the Wiki reference page SC CPLD of this module or into the bitstream file of the SC CPLD.

Add link to the Wiki reference page of the SC CPLD, if available.

--> |

High-speed USB2 ULPI PHY

USB2 PHY U15 is provided by USB3320 from Microchip. The ULPI interface is connected to the Zynq Ultrascale+ PS USB0. I/O voltage is fixed at 1.8V and PHY reference clock input is supplied from the on-board 52.000000 MHz oscillator U16.

| PHY Pin | Connected to | Notes |

|---|---|---|

| ULPI | PS bank MIO52 ... MIO63 | Zynq Ultrascale+ USB0 MIO pins are connected to the PHY |

| REFCLK | - | 52MHz from on board oscillator U16 |

| REFSEL[0..2] | - | All pins set to GND selects the external reference clock frequency (52.000000 MHz) |

| RESETB | SC CPLD U27, bank 4, Pin: M2 | Low active USB2 PHY Reset (pulled-up to PS_1.8V) |

| DP, DM | 4-port USB3 Hub U4 | USB2 data lane |

| CPEN | - | External USB power switch active-high enable signal |

| VBUS | 5V | Connected to USB VBUS via a series of resistors, see schematic |

| ID | - | For an A-device connect to the ground. For a B-device, leave floating |

Table 45: USB PHY interface connections

4-port USB3 Hub

On the TEB0911 board there are to 2 USB3 Super Speed ports available, which are also downward compatible to USB2 High Speed ports. The USB3 ports are provided by Cypress Semiconductor CYUSB3324 4-port USB3 Hub controller U4. The pin-strap configuration option of the USB3 Hub is disabled, so this controller gets the configuration data and parameter from the configuration EEPROM U5. The I²C interface of the EEPROM and the controller are also accessible by the Zynq Ultrascale+ MPSoC through I²C switch U37.

On the Upstream-side, this controller is connected to the MGT1 lane of MPSoC's PS GT bank 505 to establish the USB3 data lane. For the USB2 interface, the controller is connected to the on-board USB2 PHY U15. The USB2 PHY is connected via ULPI interface (MIO pins 52..63) to MPSoC's MIO bank.

The USB3 Hub controller has also an ARM Cortex-M0 controller integrated, refer to the data sheet for further features and programmable options.

Gigabit Ethernet PHY

On-board Gigabit Ethernet PHY U20 is provided with Marvell Alaska 88E1512. The Ethernet PHY RGMII interface is connected to the Zynq Ultrascale+ Ethernet0 PS GEM3. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from the on-board 25.000000 MHz oscillator U21. The 125MHz PHY output clock (PHY_CLK125M) is routed to System Controller CPLD U27, bank 4, pin K2.

8-Channel I²C Switches

All on-board and on-module peripherals with accessible I²C interface are muxed to the I²C interface of the Zynq Ultrascale+ MPSoC as master.

For this purpose, the TEB0911 board is equipped with two 8-channel I²C switches provided by TCA9548A from Texas Instruments, together creating up to 16 switched I²C channels.

Refer to the data sheet of the TCA9548A chip how to address and and transmit data to the I²C slave devices through this switches.

The on-board I2C bus works with reference voltage 3.3V, it is connected to the MPSoC I2C interface via PS MIO bank (pins MIO38, MIO39) and configured as master.

| MIO | Signal Schematic Name | Notes |

|---|---|---|

| 38 |

| 3.3V reference voltage |

| 39 |

| 3.3V reference voltage |

Table 46: MIO-pin assignment of the module's I2C interface

| Info |

|---|

| The I²C switches can be reseted simultanously by the pin 'I2C_RST', which is connected to SC CPLD U27, bank 4 pin L2 with low active logic. |

I2C addresses (7 bit without read/write-bit) for on-board slave devices are listed in the table below:

| I²C Slave Devices connected to MPSoC I²C Interface | I²C Switch Position | I²C Slave Address | Schematic Names of I²C Bus Lines |

|---|---|---|---|

| 8-channel I²C switch U13 | - | 0x76 |

|

| 8-channel I²C switch U37 | - | 0x77 |

|

| I²C Slave Devices connected to 8-channel I²C Switch U13 | I²C Switch Position | I²C Slave Address | Schematic Names of I²C Bus Lines |

| FMC Connector J7 (FMC D) | 2 | 0x50 |

|

| FMC Connector J6 (FMC E) | 3 | 0x50 |

|

| FMC Connector J4 (FMC B) | 4 | 0x50 |

|

| FMC Connector J8 (FMC C) | 5 | 0x50 |

|

| PLL clock generator U17 Si5345A | 6 | 0x69 |

|

| I²C Slave Devices connected to 8-channel I²C Switch U37 | I²C Switch Position | I²C Slave Address | Schematic Names of I²C Bus Lines |

| FMC Connector J10 (FMC A) | 1 | 0x50 |

|

| FMC Connector J21 (FMC F) | 2 | 0x50 |

|

| SFP+ Connector J9A | 3 | 0x50 / 0x51 |

|

| 8-bit I²C IO Expander U86 (SPF+ connector control signals) | 3 | 0x27 |

|

| SFP+ Connector J9B | 4 | 0x50 / 0x51 |

|

| PLL clock generator U12 Si5338A | 5 | 0x70 |

|

| Configuration EEPROM U83 | 5 | 0x51 |

|

| Configuration EEPROM U45 | 5 | 0x52 |

|

| Configuration EEPROM U60 | 5 | 0x53 |

|

| Configuration EEPROM U57 | 5 | 0x57 |

|

| SC CPLD U27 | 5 | user configurable |

|

| DDR4 SODIMM I²C interface | 6 | module dependent |

|

| USB3 Hub U4 | 7 | 0x60 |

|

| USB3 Hub configuration EEPROM U5 | 7 | 0x51 |

|

Table 46: On-board peripherals' I2C-interfaces device slave addresses

Configuration EEPROMs

The TEB0911 carrier board contains several EEPROMs for configuration and general user purposes. The EEPROMs are provided by Microchip, the I²C interfaces of the EEPROM's are multiplexed to the I²C switch U37:

| EEPROM Modell | Designator | Memory Density | Purpose |

|---|---|---|---|

| 24LC128-I/ST | U57 | 128 Kbit | user |

| 24AA025E48T-I/OT | U60 | 2 Kbit | user |

| 24AA025E48T-I/OT | U45 | 2 Kbit | user |

| 24AA025E48T-I/OT | U83 | 2 Kbit | user |

| 24LC128-I/ST | U5 | 128 Kbit | USB3 Hub U4 configuration memory |

Table 47: On-board configuration EEPROMs overview

CAN FD Transceiver

On-board CAN FD (Flexible Data Rate) transceiver U48 is provided by Texas Instruments TCAN337. This controller is the physical layer of the CAN interface and is specified for data rates up to 1 Mbps. The controller has many protection features included to ensure CAN network robustness and to eliminate the need for additional protection circuits. Refer to the data sheet of this transceiver for more details and specifications.

The transceiver is connected to System Controller CPLD U27, means it works on this interface with 3.3V VCCIO. The logical signal processing of the CAN interface depends on the current firmware ot the SC CPLD.

On-board Flash Memory

On-board QSPI flash memory U24 and U25 on the TEB0911 board is provided by Micron Serial NOR Flash Memory N25Q256A with 256 Mbit (32 MByte) storage capacity each. The QSPI Flash memory ICs are connected to the PS MIO bank (Dual QSPI MIO0 ... MIO12) of the Zynq Ultrascale+ MPSoC. This non volatile memory is used to store initial FPGA configuration. Besides FPGA configuration, remaining free flash memory can be used for user application and data storage. All four SPI data lines are connected to the Zynq MPSoC allowing x1, x2 or x4 data bus widths. Maximum data rate depends on the selected bus width and clock frequency used.

The TEB0911 board is also equipped with embedded MMC memory connected to the PS MIO bank (MIO13 ... MIO23) of the Zynq Ultrascale+ MPSoC. The memory is provided by MTFC4GACAJCN-4M IT from Micron Technology. It has a memory density of 32 Gbit (4 GByte) and is sectored into 8 banks a 4 Gbit.

| IC | Name | Memory Density | Connected to | Notes |

|---|---|---|---|---|

| QSPI Flash U24 | N25Q256A11E1240E | 256 Mbit (32 MByte) | QSPI0: MIO0 ... MIO5 | dual parallel booting possible, 64 MByte total QSPI Flash memory connected via Dual QSPI MIO0 ... MIO12 |

| QSPI Flash U25 | N25Q256A11E1240E | 256 Mbit (32 MByte) | QSPI0: MIO7 ... MIO12 | |

| eMMC Flash U26 | MTFC4GACAJCN-4M IT | 32 Gbit (4 GByte) | SD0 eMMC: MIO13 ... MIO23 | bootable eMMC |

Table 48: On-board Flash memory ICs overview

Quad SPI Flash memory ICs U24 and U25 are connected to the Zynq MPSoC PS QSPI0 interface via PS MIO bank 500, pins MIO0 ... MIO5 and MIO7 ... MIO12.

eMMC Flash memory IC U25 is connected to Zynq MPSoC by pins MIO13 ... MIO23.

| MIO | Signal Schematic Name | Flash U24 Pin | MIO | Signal Schematic Name | Flash U25 Pin | MIO | Signal Schematic Name | Flash U26 Pin | ||

|---|---|---|---|---|---|---|---|---|---|---|

| 0 |

| B2 | 7 |

| C2 | 13 |

| H3 | ||

| 1 |

| D2 | 8 |

| D3 | 14 |

| H4 | ||

| 2 |

| C4 | 9 |

| D2 | 15 |

| H5 | ||

| 3 |

| D4 | 10 |

| C4 | 16 |

| J2 | ||

| 4 |

| D3 | 11 |

| D4 | 17 |

| J3 | ||

| 5 |

| C2 | 12 |

| B2 | 18 |

| J4 | ||

| 19 |

| J5 | ||||||||

| 20 |

| J6 | ||||||||

| 21 |

| W5 | ||||||||

| 22 |

| W6 | ||||||||

| 23 |

| U5 |

Table 49: PS MIO pin assignment of the Flash memory ICs

| Note |

|---|

SPI Flash QE (Quad Enable) bit must be set to high or FPGA is unable to load its configuration from flash during power-on. By default this bit is set to high at the manufacturing plant. |

Oscillators

The TEB0911 board is equipped several on-board oscillators to provide the Zynq Ultrascale+ MPSoC's PS and PL banks and the on-board peripherals with reference clock-signals:

| Clock Source | Signal Schematic Name | Frequency | Clock Input Destination |

|---|---|---|---|

| SiTime SiT8008BI oscillator, U22 |

| 33.333333 MHz | Zynq MPSoC PS Config Bank 503, pin U24 |

| SiTime SiT8008AI oscillator, U16 |

| 52.000000 MHz | USB2 transceiver PHY U15, pin 26 |

| Kyocera CX3225SB26000, Y3 | - | 26.000 MHz | 4-port USB3 Hub U4, pin 68/69 |

| Kyocera CX3225SB26000, Y2 |

| 54.000 MHz | PLL clock generator U17, pin 8/9 |

| SiTime SiT8008BI oscillator, U21 |

| 25.000000 MHz | Gigabit Ethernet PHY U20, pin 34 |

SiTime SiT8008AI oscillator, U87 optional, not equipped |

| 25.000000 MHz | System Controller CPLD U27, bank 2, pin AA9 |

| SiTime SiT8008BI oscillator, U18 |

| 25.000000 MHz | PLL clock generator U17, pin 63 |

| SiTime SiT8008AI oscillator, U85 | - | 25.000000 MHz | PLL clock generator U12, pin 3 |

DSC1123 oscillator, U92 optional, not equipped |

| 100.0000 MHz | PS GTR Bank 505 Lane 3, dedicated for DisplayPort, pin U31, U32 |

Table 50: Reference clock signal oscillators

Programmable Clock Generator Si5338A

There is a Si5338A U12, Silicon Labs I2C programmable quad PLL clock generator on-board to generate various reference clocks for the Zynq MPSoC MGT banks and on-board peripherals.

| Si5338A Pin | Signal Schematic Name | Connected to | Clock Direction | Note |

|---|---|---|---|---|

IN1 |

| U17, pin 54 | Input | Differential reference clock input from PLL clock generator U17 |

| IN2 |

| U17, pin 53 | Input | |

IN3 | - | U85, pin 3 | Input | 25.000000 MHz oscillator, Si8008AI |

IN4 | - | GND | Input | LSB (pin 'IN4') of the default I²C-adress 0x70 not set |

IN5 | - | Not connected | Input | Not used |

| IN6 | - | GND | Input | Not used |

CLK0A |

| U2, pin 55 | Output | NGFF M.2 PCIe socket (Key M), |

| CLK0B |

| U2, pin 53 | Output | |

| CLK1A |

| U1, pin U27 | Output | PS GTR Bank 505 Lane 2 |

| CLK1B |

| U1, pin U28 | Output | |

| CLK2A |

| U1, pin W27 | Output | PS GTR Bank 505 Lane 1 |

| CLK2B |

| U1, pin W28 | Output | |

| CLK3A |

| U1, pin AA27 | Output | PS GTR Bank 505 Lane 0 |

| CLK3B |

| U1, pin AA28 | Output |

Table 51: Programmable quad PLL clock generator inputs and outputs

Programmable Clock Generator Si5345A

Following table shows on-board Silicon Labs I2C programmable Si5345A U17 10-output programmable PLL reference clock generator inputs and outputs:

| Si5345A Pin | Signal Schematic Name | Connected to | Clock Direction | Note |

|---|---|---|---|---|

| IN0 |

| not connected | Input | Not used |

| GND | |||

| IN1 |

| SMA Coax J25, pin 1 | Input | external reference clock input |

| GND | |||

| IN2 | - | not connected | Input | not used |

| - | not connected | |||

| IN3 | - | not connected | Input | not used |

| - | not connected | |||

| OUT0 |

| not connected | Output | not used |

| not connected | |||

| OUT1 |

| U1, pin E8 | Output | GTH bank 229 reference clock input |

| U1, pin E7 | |||

| OUT2 |

| U1, pin B10 | Output | GTH bank 230 reference clock input |

| U1, pin B9 | |||

| OUT3 |

| U1, pin J8 | Output | GTH bank 228 reference clock input |

| U1, pin J7 | |||

| OUT4 |

| U1, pin N27 | Output | GTH bank 128 reference clock input |

| U1, pin N28 | |||

| OUT5 |

| U1, pin J27 | Output | GTH bank 129 reference clock input |

| U1, pin J28 | |||

| OUT6 |

| U1, pin E27 | Output | GTH bank 130 reference clock input |

| U1, pin E28 | |||

| OUT7 |

| U27, pin E1 | Output | Clock signal input to SC CPLD, bank 5 |

| not connected | |||

| OUT8 |

| U12, pin 2 | Output | Differential reference clock input to |

| U12, pin 1 | |||

| OUT9 | - | not connected | Output | not used |

| - | not connected | |||

| XA/XB |

| 54.000 MHz quartz oscillator Y1 | Input | Differential quartz oscillator clock input |

|

Table 52: Programmable 10-output PLL clock generator inputs and outputs

| Info |

|---|

The PLL clock generator U17 can be resetted by the low active pin 'PLL_RST' connected to SC CPLD U27, bank 4, pin L4. The on-board header J22 provides the possibility to program the clock generator U17 via I²C bus (1.8V reference voltage). |

On-board LEDs

The TEB0911 board is equipped with several LEDs to signal current states and activities.

| LED | Color | Connected to | Description and Notes |

|---|---|---|---|

| D6 | red | Zynq MPSoC U1, pin W21 | Reflects inverted DONE signal. ON when FPGA is not configured, |

| D17 | green | USB3 Hub U4, pin 25 | LED is on if all USB3 and USB2 ports are in the suspend state and is |

| D18 | green | USB3 Hub U4, pin 4 | LED output for downstream 1 port. |

| D19 | green | USB3 Hub U4, pin 63 | LED output for downstream 3 port. |

| D2 | red | SC CPLD U27, bank 2, pin AB17 | SFP+ interface status. The LEDs are fitted on-board under the SFP+ connector cage. |

| D4 | green | SC CPLD U27, bank 2, pin AB18 | |

| D3 | red | SC CPLD U27, bank 2, pin AA16 | |

| D5 | green | SC CPLD U27, bank 2, pin AB15 | |

| D13 | green | SC CPLD U27, bank 2, pin U12 | functionality depends on the current firmware of the SC CPLD U27 refer to the documentation section: LED |

| D14 | green | SC CPLD U27, bank 2, pin V12 | |

| D15 | green | SC CPLD U27, bank 2, pin W12 | |

| D16 | red | SC CPLD U27, bank 2, pin V13 |

Table 53: On-board LEDs

User Buttons

There are two switch buttons available to the user connected to the SC CPLD U27:

| Button | Connected to | Notes |

|---|---|---|

| S1 | SC CPLD U27, bank 0, pin F13 | high active logic, connected to 3V3SB, functionality depends on the current firmware of the SC CPLD U27 |

| S2 | SC CPLD U27, bank 0, pin G13 |

Table 54: On-board switch buttons

Configuration DIP-switches

There are two 4-bit DIP-witches S3 and S4 present on the TEB0911 board to configure options and set parameters. The following section describes the functionalities of the particular switches.

Table below describes the functionalities of the switches of DIP-switches S3 and S4 at their each positions:

| DIP-switch S3 | Signal Schematic Name | Connected to | Functionality | Notes |

|---|---|---|---|---|

| S3-1 |

| Zynq MPSoC U1, pin AD15 | Positions ON: PUDC_B is Low OFF: PUDC_B is HIGH | Internal pull-up resistors during configuration are enabled at ON-position,means I/O's are 3-stated until configuration of the FPGA completes. |

| S3-2 |

| SC CPLD U27, bank 0, pin A16 | Positions | JTAG interface of the SC CPLD, accessible on XMOD header J35 |

| S3-3 |

| SC CPLD U27, bank 0, pin E17 | set 2-bit code for boot mode selection | TEB0911 CPLD Firmware Documentation Section: Boot Mode |

| S3-4 |

| SC CPLD U27, bank 0, pin D16 | ||

| DIP-switch S4 | Signal Schematic Name | Connected to | Functionality | Notes |

| S4-1 |

| SC CPLD U27, bank 0, pin D18 | user defined | For functionalities of these switches in the current CPLD firmware, refer to the TEB0911 CPLD Firmware Documentation. |

| S4-2 |

| SC CPLD U27, bank 0, pin D16 | ||

| S4-3 |

| SC CPLD U27, bank 0, pin C19 | ||

| S4-4 |

| SC CPLD U27, bank 0, pin C18 |

Table 55: DIP-switch S3 and S4 functionality description

Power and Power-On Sequence

| HTML |

|---|

<!--

If power sequencing and distribution is not so much, you can join both sub sections together

--> |

Power Consumption

The maximum power consumption of the board mainly depends on the design running on the FPGA.

Xilinx provide a power estimator excel sheets to calculate power consumption. It's also possible to evaluate the power consumption of the developed design with Vivado. See also Trenz Electronic Wiki FAQ.

| Power Input | Typical Current |

|---|---|

| 24V VIN | TBD* |

Table 56: Typical power consumption, *to Be Determined soon with reference design setup.

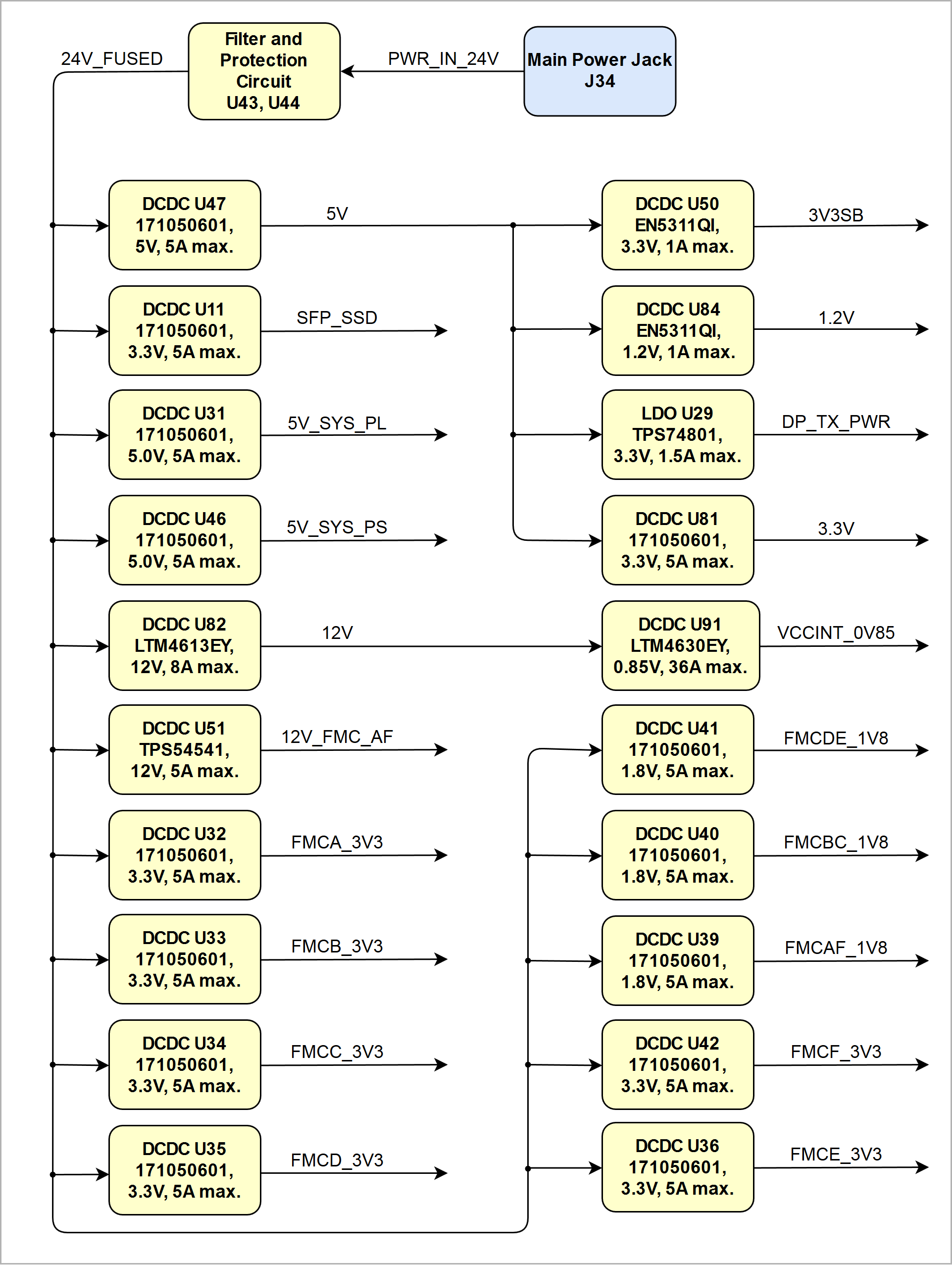

Power supply with minimum current capability of 2A for system startup is recommended. If using all FMC connectors with FPGA Mezzanine Cards, a higher current availability of up to 4A is recommended.

The TEB0911 UltraRack board is equipped with the Xilinx Zynq UltraScale+ MPSoC delivers a heterogeneous multi-processing system with integrated programmable logic and independently operable elements and is designed to meet embedded system power management requirement by advanced power management features. This features allow to offset the power and heat constraints against overall performance and operational efficiency.

This features allowing highly flexible power management are achieved by establishing Power Domains for power isolation. The Zynq UltraScale+ MPSoC has multiple power domains, whereby each power domain requires its own particular on-board DC-DC converters.

The Processing System contains three Power Domains:

- Battery Power Domain (BBRAM and RTC)

- Full-Power Domain (Application Processing Unit, DDR Controller, Graphics Processing Unit and High-Speed Connectivity)

- Low-Power Domain (Real-Time Processing Unit, Security and Configuration Unit, Platform Management Unit, System Monitor and General Connectivity)

- Programmable Logic (PL)

Power Distribution Dependencies

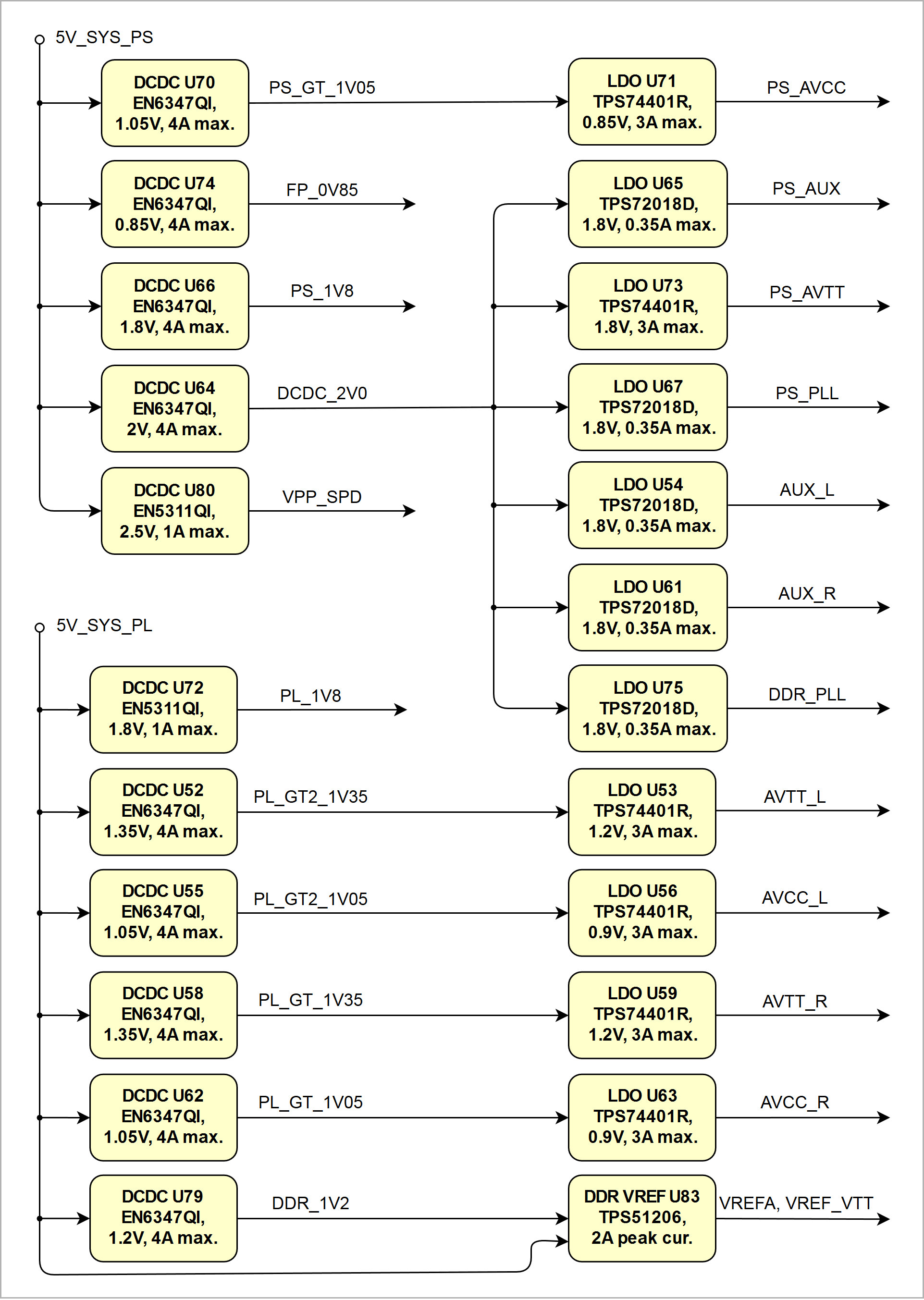

There are following dependencies how the initial 24V voltage from the main power jack J34 is distributed to the on-board DC-DC converters, which power up further DC-DC converters and the particular on-board voltages:

| Scroll Title | ||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||

|

Power distribution to the MPSoC PS and PL units:

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

| Info |

|---|

Note: The DC-DC converter U91 LTM4630EY has an integrated temperature diode for device temperature monitoring. The analog signal 'TEMP_CORE_DC' on pin J6 of the converter is routed to the dedicated differential analog interface (XADC) of the Zynq MPSoC, pin U18 (V_P), pin V17 (V_N) is connected to analog GND. |

| Warning |

|---|

| To avoid any damage to the module, check for stabilized on-board voltages should be carried out(i.e. power good and enable signals) before powering up any SoC's I/O bank voltages VCCO_x. All I/Os should be tri-stated during power-on sequence. |

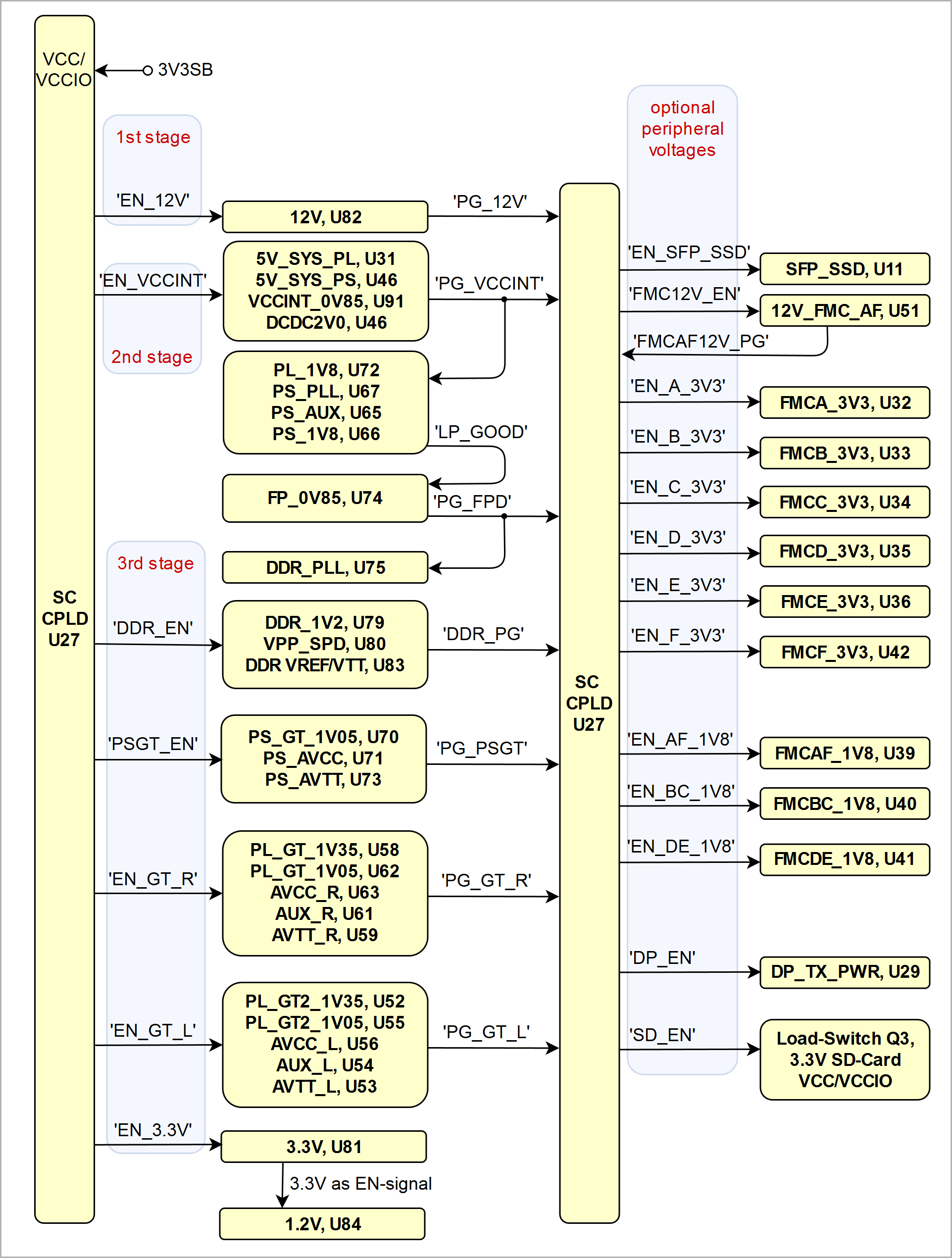

Power-On Sequence

The TEB0911 UltraRack board meets the recommended criteria to power up the Xilinx Zynq UltraScale+ MPSoC properly by keeping a specific sequence of enabling the on-board DC-DC converters dedicated to the particular Power Domains and powering up the on-board voltages.

On the TEB0911 UltraRack board following Power Domains will be powered up in a certain sequence with by enable and power-good signals of the DC-DC converters, which are controlled by the System Controller CPLD U27:

- Low-Power Domain (LPD)

- Programmable Logic (PL) and Full-Power Domain (FPD)

- GTH, PS GTR transceiver and DDR memory

Hence, those three power instances will be powered up consecutively when the Power-Good signals of the previous instance is asserted.

Following diagram describes the sequence of enabling the three power instances utilizing the DC-DC converter control signals (Enable, Power-Good), which will power-up in descending order as listed in the blocks of the diagram.

| Scroll Title | ||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||

|

Power Rails