Page History

...

| Excerpt |

|---|

|

...

| Date | Vivado | Project Built | Authors | Description | ||

|---|---|---|---|---|---|---|

| 2018-0608-1915 | 20172018.42 | TE0820-test_board-vivado_20172018.42-build_1001_2018061916071320180706132853.zip TE0820-test_board_noprebuilt-vivado_20172018.42-build_1001_2018061916072820180706132906.zip | John Hartfiel |

| ||

| 2018-06-19 |

| 2018-05-24 | 2017.4 | TE0820-test_board-vivado_2017.4-build_10_2018052415135620180619160713.zip TE0820-test_board_noprebuilt-vivado_2017.4-build_10_2018052415134220180619160728.zip | John Hartfiel |

|

| 2018-05-24 | 2017.4 | TE0820-test_board-vivado_2017.4-build_10_20180524151356.zip | John Hartfiel |

| ||

| 2018-04-25 | 2017.4 | TE0820-test_board-vivado_2017.4-build_07_20180425134435.zip TE0820-test_board_noprebuilt-vivado_2017.4-build_07_20180425134459.zip | John Hartfiel |

| ||

| 2018-02-06 | 2017.4 | TE0820-test_board-vivado_2017.4-build_06_20180206203359.zip TE0820-test_board_noprebuilt-vivado_2017.4-build_06_20180206203414.zip | John Hartfiel |

| ||

| 2018-02-01 | 2017.4 | TE0820-test_board-vivado_2017.4-build_05_20180201084319.zip TE0820-test_board_noprebuilt-vivado_2017.4-build_05_20180201094724.zip | John Hartfiel |

| ||

| 2018-01-24 | 2017.4 | TE0820-test_board-vivado_2017.4-build_05_20180124085247.zip TE0820-test_board_noprebuilt-vivado_2017.4-build_05_20180124085303.zip | John Hartfiel |

| ||

| 2017-11-21 | 2017.2 | TE0820-test_board-vivado_2017.2-build_05_20171121160552.zip TE0820-test_board_noprebuilt-vivado_2017.2-build_05_20171121160606.zip | John Hartfiel |

| ||

| 2017-11-20 | 2017.2 | TE0820-test_board-vivado_2017.2-build_05_20171120162931.zip TE0820-test_board_noprebuilt-vivado_2017.2-build_05_20171120162851.zip | John Hartfiel |

| ||

| 2017-10-19 | 2017.2 | TE0820-test_board-vivado_2017.2-build_05_20171019104824.zip TE0820-test_board_noprebuilt-vivado_2017.2-build_05_20171019104837.zip | John Hartfiel |

|

...

| Software | Version | Note |

|---|---|---|

| Vivado | 20172018.42 | needed |

| SDK | 20172018.42 | needed |

| PetaLinux | 20172018.42 | needed |

| SI5338 Clock Builder | --- | optional |

...

- Connect JTAG and power on carrier with module

- Open Vivado Project with "vivado_open_existing_project_guimode.cmd" or if not created, create with "vivado_create_project_guimode.cmd"

- Type on Vivado TCL Console: TE::pr_program_flash_binfile -swapp u-boot

Note: To program with SDK/Vivado GUI, use special FSBL (zynqmp_fsbl_flash) on setup

optional "TE::pr_program_flash_binfile -swapp hello_te0820" possible - Copy image.ub on SD-Card

- For correct prebuilt file location, see <design_name>/prebuilt/readme_file_location.txt

- Insert SD-Card

...

- Prepare HW like described on section Programming

- Connect UART USB (most cases same as JTAG)

- Select SD Card or QSPI as Boot Mode (Depends on used programming variant)

Note: See TRM of the Carrier, which is used. - Power On PCB

Note: 1. ZynqMP Boot ROM loadsPMU loads PMU Firmware and FSBL from SD/QSPI Flash into OCM, 2. FSBL loads ATF(bl31.elf) and U-boot from SD into DDR, 3. U-boot load Linux from SD into DDR

...

SI5338 CLK is configured to 200MHz by default.

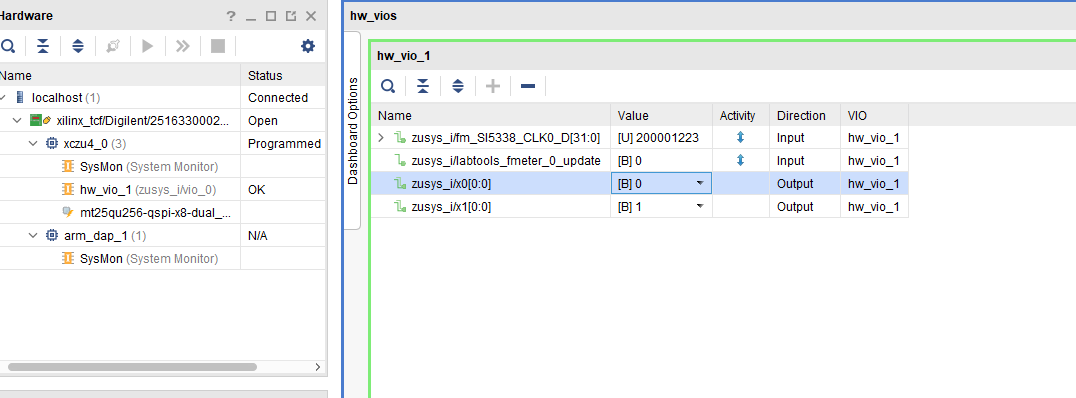

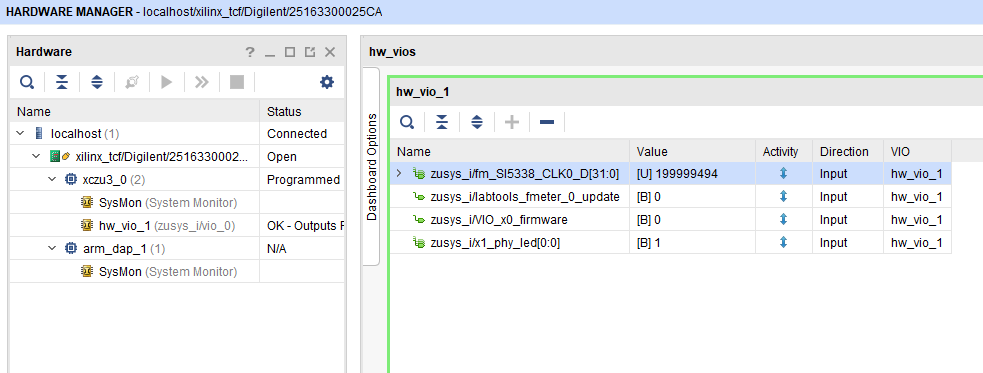

PCB REV03 Design:

- User LED, see: TE0820 CPLD#LED

PCB REV01, REV02 Design:

- PHY LEDS

...

- See, see: TE0820-REV01_REV02 CPLD#X0/X1Pin

- CPLD Firmware, see:

...

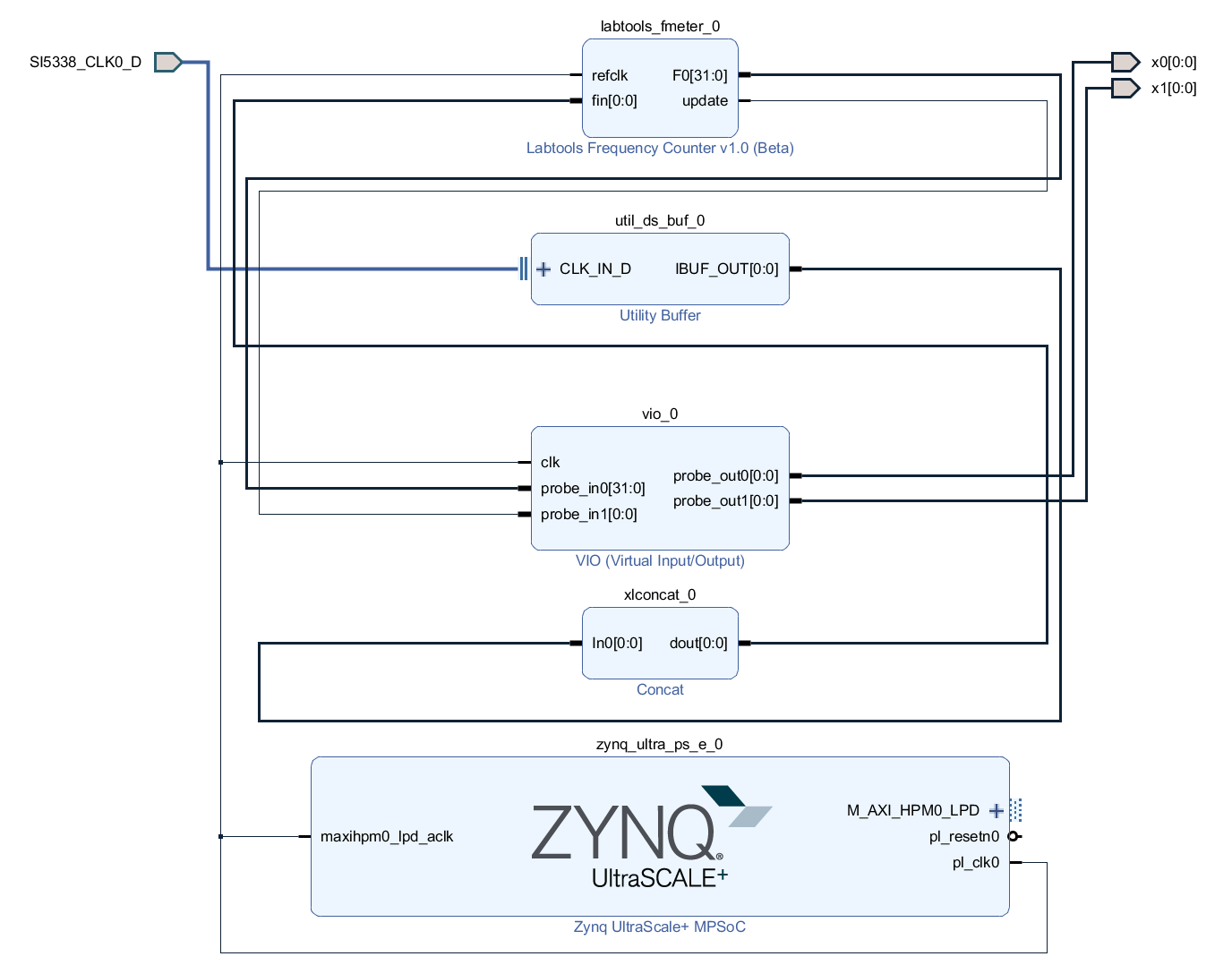

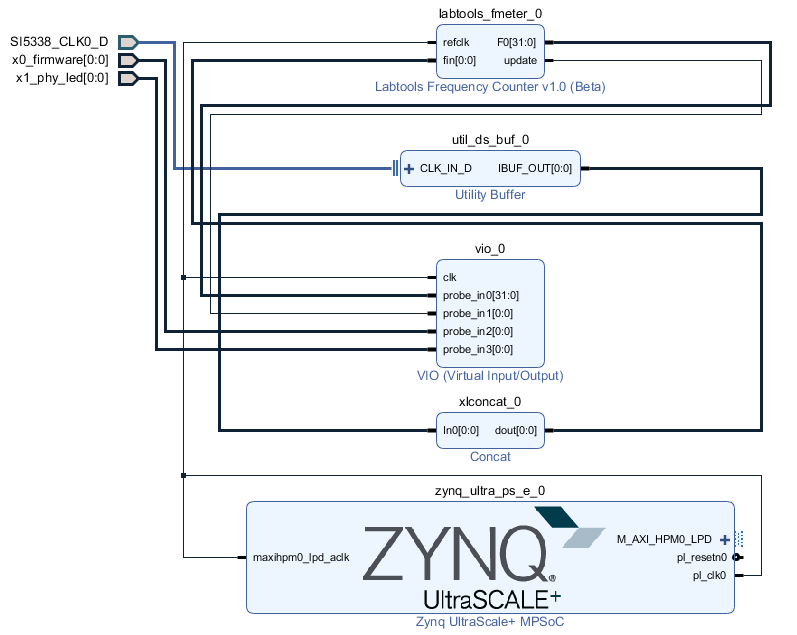

System Design - Vivado

| HTML |

|---|

<!-- Description of Block Design, Constrains... BD Pictures from Export... --> |

Block Design

PCB REV03

PCB REV01 REV02

PS Interfaces

Activated interfaces:

...

| Code Block | ||||

|---|---|---|---|---|

| ||||

set_property PACKAGE_PIN K9 [get_ports {SI5338_CLK0_D_clk_p[0]}]

set_property IOSTANDARD LVDS [get_ports {SI5338_CLK0_D_clk_p[0]}]

set_property DIFF_TERM TRUE [get_ports {SI5338_CLK0_D_clk_p[0]}]

set_property PACKAGE_PIN H1 [get_ports {x0_firmware[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {x0_firmware[0]}]

set_property PACKAGE_PIN J1 [get_ports {x1_phy_led[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {x1_phy_led[0]}] |

Software Design - SDK/HSI

...

Application

zynqmp_fsbl

TE modified 20172018.4 2 FSBL

Changes:

- Si5338 Configuration, ETH+OTG Reset over GPIO

- see xfsbl_board.c, xfsbl_board.h, xfsbl_main.c

- Add register_map.h, si5338.c, si5338.h

Note: Remove compiler flags "-Os -flto -ffat-lto-objects" if you create 2018.2 FSBL with SDK

zynqmp_fsbl_flash

TE modified 2017.4 FSBL

...

- Set FSBL Boot Mode to JTAG

- Disable Memory initialisation

- see xfsbl_initialisation.c, xfsbl_hw.h, xfsbl_handoff.c, xfsbl_main.c

Note: Remove compiler flags "-Os -flto -ffat-lto-objects" if you create 2018.2 FSBL with SDK

zynqmp_pmufw

Xilinx default PMU firmware.

...

Config

...

Activate:

- SUBSYSTEM_PRIMARY_SD_PSU_SD_1_SELECT

U-Boot

- Change platform-top.h

| Code Block | ||

|---|---|---|

| ||

#include <configs/platform-auto.h>

#define CONFIG_SYS_BOOTM_LEN 0xF000000

#define DFU_ALT_INFO_RAM \

"dfu_ram_info=" \

"setenv dfu_alt_info " \

"image.ub ram $netstart 0x1e00000\0" \

"dfu_ram=run dfu_ram_info && dfu 0 ram 0\0" \

"thor_ram=run dfu_ram_info && thordown 0 ram 0\0"

#define DFU_ALT_INFO_MMC \

"dfu_mmc_info=" \

DFU_ALT_INFO_RAM

/*Required for uartless designs */

#ifndef CONFIG_BAUDRATE

#define CONFIG_BAUDRATE 115200

#ifdef CONFIG_DEBUG_UART

#undef CONFIG_ "set dfu_alt_info " \

"${kernel_image} fat 0 1\\\\;" \

"dfu_mmc=run dfu_mmc_info && dfu 0 mmc 0\0" \

"thor_mmc=run dfu_mmc_info && thordown 0 mmc 0\0"

/*Required for uartless designs */

#ifndef CONFIG_BAUDRATE

#define CONFIG_BAUDRATE 115200

#ifdef CONFIG_DEBUG_UART

#undef CONFIG_DEBUG_UART

#endif

#endif

/*select sd instead of mmc for autoboot */

#define CONFIG_BOOTCOMMAND "run uenvboot; mmcinfo && fatload mmc 1 ${netstart} ${kernel_img};bootm ${netstart}"

Define CONFIG_ZYNQMP_EEPROM here and its necessaries in u-boot menuconfig if you had EEPROM memory. */

#ifdef CONFIG_ZYNQMP_EEPROM

#define CONFIG_SYS_I2C_EEPROM_ADDR_LEN 1

#define CONFIG_CMD_EEPROM

#define CONFIG_ZYNQ_EEPROM_BUS 5

#define CONFIG_ZYNQ_GEM_EEPROM_ADDR 0x54

#define CONFIG_ZYNQ_GEM_I2C_MAC_OFFSET 0x20

#endif

|

Device Tree

| Code Block | ||

|---|---|---|

| ||

/include/ "system-conf.dtsi"

/ {

};

/* SDIO */

&sdhci1 {

disable-wp;

no-1-8-v;

};

/* ETH PHY */

&gem3 {

status = "okay";

ethernet_phy0: ethernet-phy@0 {

compatible = "marvell,88e1510";

device_type = "ethernet-phy";

reg = <1>;

};

};

/* USB 2.0 */

&dwc3_0 {

status = "okay";

dr_mode = "host";

maximum-speed = "high-speed";

/delete-property/phy-names;

/delete-property/phys;

/delete-property/snps,usb3_lpm_capable;

};

/* QSPI PHY */

&qspi {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

flash0: flash@0 {

compatible = "jedec,spi-nor";

reg = <0x0>;

#address-cells = <1>;

#size-cells = <1>;

};

};

/* DMA not used: Reduce error messages on linux.*/

&lpd_dma_chan1 {

status = "disabled";

};

&lpd_dma_chan2 {

status = "disabled";

};

&lpd_dma_chan3 {

status = "disabled";

};

&lpd_dma_chan4 {

status = "disabled";

};

&lpd_dma_chan5 {

status = "disabled";

};

&lpd_dma_chan6 {

status = "disabled";

};

&lpd_dma_chan7 {

status = "disabled";

};

&lpd_dma_chan8 {

status = "disabled";

};

|

...

| Date | Document Revision | Authors | Description | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|

| ||||||||||||||||||||||

| v.34 | John Hartfiel |

| |||||||||||||||||||||||

| v.29 | John Hartfiel |

| |||||||||||||||||||||||

| 2018-02-06 | v.27 | John Hartfiel |

| ||||||||||||||||||||||

| 2018-01-29 | v.26 | John Hartfiel |

| ||||||||||||||||||||||

| 2018-01-24 | v.25 | John Hartfiel |

| ||||||||||||||||||||||

| 2018-01-10 | v.24 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-12-20 | v.23 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-11-21 | v.19 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-11-20 | v.18 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-11-13 | v.16 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-11-06 | v.15 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-23 | v.13 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-10-19 | v.9 | John Hartfiel |

| ||||||||||||||||||||||

| 2017-09-11 | v.1 |

| Initial release | ||||||||||||||||||||||

| All |

|

...

Overview

Content Tools