Page History

...

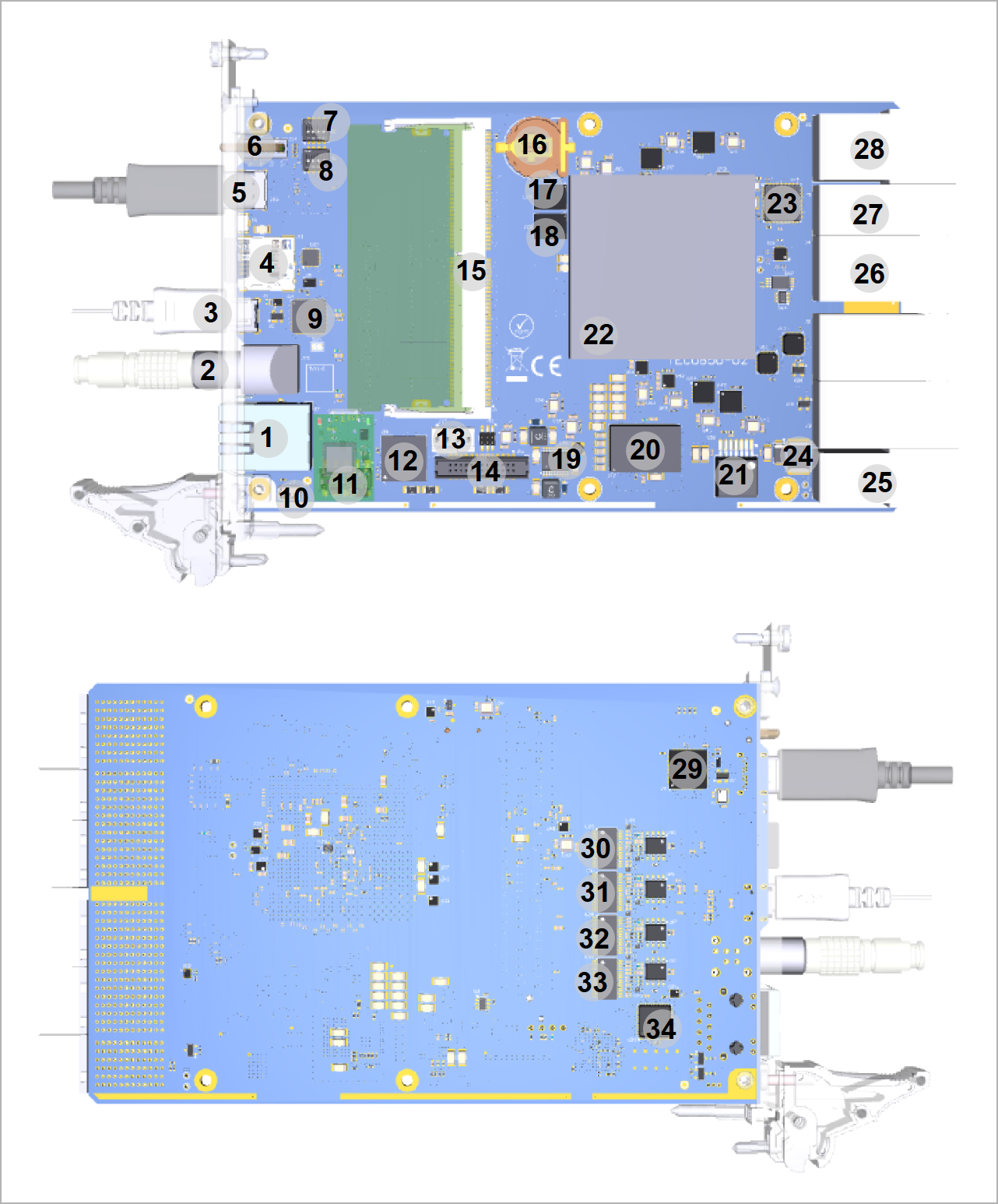

Zynq UltraScale+ MPSoC ZU15

- Front side interface connectors

- RJ-45 GbE Ethernet interface

- Elbow Socket with 4x on-board 8bit DAC output

- MicroSD Card connector

- USB2 and USB3 to FIFO bridge connector

- 4x status LEDs

- 3 4 CompactPCI slots for backplane connection (3U form factor)

- 24 GTH lanes

- 4 PS GTR lanes

- USB2 interface

- 64 Zynq FPGA PL HP I/O's

- 8x PLL clock input

- JTAG, I²C and 7 user I/O's to SC MAX10 FPGA

64bit DDR4 SODIMM (PS connected), 8 GByte maximum

Dual parallel QSPI Flash (bootable), 512 MByte maximum

- 26-pin header with 20 Zynq FPGA PL HD I/O's

- 3-pin header with 2 SC MAX10 FPGA I/O's

- System Controller (Altera MAX10 FPGA SoC)

- Power Sequencing

- System management and control for MPSoC and on-board peripherals

- Si5345 programmable 10 output PLL clock generator

- Quad and Dual PLL clock generators

- 2x 4bit DIP switches

- 1x user push button

- Zynq MPSoC cooling FAN connector

- On-board high-efficiency DC-DC converters

...

| Scroll Title | ||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ||||||||||||||||||||||||||||||||

|

- ...

- ...

- ...

Initial Delivery State

...

Overview

Content Tools