...

| Scroll Title |

|---|

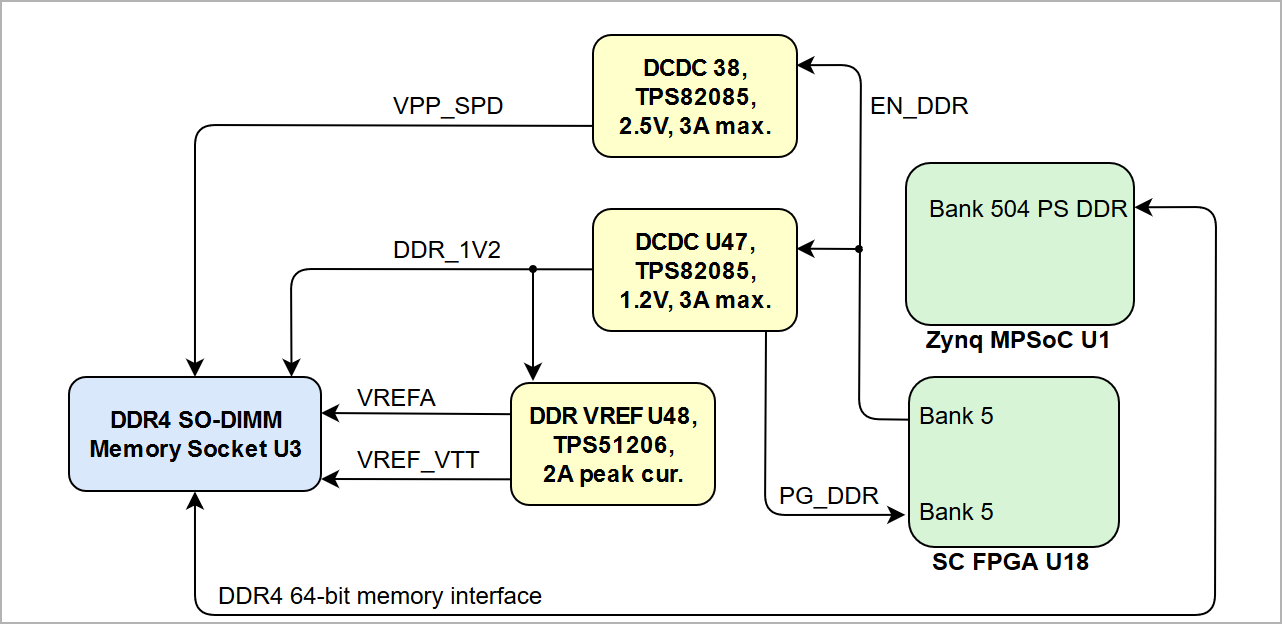

| anchor | Figure_38 |

|---|

| title | Figure 3: JTAG/UART Interface8: DDR4 SDRAM SODIMM socket |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 1 |

|---|

| diagramName | TEC0850 DDR4 interface |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

Following table gives an overview about the memory interface I/O signals of the DDR4 SDRAM SO-DIMM Socket U3:

| Scroll Title |

|---|

| anchor | Table_x12 |

|---|

| title | Table x12: DDR4 SDRAM SO-DIMM Socket socket U3 |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| DDR4 SDRAM I/O Signal | Signal Schematic Name | Connected to | Notes |

|---|

| Address inputs | | PS DDR Bank 504 | - | Bank address inputs

| | - | | Bank group inputs | | - | | Differential clocks | - DDR4-CLK0_P

- DDR4-CLK0_N

- DDR4-CLK1_P

- DDR4-CLK1_N

| 2 x DDR4 clock | | Data input/output | | - | | Check bit input/output | | - | | Data strobe (differential) | - DDR4-DQS0_P

- DDR4-DQS0_N

- ...

- DDR4-DQS8_P

- DDR4-DQS8_N

| - | | Data mask and data bus inversion | | - | | Serial address inputs | | address range configuration on I²C bus | | Control Signals | | chip selest signal | | On-die termination enable | | nRESET | | Command and address parity input | | Clock enable | | CRC error flag | | Activation command input | | Temperature event | | I²C | | not connected | - |

|

...

| Scroll Title |

|---|

| anchor | Figure_119 |

|---|

| title | Figure 11: CAN interface9: 4x 8bit DAC units |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 3 |

|---|

| diagramName | TEC0850 DACs |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

|

...

| Scroll Title |

|---|

| anchor | Figure_1110 |

|---|

| title | Figure 11: CAN interface10: Zynq MPSoC PL I/O's IDC pin-header |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 2 |

|---|

| diagramName | TEC0850 header J16 |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 346 |

|---|

|

|

|

...

| Scroll Title |

|---|

| anchor | Figure_11 |

|---|

| title | Figure 11: CAN interface10-pin JTAG/UART header |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 3 |

|---|

| diagramName | TEC0850 header 13 |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

|

...

2 I/O's of the SC FPGA U18 are exposed to the on-board 3-Pin PicoBlade header J8 available to the user or for future use of upcoming versions of SC FPGA firmware.

| Scroll Title |

|---|

| anchor | Figure_1112 |

|---|

| title | Figure 11: CAN interface12: 3-pin PicoBlade header |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 3 |

|---|

| diagramName | TEC0850 header J8 |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

|

...

| Scroll Title |

|---|

| anchor | Figure_1113 |

|---|

| title | Figure 11: CAN interface13: Backup-Battery Holder |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 4 |

|---|

| diagramName | TEC0850 battery holder |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

|

...

| Scroll Title |

|---|

| anchor | Figure_1314 |

|---|

| title | Figure 1314: 4-wire PWM FAN connectors |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 2 |

|---|

| diagramName | TEC0850 4-Wire PWM Connector |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

|

|

...