...

Zynq UltraScale+ MPSoC ZU15

- Front side interface connectors

- RJ-45 GbE Ethernet interface

- Elbow Socket with 4x on-board 8bit DAC output

- MicroSD Card connector

- USB2 and USB3 to FIFO bridge connector

- 4x status LEDs

- 4 CompactPCI slots connectors for backplane connection (3U form factor)

- 24 GTH lanes

- 4 PS GTR lanes

- USB2 interface

- 64 Zynq PL HP I/O's

- 8x PLL clock input

- JTAG, I²C and 7 user I/O's to MAX10 FPGA

64bit DDR4 SODIMM (PS connected), 8 GByte maximum

Dual parallel QSPI Flash (bootable), 512 MByte maximum

- 26-pin header with 20 Zynq PL HD I/O's

- 3-pin header with 2 MAX10 FPGA I/O's

- System Controller (Altera MAX10 FPGA SoC)

- Power Sequencing

- System management and control for MPSoC and on-board peripherals

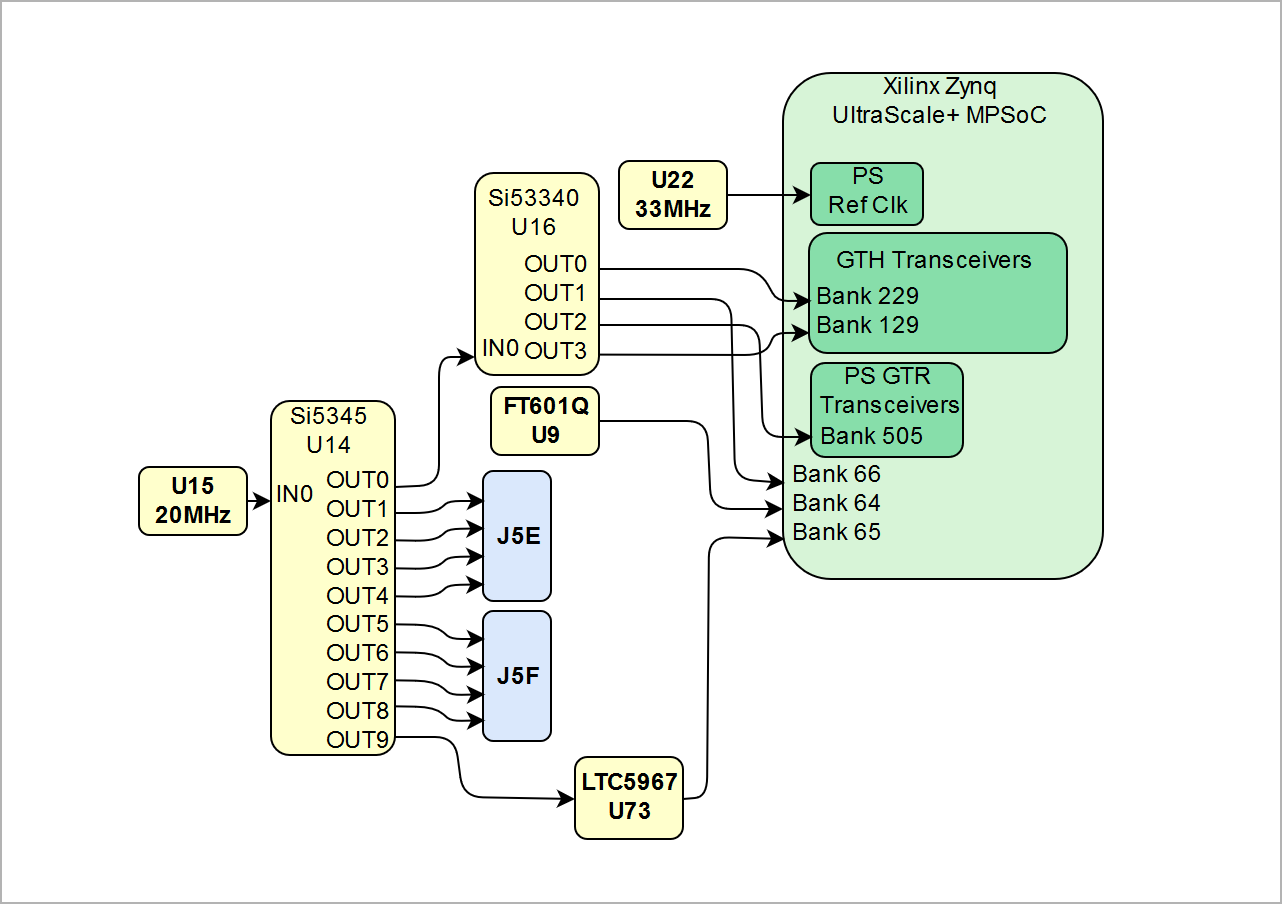

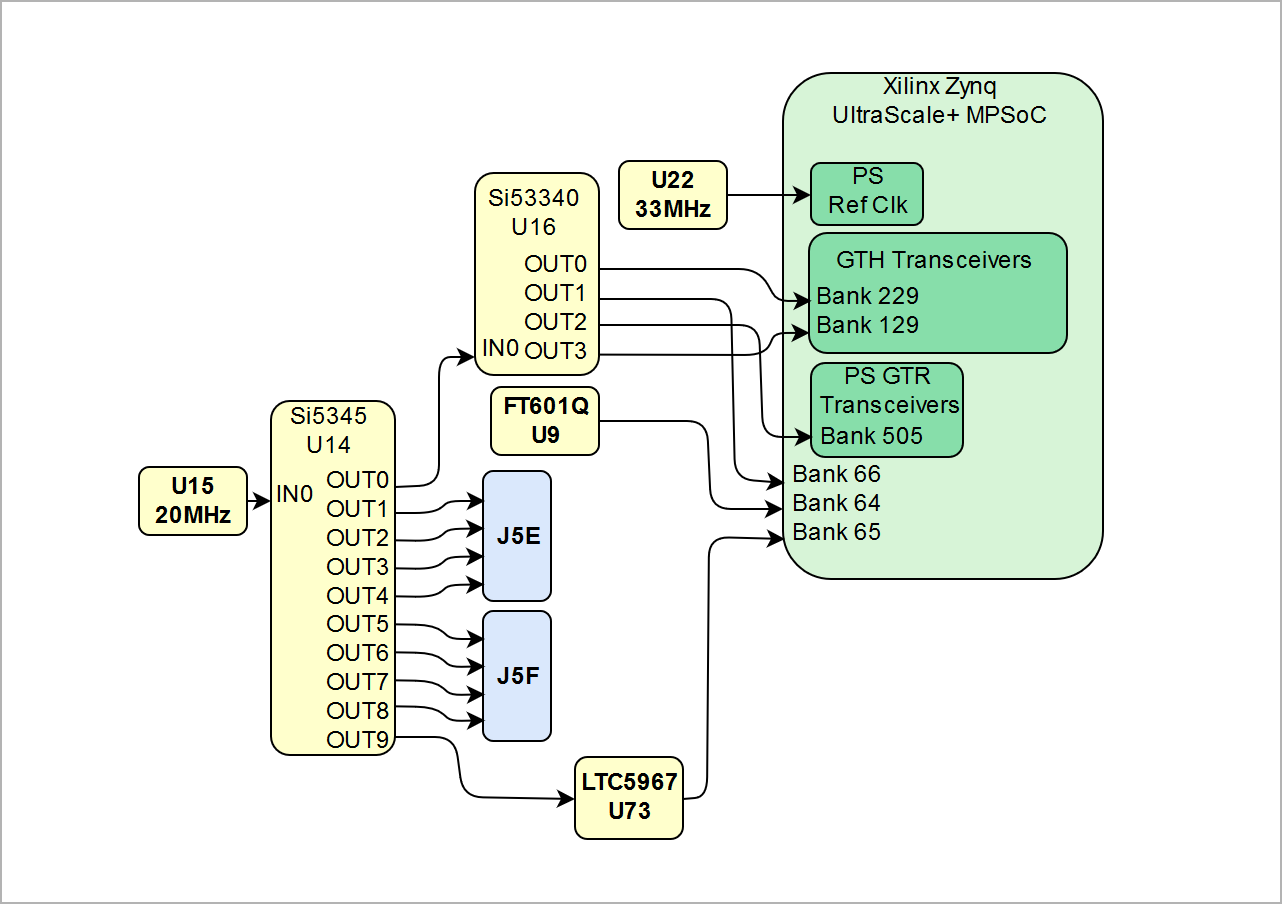

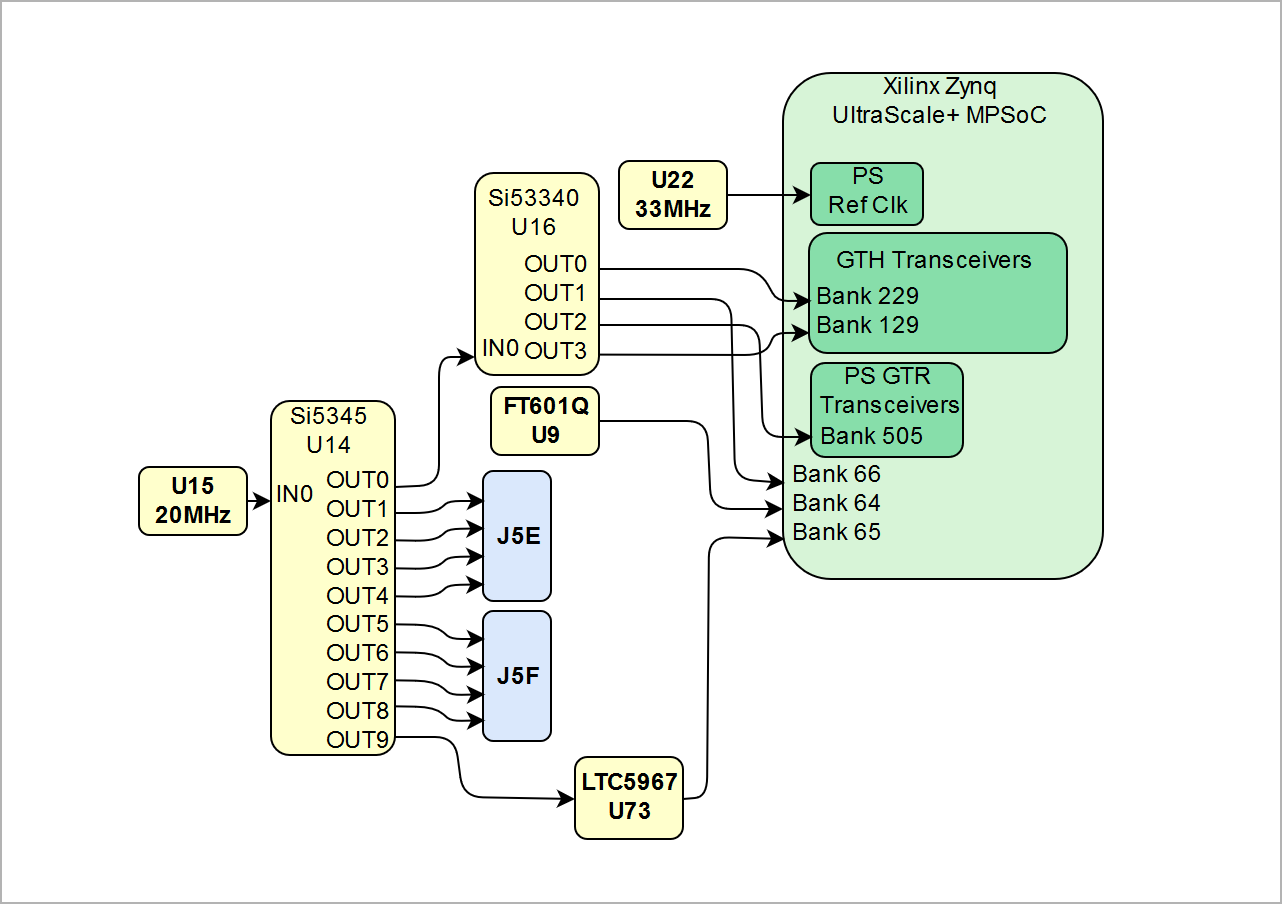

- Si5345 programmable 10 output PLL clock generator

- Si53340 Quad PLL clock generator

- 2x 4bit DIP switches

- 1x user push button

- Zynq MPSoC cooling FAN connector

- On-board high-efficiency DC-DC converters

...

- GbE RJ-45 MagJack, J7

- DAC output 5-pin elbow receptacle socket, J15

- Micro USB2 B receptacle connector, J9

- MicroSD Card socket, J11

- USB C connector, J10

- LED light pipes J14 integrating LEDs D1 ... D4

- 4bit DIP-switch, S2

- 4bit DIP-switch, S1

- FTDI FT2232 USB2 to FIFO bridge, U4

- 3-pin header, J8

- MAX10 FPGA JTAG/UART 10-pin header, J13

- Altera MAX10 System Controller FPGA, U18

- 4-Wire PWM fan connector, J17

- Zynq MPSoC PL I/O 26-pin header, J16

- DDR4 SO-DIMM 260-pin socket, U3

- Battery Holder CR1220, B1

- 256 Mbit (32 MByte) Micron Serial NOR Flash Memory N25Q256A, U24

- 256 Mbit (32 MByte) Micron Serial NOR Flash Memory N25Q256A, U25

- DC-DC Converter LT8471IFE @+5VA/-5VA, U74

- DC-DC Converter EM2130L02QI @VCCINT_0V85, U17

- DC-DC Converter 171050601 @5V, U50

- Xilinx Zynq Ultrascale+ MPSoC, U1

- Si5345A 10-output I²C programmable PLL clock, U14

- Main power fuse @2.5A/16V, F1

- cPCI slotconnector, J1

- cPCI slotconnector, J4

- cPCI slotconnector, J5

- cPCI slotconnector, J6

- FTDI FT601Q USB3 to FIFO bridge, U9

- TI THS5641 8bit DAC ,U28

- TI THS5641 8bit DAC ,U31

- TI THS5641 8bit DAC ,U29

- TI THS5641 8bit DAC ,U33

- Marvell Alaska 88E1512 GbE PHY ,U20

...

Following tables contains information about the interfaces, I/O's, clock and VCCIO sources available on the FMC connectors A - FcPCI connectors:

- CompactPCI Connector J1

- CompactPCI Connector J4

- CompactPCI Connector J5

- CompactPCI Connector J6

...

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: FTDI Signals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

cPCI connector J1 clock signal from PLL U14 is also shared with SC FPGA and header J13 : | Clock Signal Schematic Name | cPCI Connector Pin | Header J13 Pin | SC FPGA U18 Pin | Notes |

|---|

| J1-K3

J1-J3 | J13-5

J13-1 | Bank 1B, Pin G1

Bank 1B, Pin G2 | Supplied by 10-output PLL clock PLL U14 |

|

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: FTDI Signals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

cPCI connector J1 VCC/VCCIO: | cPCI Connector | Available VCC/VCCIO | cPCI Connector Pin | Source | Notes |

|---|

J1 | VIN_12V | J1-A1

J1-D1

J1-E1

J1-G1

J1-H1

J1-J1

J1-K1 | cPCI backplane

| min. cur.: 6.65A |

|

...

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: FTDI Signals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

cPCI connector J1 MGT Lanes: | cPCI Connector | MGT Lane | Bank | Type | Signal Schematic Name | FMC Connector PincPCI Connector Pin | FPGA Pin |

|---|

J4

| 0 | 128 | GTH | - PE3_RX0_P

- PE3_RX0_N

- PE3_TX0_P

- PE3_TX0_N

| J4-D1

J4-E1

J4-A1

J4-B1 | MGTHRXP0_128, T33

MGTHRXN0_128, T34

MGTHTXP0_128, T29

MGTHTXN0_128, T30 | | 1 | 128 | GTH | - PE3_RX1_P

- PE3_RX1_N

- PE3_TX1_P

- PE3_TX1_N

| J4-J1

J4-K1

J4-G1

J4-H1 | MGTHRXP1_128, P33

MGTHRXN1_128, P34

MGTHTXP1_128, R31

MGTHTXN1_128, R32 | | 2 | 128 | GTH | - PE3_RX2_P

- PE3_RX2_N

- PE3_TX2_P

- PE3_TX2_N

| J4-E2

J4-F2

J4-B2

J4-C2 | MGTHRXP2_128, N31

MGTHRXN2_128, N32

MGTHTXP2_128, P29

MGTHTXN2_128, P30 | | 3 | 128 | GTH | - PE3_RX3_P

- PE3_RX3_N

- PE3_TX3_P

- PE3_TX3_N

| J4-K2

J4-L2

J4-H2

J4-I2 | MGTHRXP3_128, M33

MGTHRXN3_128, M34

MGTHTXP3_128, M29

MGTHTXN3_128, M30 | | 0 | 129 | GTH | - PE4_RX0_P

- PE4_RX0_N

- PE4_TX0_P

- PE4_TX0_N

| J4-D3

J4-E3

J4-A3

J4-B3 | MGTHRXP0_129, L31

MGTHRXN0_129, L32

MGTHTXP0_129, K29

MGTHTXN0_129, K30 | | 1 | 129 | GTH | - PE4_RX1_P

- PE4_RX1_N

- PE4_TX1_P

- PE4_TX1_N

| J4-J3

J4-K3

J4-G3

J4-H3 | MGTHRXP1_129, K33

MGTHRXN1_129, K34

MGTHTXP1_129, J31

MGTHTXN1_129, J32 | | 2 | 129 | GTH | - PE4_RX2_P

- PE4_RX2_N

- PE4_TX2_P

- PE4_TX2_N

| J4-E4

J4-F4

J4-B4

J4-C4 | MGTHRXP2_129, H33

MGTHRXN2_129, H34

MGTHTXP2_129, H29

MGTHTXN2_129, H30 | | 3 | 129 | GTH | - PE4_RX3_P

- PE4_RX3_N

- PE4_TX3_P

- PE4_TX3_N

| J4-K4

J4-L4

J4-H4

J4-I4 | MGTHRXP3_129, F33

MGTHRXN3_129, F34

MGTHTXP3_129, G31

MGTHTXN3_129, G32 | | 0 | 130 | GTH | - PE5_RX0_P

- PE5_RX0_N

- PE5_TX0_P

- PE5_TX0_N

| J4-D5

J4-E5

J4-A5

J4-B5 | MGTHRXP3_130, B33

MGTHRXN3_130, B34

MGTHTXP3_130, A31

MGTHTXN3_130, A32 | | 1 | 130 | GTH | - PE5_RX1_P

- PE5_RX1_N

- PE5_TX1_P

- PE5_TX1_N

| J4-J5

J4-K5

J4-G5

J4-H5 | MGTHRXP2_130, C31

MGTHRXN2_130, C32

MGTHTXP2_130, B29

MGTHTXN2_130, B30 | | 2 | 130 | GTH | - PE5_RX2_P

- PE5_RX2_N

- PE5_TX2_P

- PE5_TX2_N

| J4-E6

J4-F6

J4-B6

J4-C6 | MGTHRXP1_130, D33

MGTHRXN1_130, D34

MGTHTXP1_130, D29

MGTHTXN1_130, D30 | | 3 | 130 | GTH | - PE5_RX3_P

- PE5_RX3_N

- PE5_TX3_P

- PE5_TX3_N

| J4-K6

J4-L6

J4-H6

J4-I6 | MGTHRXP0_130, E31

MGTHRXN0_130, E32

MGTHTXP0_130, F29

MGTHTXN0_130, F30 | | 0 | 230 | GTH | - PE6_RX0_P

- PE6_RX0_N

- PE6_TX0_P

- PE6_TX0_N

| J4-D7

J4-E7

J4-A7

J4-B7 | MGTHRXP3_230, A4

MGTHRXN3_230, A3

MGTHTXP3_230, A8

MGTHTXN3_230, A7 | | 1 | 230 | GTH | - PE6_RX1_P

- PE6_RX1_N

- PE6_TX1_P

- PE6_TX1_N

| J4-J7

J4-K7

J4-G7

J4-H7 | MGTHRXP2_230, B2

MGTHRXN2_230, B1

MGTHTXP2_230, B6

MGTHTXN2_230, B5 | | 2 | 230 | GTH | - PE6_RX2_P

- PE6_RX2_N

- PE6_TX2_P

- PE6_TX2_N

| J4-E8

J4-F8

J4-B8

J4-C8 | MGTHRXP1_230, C4

MGTHRXN1_230, C3

MGTHTXP1_230, D6

MGTHTXN1_230, D5 | | 3 | 230 | GTH | - PE6_RX3_P

- PE6_RX3_N

- PE6_TX3_P

- PE6_TX3_N

| J4-K8

J4-L8

J4-H8

J4-I8 | MGTHRXP0_230, D2

MGTHRXN0_230, D1

MGTHTXP0_230, E4

MGTHTXN0_230, E3 |

|

...

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: FTDI Signals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| cPCI Connector | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|

| J5 | MGT | - | 16 (8 x RX/TX) | Bank 128 GTH

Bank 128 GTH | - | - | | Clock Input | - | 8 | PLL clock U14 | - | - |

|

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: FTDI Signals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

cPCI connector J1J5 MGT Lanes: |

USB-C

Front panel USB-C Interface connected to USB FIFO bridge chip FT601Q. 32-bit FIFO bridge provides a simple high-speed interface to Zynq UltraScale+ PL.

...

| anchor | Table_x |

|---|

| title | Table x: FTDI Signals |

|---|

...

See FT600Q-FT601Q IC Datasheet for interface details.

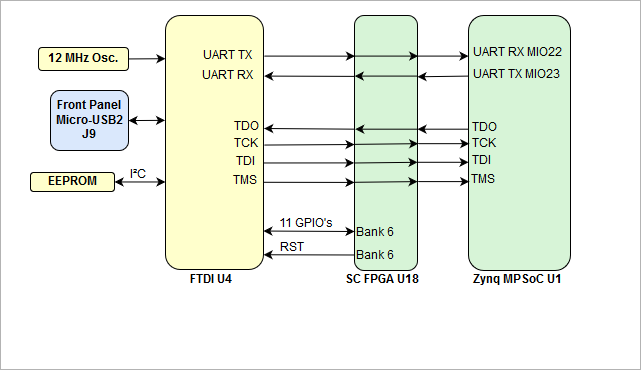

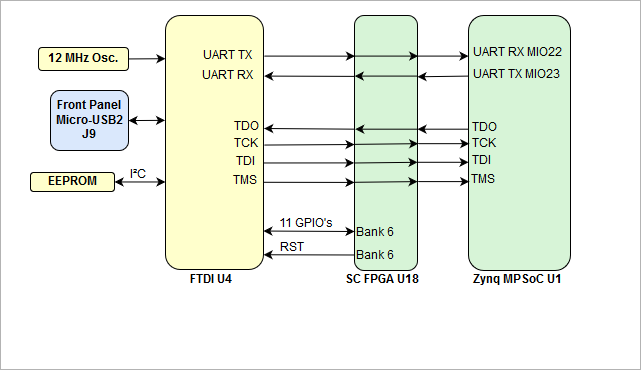

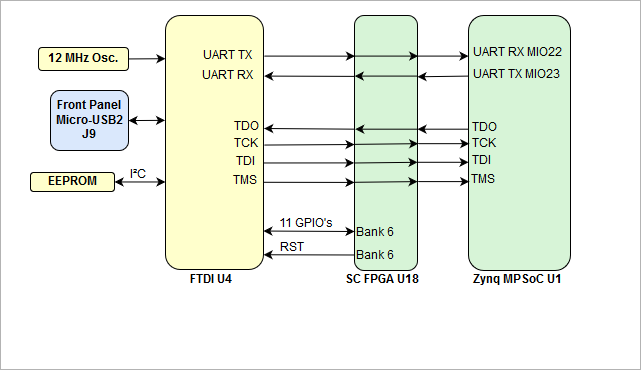

MicroUSB

Front panel Micro-USB Interface provides access to UART and JTAG functions via FTDI FT2232 chip. Use of this feature requires that USB driver is installed on your host PC. UART0 with MIO 22 .. 23 should be selected in "Zynq UltraScale+ MPSoC" configuration.

The Digilent plug-in software and cable drivers must be installed on your machine for you to be able to use JTAG interface.

...

| anchor | Figure_3 |

|---|

| title | Figure 3: JTAG/UART Interface |

|---|

...

| Scroll Only |

|---|

Image Removed Image Removed

|

SD

There are some limitations to use SD card Interface in Linux.

- Zynq UltraScale+ SD controller is working only in the 3.3V mode as it connected to SD card socket using 1.8V to 3.3V level shifter U10.

- Micro SD card socket has no "Write Protect" switch.

| Tip |

|---|

To force Linux driver not to use this features add following instructions to device tree file. &sdhci1 { no-1-8-v;

disable-wp;

}; |

RJ45 - Ethernet

cPCIe

...

MGT

The TEC0850 board has 30 MGT lines routed to backplane connectors.

...

| anchor | Table_x |

|---|

| title | Table x: MGT Banks |

|---|

...

MGT reference clocks are connected to banks 129, 229 and 505. Banks 128 and 130 should share clock from bank 129, banks 230 and 228 from bank 229.

USB Interface

Zynq UltraScale+ USB controller connected to backplane connector J1C via USB PHY chip U11.

DDR4 SODIMM Socket

The Zynq UltraScale+ DDRC hard memory controller is wired to the DDR4 SODIMM Socket U3.

Circular Push Pull Connector

PicoBlade Connector

Pin Heater 2,54mm (2x5)

Battery holder

On-board Peripherals

| Page properties |

|---|

|

Notes : - add subsection for every component which is important for design, for example:

- Ethernet PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

Subsections...

Zynq UltraScale XCZU15EG MPSoC

The TEC0850 board is populated with the Zynq UltraScale+ XCZU15EG-1FFVB1156E MPSoC.

Main IO interfaces are shown on the image below.

PS MIO Configuration

...

| anchor | Table_x |

|---|

| title | Table x: Default MIO Configuration |

|---|

...

| cPCI Connector | MGT Lane | Bank | Type | Signal Schematic Name | cPCI Connector Pin | FPGA Pin |

|---|

| J5 | 0 | 228 | GTH | - PE8_RX0_P

- PE8_RX0_N

- PE8_TX0_P

- PE8_TX0_N

| J5-D3

J5-E3

J5-A3

J5-B3 | MGTHRXP0_228, T2

MGTHRXN0_228, T1

MGTHTXP0_228, R4

MGTHTXN0_228, R3 | | 1 | 228 | GTH | - PE8_RX1_P

- PE8_RX1_N

- PE8_TX1_P

- PE8_TX1_N

| J5-J3

J5-K3

J5-G3

J5-H3 | MGTHRXP1_228, P2

MGTHRXN1_228, P1

MGTHTXP1_228, P6

MGTHTXN1_228, P5 | | 2 | 228 | GTH | - PE8_RX2_P

- PE8_RX2_N

- PE8_TX2_P

- PE8_TX2_N

| J5-E4

J5-F4

J5-B4

J5-C4 | MGTHRXP2_228, M2

MGTHRXN2_228, M1

MGTHTXP2_228, N4

MGTHTXN2_228, N3 | | 3 | 228 | GTH | - PE8_RX3_P

- PE8_RX3_N

- PE8_TX3_P

- PE8_TX3_N

| J5-K4

J5-L4

J5-H4

J5-I4 | MGTHRXP3_228, L4

MGTHRXN3_228, L3

MGTHTXP3_228, M6

MGTHTXN3_228, M5 | | 0 | 229 | GTH | - PE7_RX0_P

- PE7_RX0_N

- PE7_TX0_P

- PE7_TX0_N

| J5-D1

J5-E1

J5-A1

J5-B1 | MGTHRXP0_229, K2

MGTHRXN0_229, K1

MGTHTXP0_229, K6

MGTHTXN0_229, K5 | | 1 | 229 | GTH | - PE7_RX1_P

- PE7_RX1_N

- PE7_TX1_P

- PE7_TX1_N

| J5-J1

J5-K1

J5-G1

J5-H1 | MGTHRXP1_229, J4

MGTHRXN1_229, J3

MGTHTXP1_229, H6

MGTHTXN1_229, H5 | | 2 | 229 | GTH | - PE7_RX2_P

- PE7_RX2_N

- PE7_TX2_P

- PE7_TX2_N

| J5-E2

J5-F2

J5-B2

J5-C2 | MGTHRXP2_229, H2

MGTHRXN2_229, H1

MGTHTXP2_229, G4

MGTHTXN2_229, G3 | | 3 | 229 | GTH | - PE7_RX3_P

- PE7_RX3_N

- PE7_TX3_P

- PE7_TX3_N

| J5-K2

J5-L2

J5-H2

J5-I2 | MGTHRXP3_229, F2

MGTHRXN3_229, F1

MGTHTXP3_229, F6

MGTHTXN3_229, F5 |

|

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: FTDI Signals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

cPCI connector J5 Clock Signals: | cPCI Connector | PLL Clock Output | Signal Schematic Name | cPCI Connector Pin | Notes |

|---|

| J5 | OUT1 | | J5-A5

J5-B5 | Supplied by on-board

10-output PLL clock generator U14 | | OUT2 | | J5-D5

J5-E5 | | OUT3 | | J5-G5

J5-H5 | | OUT4 | | J5-J5

J5-K5 | | OUT5 | | J5-B6

J5-C6 | | OUT6 | | J5-E6

J5-F6 | | OUT7 | | J5-H6

J5-I6 | | OUT8 | | J5-K6

J5-L6 |

|

| Anchor |

|---|

| CompactPCI Connector J6 |

|---|

| CompactPCI Connector J6 |

|---|

|

CompactPCI Connector J6

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: FTDI Signals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

cPCI connector J1 Interfaces: | cPCI Connector | Interfaces | I/O Signal Count | LVDS-pairs count | Connected to | VCCO bank Voltage | Notes |

|---|

J1 | I/O | 46 | 23 | PL bank 66 | PL_1.8V | - | | 18 | 9 | PL bank 65 | PL_1.8V | - | | 2 | - | SC FPGA U18 Bank 1B | +3V_D | Signalname: 'DET_RIO', 'DET_BPR' |

|

USB-C Connector

Front panel USB-C Interface is connected to USB FIFO bridge chip FT601Q. 32-bit FIFO bridge provides a simple high-speed interface to Zynq UltraScale+ PL.

| Scroll Title |

|---|

| anchor | Figure_2 |

|---|

| title | Figure 2: TEC0850-02 Overview IO interfaces |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | true |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramName | TEC0850 USB2 to FIFO |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| diagramWidth | 642 |

|---|

| revision | 1 |

|---|

|

|

|

MAX10 System Controller

System controller chip is Intel MAX10 10M08SAU169C8G Chip with board control firmware.

Programmable Clock Generators

...

| anchor | Figure_2 |

|---|

| title | Figure 2: TEF1001-02 main components |

|---|

...

| Scroll Only |

|---|

Image Removed Image Removed

|

I2C

The onboard I2C bus is connected to MIO 20...21 pins. Devices on the bus shown in the table below.

...

| anchor | Table_x |

|---|

| title | Table x: SI5345 I2C address |

|---|

...

Oscillators

FTDIs

FT2232H

FT601Q-B-T

Quad-SPI Flash Memory

Board has two N25Q512A11G1240E connected in a dual parallel mode.

EEPROMs

I2C

The onboard I2C bus is connected to MIO 20...21 pins. Devices on the bus shown in the table below.

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: EEPROMs I2C AddressesFTDI Signals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

| I2C address | Chip | Description |

|---|

| 0x50 | U63 24AA128T-I/ST | 128K Serial EEPROM |

| 0x53 | U64 24AA025E48T-I/OT | 2K Serial EEPROM with EUI-48™ or EUI-64™ Node Identity |

USB PHY

Gigabit Ethernet PHY

Board has Marvell Alaska 88E1512 Ethernet PHY which use MDIO address 1.

8Bit DACs

Board has 4 8-bit parallel Texas Instruments THS5641 DACs with up to 100 MSPS Update Rate.

DIP-Switches

S1

...

| anchor | Table_x |

|---|

| title | Table x: LEDs |

|---|

...

The USB3 to FIFO bridge U9 is connected to the Zynq MPSoC's PL bank 64 and is accessible through USB-C connector J10: | IC | Interface | Signal Schematic Names | Connected to | Notes |

|---|

FT601Q U9

| USB3 data lane | - SSRX_P

- SSRX_N

- SSTXX_P

- SSTXX_N

| USB C Connector J10 | - | | USB2 data lane | | USB C Connector J10 | - | | Control Lines | - FTDI_RESET_N

- WAKEUP_N

- SIWU_N

- TXE_N

- RXF_N

- WR_N

- RD_N

- OE_N

- BE_0

- BE_1

- BE_2

- BE_3

- FIFO_CLK

| PL bank 64

| - | | Parallel GPIO's | | PL bank 64 | - |

|

See FT600Q-FT601Q IC Datasheet for interface details.

Micro-USB2 Connector

Front panel Micro-USB2 Interface provides access to UART and JTAG functions via FTDI FT2232 chip. Use of this feature requires that USB driver is installed on your host PC. UART0 with MIO 22 .. 23 should be selected in "Zynq UltraScale+ MPSoC" configuration.

The Digilent plug-in software and cable drivers must be installed on your machine for you to be able to use JTAG interface.See Zynq UltraScale+ Device Technical Reference Manual page 236 for full boot modes description. Most common modes are

| Scroll Title |

|---|

| anchor | TableFigure_x3 |

|---|

| title | Table x: Recommended Boot ModesFigure 3: JTAG/UART Interface |

|---|

|

| tablelayoutorientation | portrait |

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

style | widths | | sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

cellHighlighting| Boot Mode | SW1:4 | SW1:3 | SW1:2 | SW1:1 |

|---|

| JTAG Boot Mode | ON | ON | ON | ON |

| Quad-SPI | ON | ON | ON | OFF |

| SD Card | ON | ON | OFF | OFF |

...

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 8 |

|---|

| diagramName | uart_jtag |

|---|

| simpleViewer | true |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| diagramWidth | 642 |

|---|

|

|

| Scroll Only |

|---|

Image Added Image Added

|

|

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: S2 DIP SwitchFTDI Signals |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

| Switch | Description |

|---|

| 1 | SC JTAGEN |

| 2 | EEPROM WP (Write protect) |

| 3 | FPGA PUDC |

| 4 | SC Switch (Reserved for future use) |

Buttons

LEDs

...

| anchor | Table_x |

|---|

| title | Table x: LEDs |

|---|

...

The USB2 to FIFO bridge U4 is connected to the SC FPGA U18 and is accessible through Micro-USB2 connector J9: | IC | Interface | Signal Schematic Names | Connected to | Notes |

|---|

| FT2232H U4 | USB2 data lane | | Micro-USB2 connector J9 | - | | Control Lines | | SC FPGA U18, bank 6

| - | | Parallel GPIO's | - ADBUS0

- ADBUS1

- ADBUS2

- ADBUS3

- BDBUS0

- BDBUS1

- BDBUS2

- BDBUS3

- BDBUS4

- BDBUS5

- BDBUS6

- BDBUS7

- BCBUS0

- BCBUS1

- BCBUS2

- BCBUS3

- BCBUS4

| SC FPGA U18, bank 6 | - |

|

SD

The SD Card interface of the TEC0850 board is not directly wired to the connector J11 pins, but through a Texas Instruments TXS02612 SD IO Port Expander, which is needed for voltage translation due to different voltage levels of the Micro SD Card and MIO-bank of the Xilinx Zynq MPSoC. The Micro SD Card has 3.3V signal voltage level, but the PS MIO-bank on the Xilinx Zynq MPSoC has VCCIO of 1.8V.

| Scroll Title |

|---|

| anchor | Figure_3 |

|---|

| title | Figure 3: JTAG/UART Interface |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | true |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramName | TEC0850 SD IO |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| diagramWidth | 641 |

|---|

| revision | 2 |

|---|

|

|

|

There are some limitations to use SD card Interface in Linux.

- Zynq UltraScale+ SD controller is working only in the 3.3V mode as it connected to SD card socket using 1.8V to 3.3V level shifter U10.

- Micro SD card socket has no "Write Protect" switch.

| Tip |

|---|

To force Linux driver not to use this features add following instructions to device tree file. &sdhci1 { no-1-8-v;

disable-wp;

}; |

RJ45 - Ethernet

On-board Gigabit Ethernet PHY is provided with Marvell Alaska 88E1512 IC U20. The Ethernet PHY RGMII interface is connected to the Zynq MPSoC Ethernet interface of the PS MIO bank 501. I/O voltage is fixed at 1.8V for HSTL signaling. The reference clock input of the PHY is supplied from the on-board 25.000000 MHz oscillator U21. The LEDs of the RJ-45 MegJack J13 are connected to the GbE PHY U20 status LED output.

| Scroll Title |

|---|

| anchor | Figure_3 |

|---|

| title | Figure 3: JTAG/UART Interface |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | true |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramName | TEC0850 GbE |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| diagramWidth | 641 |

|---|

| revision | 1 |

|---|

|

|

|

DDR4 SODIMM Socket

On the TEC0850 board there is a DDR4 memory interface U3 with a 64-bit databus width available for SO-DIMM modules connected to the Zynq UltraScale+ DDRC hard memory controller.

| Scroll Title |

|---|

| anchor | Figure_3 |

|---|

| title | Figure 3: JTAG/UART Interface |

|---|

|

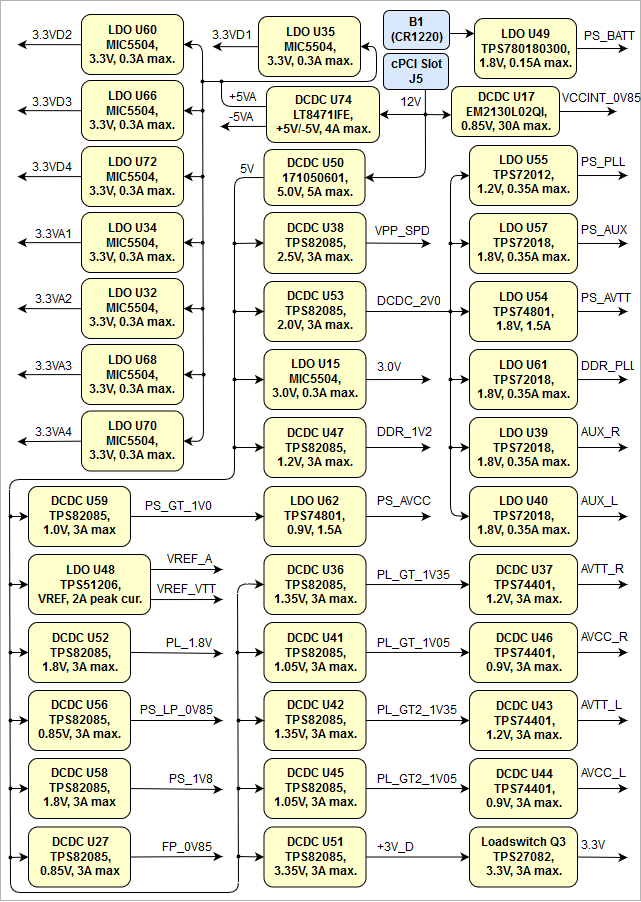

Power and Power-On Sequence

Power Consumption

The maximum power consumption of a module mainly depends on the design running on the FPGA.

Xilinx provide a power estimator excel sheets to calculate power consumption. It's also possible to evaluate the power consumption of the developed design with Vivado. See also Trenz Electronic Wiki FAQ.

...

| anchor | Table_x |

|---|

| title | Table x: Typical power consumption. |

|---|

...

Power supply with minimum current capability of 6.65A for system startup is recommended.

The TEC0850 board is equipped with the Xilinx Zynq UltraScale+ MPSoC delivers a heterogeneous multi-processing system with integrated programmable logic and independently operable elements and is designed to meet embedded system power management requirement by advanced power management features. This features allow to offset the power and heat constraints against overall performance and operational efficiency.

This features allowing highly flexible power management are achieved by establishing Power Domains for power isolation. The Zynq UltraScale+ MPSoC has multiple power domains, whereby each power domain requires its own particular on-board DC-DC converters.

The Processing System contains three Power Domains:

- Battery Power Domain (BBRAM and RTC)

- Full-Power Domain (Application Processing Unit, DDR Controller, Graphics Processing Unit and High-Speed Connectivity)

- Low-Power Domain (Real-Time Processing Unit, Security and Configuration Unit, Platform Management Unit, System Monitor and General Connectivity)

- Programmable Logic (PL)

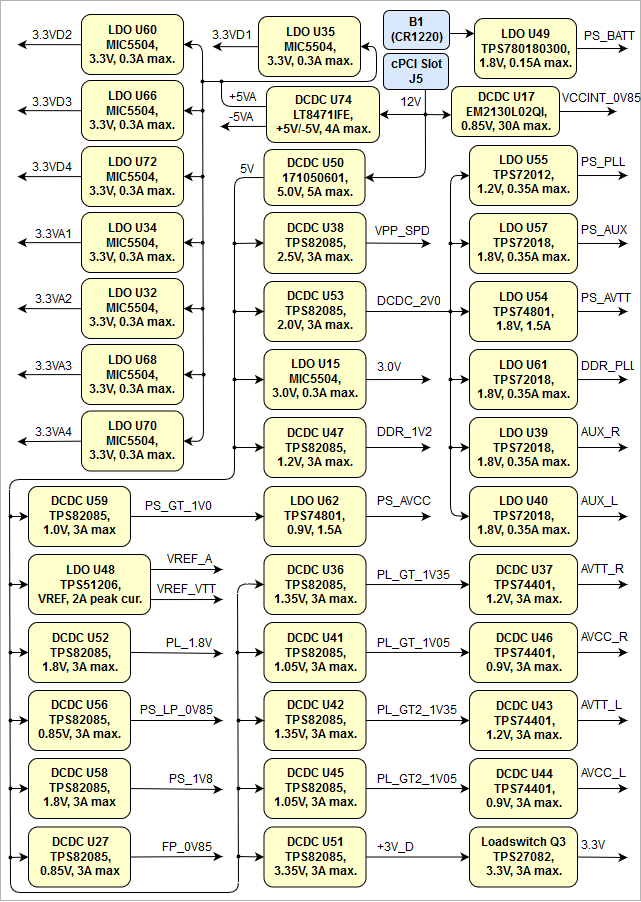

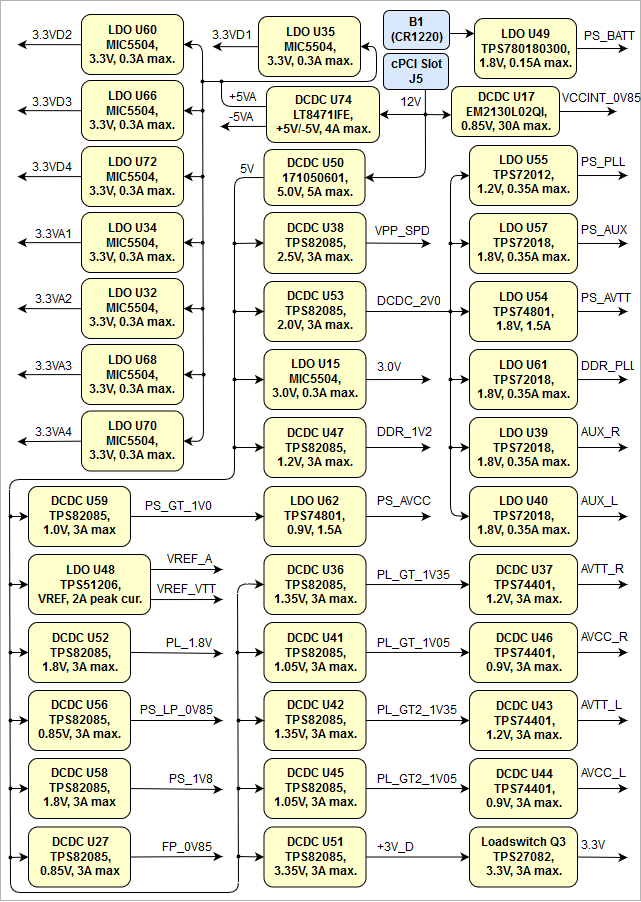

Power Distribution Dependencies

There are following dependencies how the initial 24V voltage from the main power pins on cPCI slot J1 is distributed to the on-board DC-DC converters, which power up further DC-DC converters and the particular on-board voltages:

| Scroll Title |

|---|

| anchor | Figure_3 |

|---|

| title | Figure 3: Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | falsetrue |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayNamediagramNamelbox | TEC0850 DDR4 interfacetrue |

|---|

| simpleViewerrevision | false16 |

|---|

| width | |

|---|

| diagramNamediagramWidth | Power supply641 |

|---|

| simpleViewerrevision | true1 | width |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

diagramWidth | 641

|

|

|

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: FTDI Signals |

|---|

|

| only |

Image Removed Image Removed

|

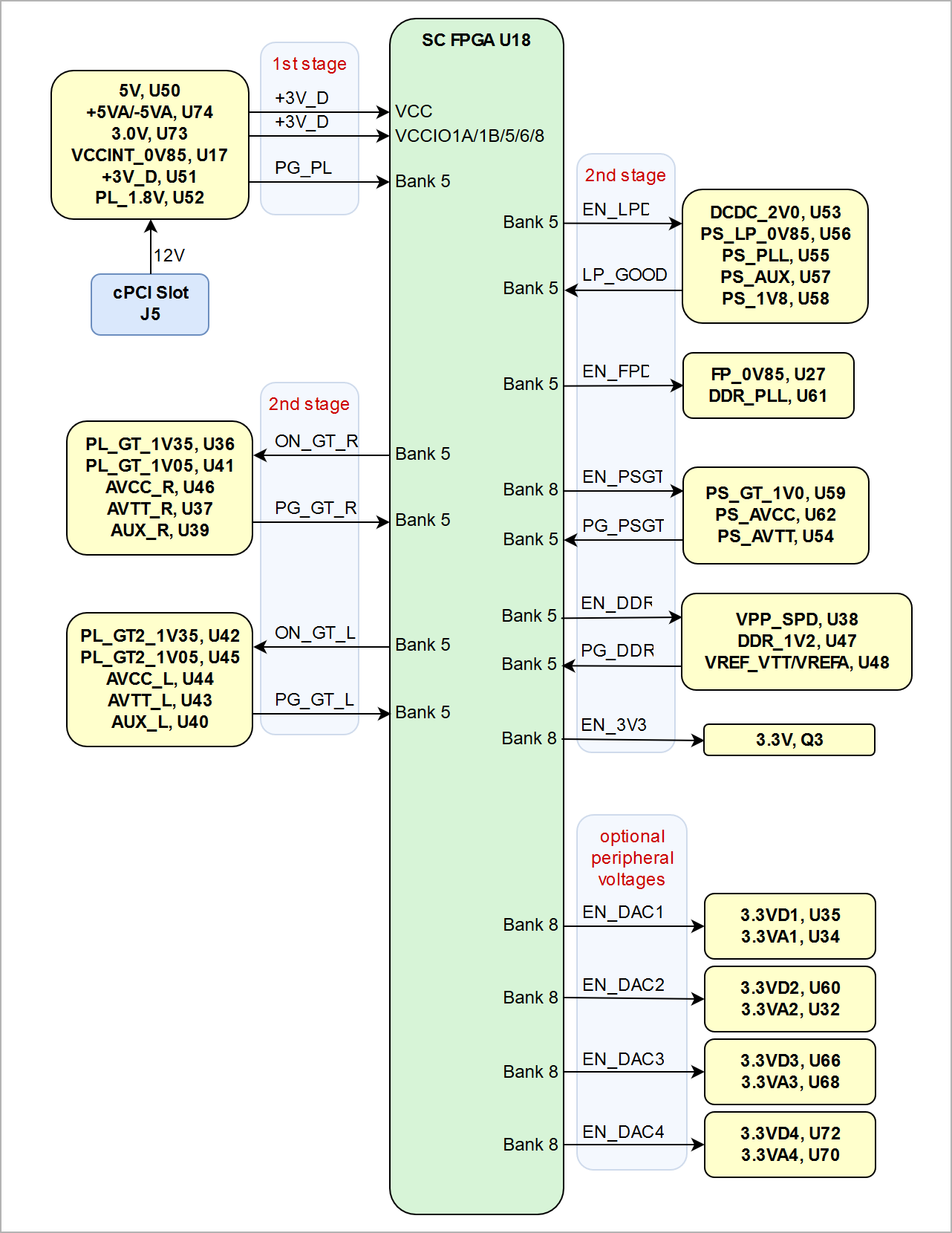

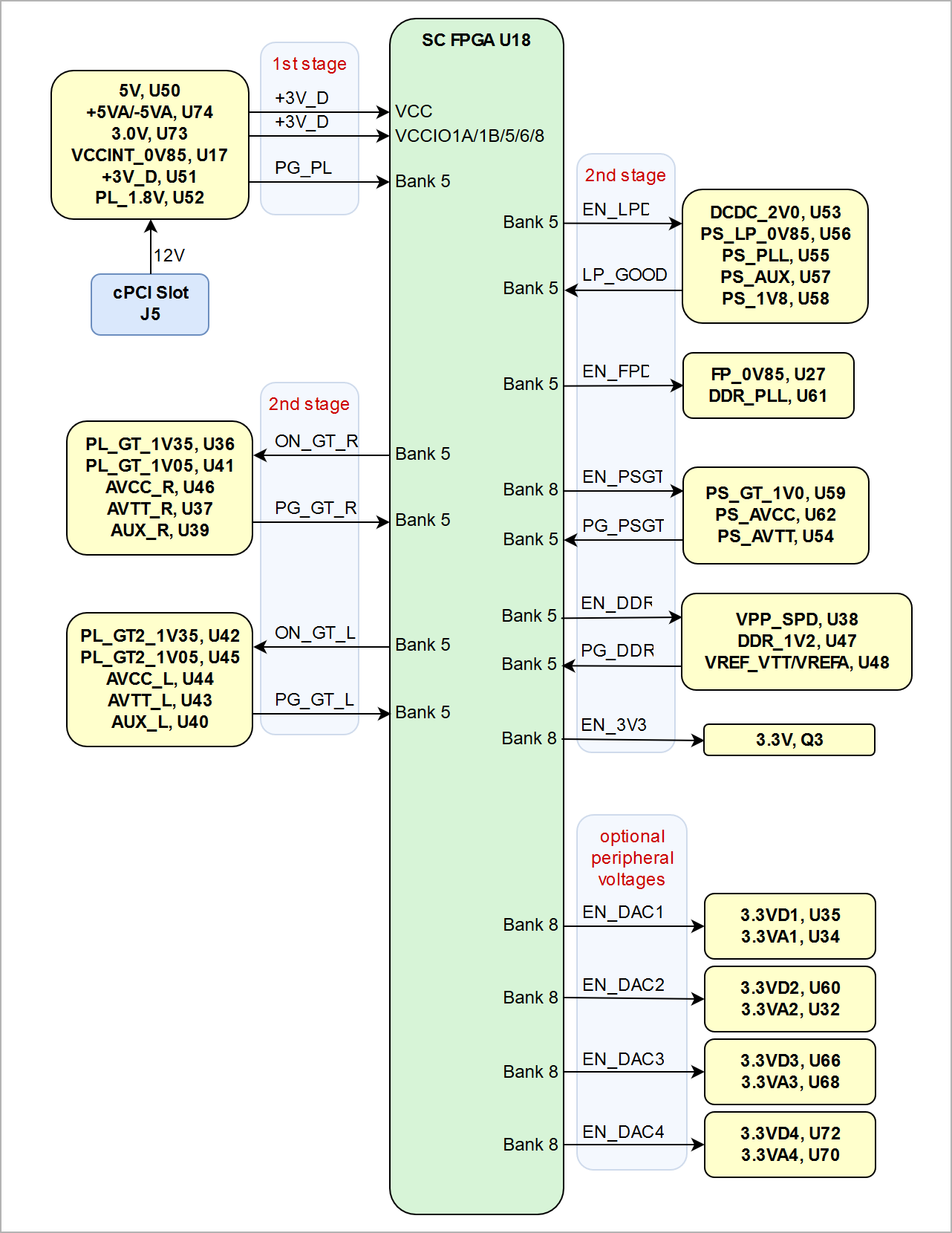

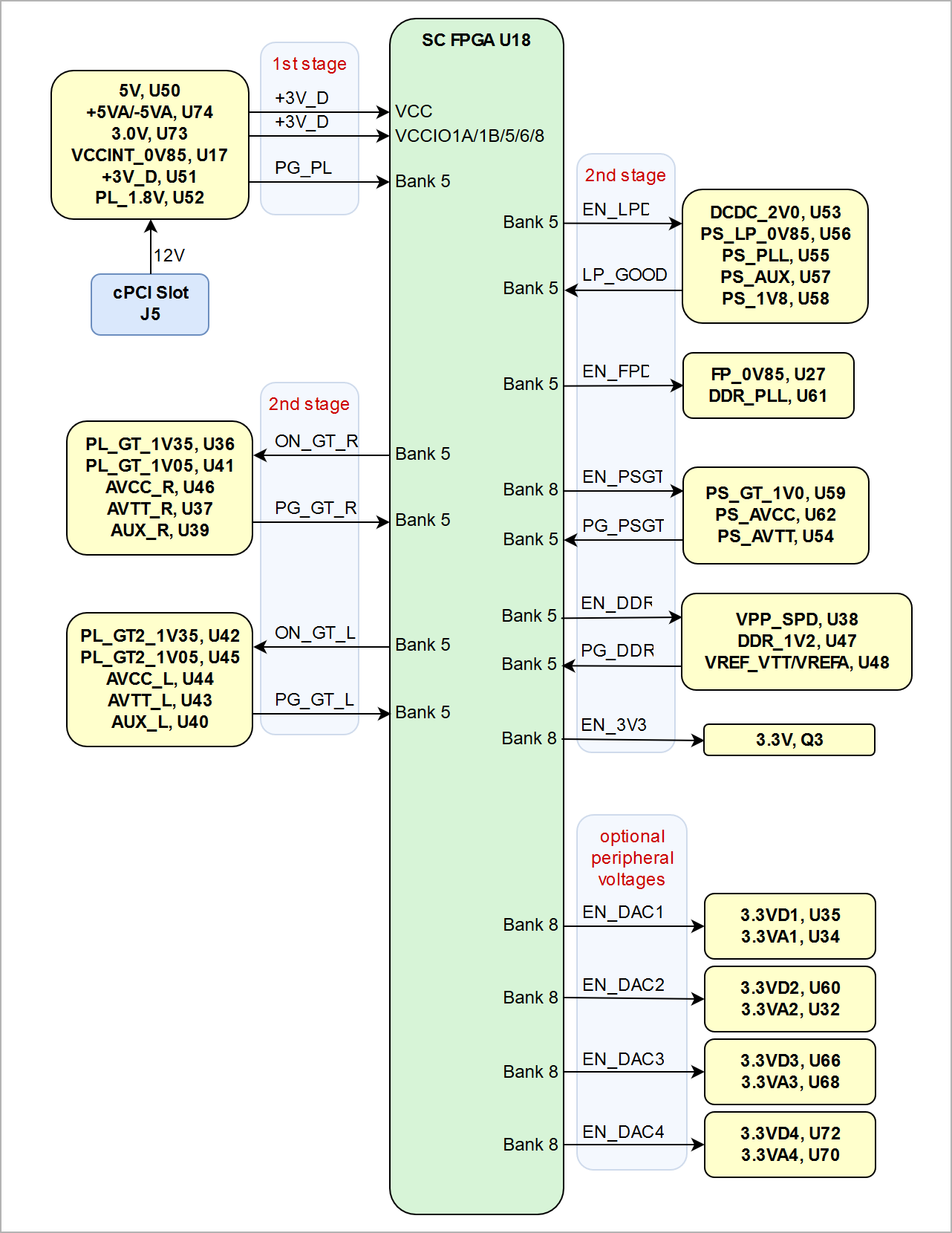

Power-On Sequence

The TEC0850 board meets the recommended criteria to power up the Xilinx Zynq UltraScale+ MPSoC properly by keeping a specific sequence of enabling the on-board DC-DC converters dedicated to the particular Power Domains and powering up the on-board voltages.

On the TEB0911 UltraRack board following Power Domains will be powered up in a certain sequence with by enable and power-good signals of the DC-DC converters, which are controlled by the System Controller FPGA U18:

- Low-Power Domain (LPD)

- Programmable Logic (PL) and Full-Power Domain (FPD)

- GTH, PS GTR transceiver and DDR memory

Hence, those three power instances will be powered up consecutively when the Power-Good signals of the previous instance is asserted.

Following diagram describes the sequence of enabling the three power instances utilizing the DC-DC converter control signals (Enable, Power-Good), which will power-up in descending order as listed in the blocks of the diagram.

...

| anchor | Figure_4 |

|---|

| title | Figure 4: Power-On Sequence Diagram |

|---|

...

| Scroll Only |

|---|

Image Removed Image Removed

|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Following table gives an overview about the I/O signals of the DDR4 SDRAM memory interface:

| Connector | DDR4 SDRAM I/O Signal | Signal Schematic Name | Connected to | Notes |

|---|

DDR4 SO-DIMM Socket U3 | Address inputs | | PS DDR Bank 504 | - | Bank address inputs

| | - | | Bank group inputs | | - | | Differential clocks | - DDR4-CLK0_P

- DDR4-CLK0_N

- DDR4-CLK1_P

- DDR4-CLK1_N

| 2 x DDR4 clock | | Data input/output | | - | | Check bit input/output | | - | | Data strobe (differential) | - DDR4-DQS0_P

- DDR4-DQS0_N

- ...

- DDR4-DQS8_P

- DDR4-DQS8_N

| - | | Data mask and data bus inversion | | - | | Serial address inputs | | address range configuration on I²C bus | | Control Signals | | chip selest signal | | On-die termination enable | | nRESET | | Command and address parity input | | Clock enable | | CRC error flag | | Activation command input | | Temperature event | | I²C | | not connected | - |

|

Circular Push Pull Connector

| Warning |

|---|

| To avoid any damage to the MPSoC module, check for stabilized on-board voltages in steady state before powering up the MPSoC's I/O bank voltages VCCOx. All I/Os should be tri-stated during power-on sequence. |

It is important that all PS and PL I/Os are tri-stated at power-on until the "Power Good"-signals are high, meaning that all on-board voltages have become stable and module is properly powered up.

See Xilinx datasheet DS925 for additional information.

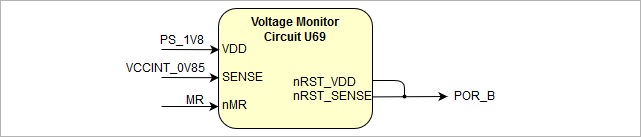

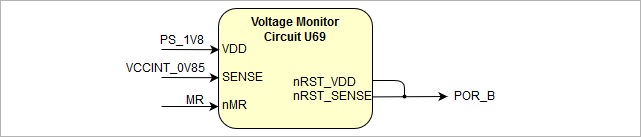

Voltage Monitor Circuit

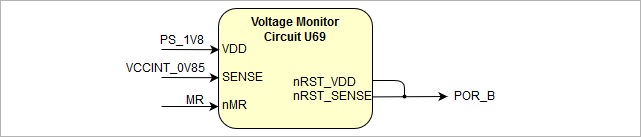

The voltages PS_1V8 and VCCINT_0V85 are monitored by the voltage monitor circuit U69, which generates the POR_B reset signal at power-on. A manual reset is also possible by driving the low active MR-pin connected to MAX10 FPGA U18 (bank5, pin K10) to GND.

| Scroll Title |

|---|

| anchor | Figure_411 |

|---|

| title | Figure 4: Power-On Sequence Diagram11: CAN interface |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | falsetrue |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false | diagramDisplayName |

|---|

| lbox | true |

|---|

| revision | 1 |

|---|

| diagramName | TEC0850 Voltage Monitor CircuitDACs |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| linksdiagramWidth | auto595 |

|---|

| tbstyle | hidden |

|---|

| revision | 1 | diagramWidth | 642 |

|---|

|

|

| Scroll Only |

|---|

Image Removed Image Removed

|

|

...

3-Pin PicoBlade Connector

Battery holder

4-Wire PWM FAN Connectors

| Scroll Title |

|---|

| anchor | TableFigure_x13 |

|---|

| title | Table x: Module absolute maximum ratings.Figure 13: 4-wire PWM FAN connectors |

|---|

|

| tablelayoutorientationportraitsortDirectionASCrepeatTableHeadersdefaultstyle | widths |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

| Connector / Pin | Voltage | Direction | Notes |

|---|

| J1, pin A1, D1, E1, G1, H1, J1, K1 | VIN_12V | Input | Main power supply pins |

| J17, pin 2 | 12V | Output | 4-wire PWM fan connector supply voltage |

| J13, pin 4 | +3V_D | Output | JTAG/UART reference VCCIO voltage |

| B1, pin + | VBATT | Input | 3.0V CR1220 battery |

| J16, pin 2 | 5V | Output | I/O header VCCIO |

| J16, pin 1 | 3.3V | Output | I/O header VCCIO |

| J9, pin 4 | VBUS | Input | USB2 VBUS (5.0V nominal) |

| J10, pin A4, B9 | VBUS30 | Input | USB3 VBUS (5.0V nominal) |

| J11, pin 4 | 3.3V | Output | MicroSD Card VDD |

| J15, pin 2 | DAC1_OUT | Output | DAC output |

| J15, pin 3 | DAC2_OUT | Output | DAC output |

| J15, pin 4 | DAC3_OUT | Output | DAC output |

| J15, pin 5 | DAC4_OUT | Output | DAC output |

...

| diagramName | TEC0850 4-Wire PWM Connector |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| diagramWidth | 641 |

|---|

| revision | 2 |

|---|

|

|

|

On-board Peripherals

| Page properties |

|---|

|

Notes : - add subsection for every component which is important for design, for example:

- Ethernet PHY

- USB PHY

- Programmable Clock Generator

- Oscillators

- eMMCs

- RTC

- FTDI

- ...

- DIP-Switches

- Buttons

- LEDs

|

Subsections...

Zynq UltraScale XCZU15EG MPSoC

The TEC0850 board is populated with the Zynq UltraScale+ XCZU15EG-1FFVB1156E MPSoC.

Main IO interfaces are shown on the image below.

PS MIO Configuration

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Default MIO Configuration |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| MIO | Interface |

|---|

| MIO 0...12 | QSPI Flash Memory | | MIO 20...21 | I2C 1 | | MIO 22...23 | UART 0 | | MIO 26...37 | GEM 0 | | MIO 46...51 | SD 1 | | MIO 52...63 | USB 0 | | MIO 64...75 | USB 1 | | MIO 76...77 | MDIO 0 |

|

MAX10 System Controller

System controller chip is Intel MAX10 10M08SAU169C8G Chip with board control firmware.

Programmable Clock Generators

| Scroll Title |

|---|

| anchor | TableFigure_x2 |

|---|

| title | Table x: Module absolute maximum ratings.Figure 2: TEF1001-02 main components |

|---|

|

| tablelayoutorientationportraitsortDirectionASCrepeatTableHeadersdefaultstylewidths |

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

| Zynq MPSoC Bank | Type | Schematic Name | Voltage | Voltage Range |

|---|

| 44 | HD | 3.3V | 3.3V | fixed to 3.3V |

| 47 | HD | 3.3V | 3.3V | fixed to 3.3V |

| 48 | HD | 3.3V | 3.3V | fixed to 3.3V |

| 49 | HD | 3.3V | 3.3V | fixed to 3.3V |

| 50 | HD | 3.3V | 3.3V | fixed to 3.3V |

| 64 | HP | PL_1V8 | 1.8V | fixed to 1.8V |

| 65 | HP | PL_1V8 | 1.8V | fixed to 1.8V |

| 66 | HP | PL_1V8 | 1.8V | fixed to 1.8V |

| 67 | HP | PL_1V8 | 1.8V | fixed to 1.8V |

| 500 | MIO | PS_1V8 | 1.8V | fixed to 1.8V |

| 501 | MIO | PS_1V8 | 1.8V | fixed to 1.8V |

| 502 | MIO | PS_1V8 | 1.8V | fixed to 1.8V |

| 503 | CONFIG | PS_1V8 | 1.8V | fixed to 1.8V |

| 504 | PSDDR | DDR_1V2

DDR_PLL | 1.2V

1.8V | fixed bank voltages |

128 129 130 | GTH | AVCC_L AUX_L AVTT_L | 0.9V 1.8V 1.2V | fixed bank voltages |

228 229 230 | GTH | AVCC_R AUX_R AVTT_R | 0.9V 1.8V 1.2V | fixed bank voltages |

| MAX10 FPGA Bank | Type | Schematic Name | Voltage | Voltage Range |

|---|

| 1A | - | +3V_D | 3.3V | fixed to 3.3V |

| 1B | - | +3V_D | 3.3V | fixed to 3.3V |

| 2 | - | PS_1V8 | 1.8V | fixed to 1.8V |

| 3 | - | 3.3V | 3.3V | fixed to 3.3V |

| 5 | - | +3V_D | 3.3V | fixed to 3.3V |

| 6 | - | +3V_D | 3.3V | fixed to 3.3V |

| 8 | - | +3V_D | 3.3V | fixed to 3.3V |

Technical Specifications

Absolute Maximum Ratings

| | lbox | true |

|---|

| revision | 3 |

|---|

| diagramName | Clocks Diagram |

|---|

| simpleViewer | true |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | top |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

Image Added Image Added

|

|

I2C

The onboard I2C bus is connected to MIO 20...21 pins. Devices on the bus shown in the table below.

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: SI5345 I2C address |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| I2C address | Chip | Description |

|---|

| 0x69 | U14 Si5345 | Clock generator and distributor |

|

Oscillators

FTDIs

FT2232H

FT601Q-B-T

Quad-SPI Flash Memory

Board has two N25Q512A11G1240E connected in a dual parallel mode.

EEPROMs

I2C

The onboard I2C bus is connected to MIO 20...21 pins. Devices on the bus shown in the table below.

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: EEPROMs I2C Addresses |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| I2C address | Chip | Description |

|---|

| 0x50 | U63 24AA128T-I/ST | 128K Serial EEPROM | | 0x53 | U64 24AA025E48T-I/OT | 2K Serial EEPROM with EUI-48™ or EUI-64™ Node Identity |

|

USB PHY

Gigabit Ethernet PHY

Board has Marvell Alaska 88E1512 Ethernet PHY which use MDIO address 1.

8Bit DACs

Board has 4 8-bit parallel Texas Instruments THS5641 DACs with up to 100 MSPS Update Rate.

DIP-Switches

S1

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Switch | Description |

|---|

| 1 | Boot Mode 0 | | 2 | Boot Mode 1 | | 3 | Boot Mode 2 | | 4 | Boot Mode 3 |

|

See Zynq UltraScale+ Device Technical Reference Manual page 236 for full boot modes description. Most common modes are

| Scroll Title |

|---|

|

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Module absolute maximum ratings.Recommended Boot Modes |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

Parameter | Min | Max | Unit | Reference Document | Notes |

|---|

| VIN_12V | -0.3 | 16 | V | Intel Enpirion EM2130 data sheet / Fuse F1 | Fuse F1 @16V/2.5A |

| VBATT | -0.3 | 6 | V | TPS780180300 data sheet | 1.8V typical output |

| VCCO for HD I/O banks | -0.5 | 3.4 | V | Xilinx document DS925 | - |

| VCCO for HP I/O banks | -0.5 | 2 | V | Xilinx document DS925 | - |

| I/O input voltage for HD I/O banks | -0.55 | VCCO + 0.55 | V | Xilinx document DS925 | - |

| I/O input voltage for HP I/O banks | -0.55 | VCCO + 0.55 | V | Xilinx document DS925 | - |

| PS I/O input voltage (MIO pins) | -0.5 | VCCO_PSIO + 0.55 | V | Xilinx document DS925 | VCCO_PSIO 1.8V nominally |

| PS GTR reference clocks absolute input voltage | -0.5 | 1.1 | V | Xilinx document DS925 | - |

| PS GTR absolute input voltage | -0.5 | 1.1 | V | Xilinx document DS925 | - |

| MGT clock absolute input voltage | -0.5 | 1.3 | V | Xilinx document DS925 | - |

MGT Receiver (RXP/RXN) and transmitter

(TXP/TXN) absolute input voltage | -0.5 | 1.2 | V | Xilinx document DS925 | - |

SC FPGA U18 I/O input voltage

| -0.5 | VCC + 0.5 | V | Intel MAX 10 data sheet | VCC 3.3V nominally |

Voltage on input I/O pins of DC-DC U17 EM2130

on header J12 | -0.3 | 3.6 | V | Intel Enpirion EM2130 data sheet | - |

Storage temperature (ambient) | -40 | 85 | °C | ASVTX-12 data sheet | - |

Recommended Operating Conditions

| Boot Mode | SW1:4 | SW1:3 | SW1:2 | SW1:1 |

|---|

| JTAG Boot Mode | ON | ON | ON | ON | | Quad-SPI | ON | ON | ON | OFF | | SD Card | ON | ON | OFF | OFF |

|

S2

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: S2 DIP Switch |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Switch | Description |

|---|

| 1 | SC JTAGEN | | 2 | EEPROM WP (Write protect) | | 3 | FPGA PUDC | | 4 | SC Switch (Reserved for future use) |

|

Buttons

LEDs

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: LEDs |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| LED | Signal | Chip | Pin | Description |

|---|

| Front panel LED 1 (Red) | LED_FP_1 | FPGA U1 | AF15 | PL User defined LED | | Front panel LED 2 (Green) | LED_FP_2 | FPGA U1 | AG15 | PL User defined LED | | Front panel LED 3 (Green) | LED_FP_3 | FPGA U1 | AE15 | PL User defined LED | | Front panel LED 4 (Green) | LED_FP_4 | SC U18 | M4 | Power Good |

|

Power and Power-On Sequence

Power Consumption

The maximum power consumption of a module mainly depends on the design running on the FPGA.

Xilinx provide a power estimator excel sheets to calculate power consumption. It's also possible to evaluate the power consumption of the developed design with Vivado. See also Trenz Electronic Wiki FAQ.

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Typical power consumption |

|---|

|

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Module absolute maximum ratings. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Power Input | Typical Current |

|---|

| Parameter | Min | Max | Unit | Reference Document | Notes |

|---|

| VIN_12V | 12 | 14 | V | Intel Enpirion EM2130 data sheet | 12V nominally input voltage, min. current 6.65A | | VBATT | 2.2 | 5.5 | V | TPS780180300 data sheet | supplied by 3.0V CR1220 battery | | VCCO for HD I/O banks | 1.14 | 3.4 | V | Xilinx document DS925 | - | | VCCO for HP I/O banks | 0.95 | 1.9 | V | Xilinx document DS925 | - | | I/O input voltage for HD I/O banks | -0.2 | VCCO + 0.2 | V | Xilinx document DS925 | - | | I/O input voltage for HP I/O banks | -0.2 | VCCO + 0.2 | V | Xilinx document DS925 | - | | PS I/O input voltage (MIO pins) | -0.2 | VCCO_PSIO + 0.2 | V | Xilinx document DS925 | VCCO_PSIO 1.8V nominally | | SC FPGA U18 I/O input voltage | 0 | VCC | V | Intel MAX 10 data sheet | VCC 3.3V nominally | | Board Operating Temperature Range 1), 2) | 0 | 85 | °C | Xilinx document DS925 | extended grade Zynq MPSoC temperarure range |

|

1) Temperature range may vary depending on assembly options

2) The operating temperature range of the Zynq MPSoC, SC FPGA SoC and on-board peripherals are junction and also ambient operating temperature ranges

Physical Dimensions

...

| anchor | Figure_x |

|---|

| title | Figure x: Physical dimensions drawing |

|---|

Variants Currently In Production

...

| anchor | Table_x |

|---|

| title | Table x: Shop Overview |

|---|

...

Revision History

Hardware Revision History

...

| anchor | Table_x |

|---|

| title | Table x: Module absolute maximum ratings. |

|---|

...

Notes

...

02

...

current available board revision

...

Document Change History

| Page properties |

|---|

|

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

...

| anchor | Table_x |

|---|

| title | Table x: Document change history. |

|---|

...

Contributor

...

| Page info |

|---|

| infoType | Current version |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

|

...

| Page info |

|---|

| infoType | Modified by |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

...

...

| Page info |

|---|

| infoType | Modified users |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

...

Disclaimer

...

J8

(FMC C)

...

- B230_RX3_P

- B230_RX3_N

- B230_TX3_P

- B230_TX3_N

...

J8-C6

J8-C7

J8-C2

J8-C3

...

MGTHRXP3_230, A4

MGTHRXN3_230, A3

MGTHTXP3_230, A8

MGTHTXN3_230, A7

...

- B230_RX2_P

- B230_RX2_N

- B230_TX2_P

- B230_TX2_N

...

J8-A2

J8-A3

J8-A22

J8-A23

...

MGTHRXP2_230, B2

MGTHRXN2_230, B1

MGTHTXP2_230, B6

MGTHTXN2_230, B5

...

- B230_RX1_P

- B230_RX1_N

- B230_TX1_P

- B230_TX1_N

...

J8-A6

J8-A7

J8-A26

J8-A27

...

MGTHRXP1_230, C4

MGTHRXN1_230, C3

MGTHTXP1_230, D6

MGTHTXN1_230, D5

Power supply with minimum current capability of 6.65A for system startup is recommended.

The TEC0850 board is equipped with the Xilinx Zynq UltraScale+ MPSoC delivers a heterogeneous multi-processing system with integrated programmable logic and independently operable elements and is designed to meet embedded system power management requirement by advanced power management features. This features allow to offset the power and heat constraints against overall performance and operational efficiency.

This features allowing highly flexible power management are achieved by establishing Power Domains for power isolation. The Zynq UltraScale+ MPSoC has multiple power domains, whereby each power domain requires its own particular on-board DC-DC converters.

The Processing System contains three Power Domains:

- Battery Power Domain (BBRAM and RTC)

- Full-Power Domain (Application Processing Unit, DDR Controller, Graphics Processing Unit and High-Speed Connectivity)

- Low-Power Domain (Real-Time Processing Unit, Security and Configuration Unit, Platform Management Unit, System Monitor and General Connectivity)

- Programmable Logic (PL)

Power Distribution Dependencies

There are following dependencies how the initial 24V voltage from the main power pins on cPCI slot J1 is distributed to the on-board DC-DC converters, which power up further DC-DC converters and the particular on-board voltages:

| Scroll Title |

|---|

| anchor | Figure_3 |

|---|

| title | Figure 3: Power Distribution |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 16 |

|---|

| diagramName | Power supply |

|---|

| simpleViewer | true |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

Image Added Image Added

|

|

Power-On Sequence

The TEC0850 board meets the recommended criteria to power up the Xilinx Zynq UltraScale+ MPSoC properly by keeping a specific sequence of enabling the on-board DC-DC converters dedicated to the particular Power Domains and powering up the on-board voltages.

On the TEB0911 UltraRack board following Power Domains will be powered up in a certain sequence with by enable and power-good signals of the DC-DC converters, which are controlled by the System Controller FPGA U18:

- Low-Power Domain (LPD)

- Programmable Logic (PL) and Full-Power Domain (FPD)

- GTH, PS GTR transceiver and DDR memory

Hence, those three power instances will be powered up consecutively when the Power-Good signals of the previous instance is asserted.

Following diagram describes the sequence of enabling the three power instances utilizing the DC-DC converter control signals (Enable, Power-Good), which will power-up in descending order as listed in the blocks of the diagram.

| Scroll Title |

|---|

| anchor | Figure_4 |

|---|

| title | Figure 4: Power-On Sequence Diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 2 |

|---|

| diagramName | TEC0850 Power-On Sequence Diagram |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 641 |

|---|

|

|

| Scroll Only |

|---|

Image Added Image Added

|

|

| Warning |

|---|

| To avoid any damage to the MPSoC module, check for stabilized on-board voltages in steady state before powering up the MPSoC's I/O bank voltages VCCOx. All I/Os should be tri-stated during power-on sequence. |

It is important that all PS and PL I/Os are tri-stated at power-on until the "Power Good"-signals are high, meaning that all on-board voltages have become stable and module is properly powered up.

See Xilinx datasheet DS925 for additional information.

Voltage Monitor Circuit

The voltages PS_1V8 and VCCINT_0V85 are monitored by the voltage monitor circuit U69, which generates the POR_B reset signal at power-on. A manual reset is also possible by driving the low active MR-pin connected to MAX10 FPGA U18 (bank5, pin K10) to GND.

| Scroll Title |

|---|

| anchor | Figure_4 |

|---|

| title | Figure 4: Power-On Sequence Diagram |

|---|

|

| Scroll Ignore |

|---|

| draw.io Diagram |

|---|

| border | false |

|---|

| viewerToolbar | true |

|---|

| |

|---|

| fitWindow | false |

|---|

| diagramDisplayName | |

|---|

| lbox | true |

|---|

| revision | 1 |

|---|

| diagramName | TEC0850 Voltage Monitor Circuit |

|---|

| simpleViewer | false |

|---|

| width | |

|---|

| links | auto |

|---|

| tbstyle | hidden |

|---|

| diagramWidth | 642 |

|---|

|

|

| Scroll Only |

|---|

Image Added Image Added

|

|

Power Rails

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Module absolute maximum ratings. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Connector / Pin | Voltage | Direction | Notes |

|---|

| J1, pin A1, D1, E1, G1, H1, J1, K1 | VIN_12V | Input | Main power supply pins | | J17, pin 2 | 12V | Output | 4-wire PWM fan connector supply voltage | | J13, pin 4 | +3V_D | Output | JTAG/UART reference VCCIO voltage | | B1, pin + | VBATT | Input | 3.0V CR1220 battery | | J16, pin 2 | 5V | Output | I/O header VCCIO | | J16, pin 1 | 3.3V | Output | I/O header VCCIO | | J9, pin 4 | VBUS | Input | USB2 VBUS (5.0V nominal) | | J10, pin A4, B9 | VBUS30 | Input | USB3 VBUS (5.0V nominal) | | J11, pin 4 | 3.3V | Output | MicroSD Card VDD | | J15, pin 2 | DAC1_OUT | Output | DAC output | | J15, pin 3 | DAC2_OUT | Output | DAC output | | J15, pin 4 | DAC3_OUT | Output | DAC output | | J15, pin 5 | DAC4_OUT | Output | DAC output |

|

Bank Voltages

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Module absolute maximum ratings. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Zynq MPSoC Bank | Type | Schematic Name | Voltage | Voltage Range |

|---|

| 44 | HD | 3.3V | 3.3V | fixed to 3.3V | | 47 | HD | 3.3V | 3.3V | fixed to 3.3V | | 48 | HD | 3.3V | 3.3V | fixed to 3.3V | | 49 | HD | 3.3V | 3.3V | fixed to 3.3V | | 50 | HD | 3.3V | 3.3V | fixed to 3.3V | | 64 | HP | PL_1V8 | 1.8V | fixed to 1.8V | | 65 | HP | PL_1V8 | 1.8V | fixed to 1.8V | | 66 | HP | PL_1V8 | 1.8V | fixed to 1.8V | | 67 | HP | PL_1V8 | 1.8V | fixed to 1.8V | | 500 | MIO | PS_1V8 | 1.8V | fixed to 1.8V | | 501 | MIO | PS_1V8 | 1.8V | fixed to 1.8V | | 502 | MIO | PS_1V8 | 1.8V | fixed to 1.8V | | 503 | CONFIG | PS_1V8 | 1.8V | fixed to 1.8V | | 504 | PSDDR | DDR_1V2

DDR_PLL | 1.2V

1.8V | fixed bank voltages | 128 129 130 | GTH | AVCC_L AUX_L AVTT_L | 0.9V 1.8V 1.2V | fixed bank voltages | 228 229 230 | GTH | AVCC_R AUX_R AVTT_R | 0.9V 1.8V 1.2V | fixed bank voltages | | MAX10 FPGA Bank | Type | Schematic Name | Voltage | Voltage Range |

|---|

| 1A | - | +3V_D | 3.3V | fixed to 3.3V | | 1B | - | +3V_D | 3.3V | fixed to 3.3V | | 2 | - | PS_1V8 | 1.8V | fixed to 1.8V | | 3 | - | 3.3V | 3.3V | fixed to 3.3V | | 5 | - | +3V_D | 3.3V | fixed to 3.3V | | 6 | - | +3V_D | 3.3V | fixed to 3.3V | | 8 | - | +3V_D | 3.3V | fixed to 3.3V |

|

Technical Specifications

Absolute Maximum Ratings

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Module absolute maximum ratings. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

Parameter | Min | Max | Unit | Reference Document | Notes |

|---|

| VIN_12V | -0.3 | 16 | V | Intel Enpirion EM2130 data sheet / Fuse F1 | Fuse F1 @16V/2.5A | | VBATT | -0.3 | 6 | V | TPS780180300 data sheet | 1.8V typical output | | VCCO for HD I/O banks | -0.5 | 3.4 | V | Xilinx document DS925 | - | | VCCO for HP I/O banks | -0.5 | 2 | V | Xilinx document DS925 | - | | I/O input voltage for HD I/O banks | -0.55 | VCCO + 0.55 | V | Xilinx document DS925 | - | | I/O input voltage for HP I/O banks | -0.55 | VCCO + 0.55 | V | Xilinx document DS925 | - | | PS I/O input voltage (MIO pins) | -0.5 | VCCO_PSIO + 0.55 | V | Xilinx document DS925 | VCCO_PSIO 1.8V nominally | | PS GTR reference clocks absolute input voltage | -0.5 | 1.1 | V | Xilinx document DS925 | - | | PS GTR absolute input voltage | -0.5 | 1.1 | V | Xilinx document DS925 | - | | MGT clock absolute input voltage | -0.5 | 1.3 | V | Xilinx document DS925 | - | MGT Receiver (RXP/RXN) and transmitter

(TXP/TXN) absolute input voltage | -0.5 | 1.2 | V | Xilinx document DS925 | - | SC FPGA U18 I/O input voltage

| -0.5 | VCC + 0.5 | V | Intel MAX 10 data sheet | VCC 3.3V nominally | Voltage on input I/O pins of DC-DC U17 EM2130

on header J12 | -0.3 | 3.6 | V | Intel Enpirion EM2130 data sheet | - | Storage temperature (ambient) | -40 | 85 | °C | ASVTX-12 data sheet | - |

|

Recommended Operating Conditions

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Module absolute maximum ratings. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Parameter | Min | Max | Unit | Reference Document | Notes |

|---|

| VIN_12V | 12 | 14 | V | Intel Enpirion EM2130 data sheet | 12V nominally input voltage, min. current 6.65A | | VBATT | 2.2 | 5.5 | V | TPS780180300 data sheet | supplied by 3.0V CR1220 battery | | VCCO for HD I/O banks | 1.14 | 3.4 | V | Xilinx document DS925 | - | | VCCO for HP I/O banks | 0.95 | 1.9 | V | Xilinx document DS925 | - | | I/O input voltage for HD I/O banks | -0.2 | VCCO + 0.2 | V | Xilinx document DS925 | - | | I/O input voltage for HP I/O banks | -0.2 | VCCO + 0.2 | V | Xilinx document DS925 | - | | PS I/O input voltage (MIO pins) | -0.2 | VCCO_PSIO + 0.2 | V | Xilinx document DS925 | VCCO_PSIO 1.8V nominally | | SC FPGA U18 I/O input voltage | 0 | VCC | V | Intel MAX 10 data sheet | VCC 3.3V nominally | | Board Operating Temperature Range 1), 2) | 0 | 85 | °C | Xilinx document DS925 | extended grade Zynq MPSoC temperarure range |

|

1) Temperature range may vary depending on assembly options

2) The operating temperature range of the Zynq MPSoC, SC FPGA SoC and on-board peripherals are junction and also ambient operating temperature ranges

Physical Dimensions

| Scroll Title |

|---|

| anchor | Figure_x |

|---|

| title | Figure x: Physical dimensions drawing |

|---|

|

|

Variants Currently In Production

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Shop Overview |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

|

Revision History

Hardware Revision History

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Module absolute maximum ratings. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Notes | PCN | Documentation Link |

|---|

| - | 02 | current available board revision | - | TEC0850-02 | | - | 01 | Prototypes | - | - |

|

Document Change History

| Page properties |

|---|

|

- Note this list must be only updated, if the document is online on public doc!

- It's semi automatically, so do following

Add new row below first Copy "Page Information Macro(date)" Macro-Preview, Metadata Version number, Author Name and description to the empty row. Important Revision number must be the same as the Wiki document revision number Update Metadata = "Page Information Macro (current-version)" Preview+1 and add Author and change description. --> this point is will be deleted on newer pdf export template - Metadata is only used of compatibility of older exports

|

| Scroll Title |

|---|

| anchor | Table_x |

|---|

| title | Table x: Document change history. |

|---|

|

| Scroll Table Layout |

|---|

| orientation | portrait |

|---|

| sortDirection | ASC |

|---|

| repeatTableHeaders | default |

|---|

| style | |

|---|

| widths | |

|---|

| sortByColumn | 1 |

|---|

| sortEnabled | false |

|---|

| cellHighlighting | true |

|---|

|

| Date | Revision | Contributor | Description |

|---|

| Page info |

|---|

| modified-date |

|---|

| modified-date |

|---|

| dateFormat | yyyy-MM-dd |

|---|

|

| | Page info |

|---|

| infoType | Current version |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| prefix | v. |

|---|

| type | Flat |

|---|

|

| | Page info |

|---|

| infoType | Modified by |

|---|

| dateFormat | yyyy-MM-dd |

|---|

| type | Flat |

|---|

|

| |

|

Disclaimer

| Include Page |

|---|

| IN:Legal Notices |

|---|

| IN:Legal Notices |

|---|

|

...

- B230_RX0_P

- B230_RX0_N

- B230_TX0_P

- B230_TX0_N

...

J8-A10

J8-A11

J8-A30

J8-A31

...